1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах, построенных на основе больших интегральных схем.

Известно устройство для возведения в степень, содержащее регистры операнда и результата, вспомогательный регистр, (V-1) регнстров промежуточных результатов {N - показатель степени), (Л-1) сумматоров, блок местного управления и логические схемы «И, объединенные в Л груии.

В нредлагаемом устройстве для упрош,ения выходы регистра онеранда соединены с первыми входами схем «И всех групн, вторые входы первой группы схем «И соединены с выходом блока местного управления, а выходы первой группы схем «И соединены с входами вспомогательного регистра, выход младшего разряда которого соединен со вторыми входами второй группы схем «И, выходы второй Л-ой групп схем «И соединены с входами первого-(;V-1)-го сумматоров, выходы этих сумматоров соединены с входами первого- (.V-1)-го регистров нромежуточиых результатов, выходы этих регистров соединены с входами первого (Л-1)-го сумматоров, выход младшего разряда г-го регистра промежуточных результатов соедииен со вторыми входами (1-|-2)-ой груниь схем «И, выход младшего разряда ()-го регнстра промежуточных результатов соединен с входом регистра результата, третьи входы второй jV-ой групп схем «И соединены с блоком местного управления, з правляюш,ие входы регистров про.лтежуточных результатов, всномогательного регистра, регистра результата соединены с блоком местного управления.

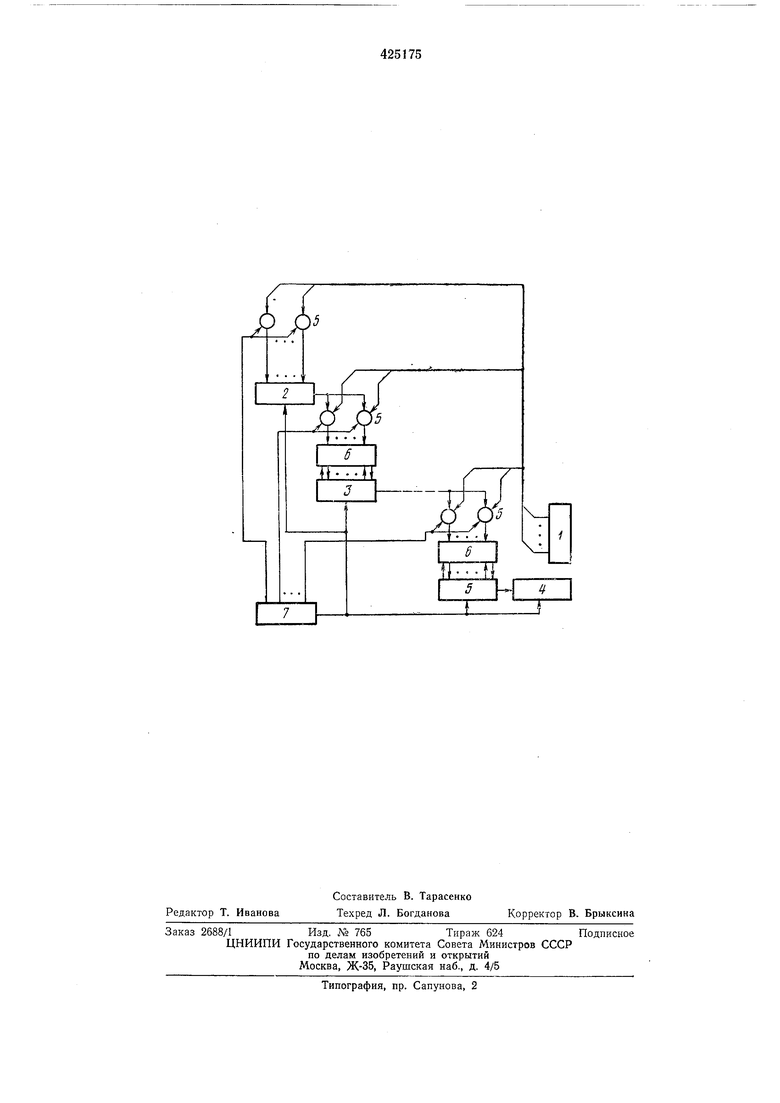

На чертеже изображена блок-схема предлагаемого устройства.

Устройство состоит из регистра 1 операнда А , вспомогательного регистра 2 этого же операнда, (Л-I) регнстров 3 промежуточных результатов н регистра 4 результата. Выходы регнстра 1 через грунпу 3 схем «И нодключены к входам вспомогательного регистра 2, а также к первым входам (Л--1) сумматоров 6. Вторые входы всех (/V-1) сумматоров 6 и их выходы соединены соответственно с выходами н входами (Л-1) periiCTpoB 3 промежуточных результатов. Выход младшего разряда i-ro регнстра нромежуточиых результатов соединен со вторыми входами (i-{-2)-on грунпы схем «И. Третьи входы всех групп схем «И связаны с выходами блока 7 местного управления. Выход младшего разряда вспомогательиого регистра 2 подведен ко вторым входам первой группы 5 схем «I-I. а такой же выход (.V-1)-го регистра промежуточных результатов соединен с входом регистра 4 результата. Входы цепей сдвига регистров 2, 3 и 4 соединены с выходом блока 7. Все регистры 3 промежуточных результатов имеют по (rt+l) разрядов, где п - число разрядов операнда Х.. Регистр 2 при этом имеет п разрядов, а регистр 4 - не менее (Л-1)« разрядов. Устройство работает следуюндим образом. В исходном состоянии операнд X находится в регистре 1, а в регистрах 2, 3 и 4 записаны нули. С началом работы устройства блок 7 открывает группу 5 схем «И, подключенную к входам вспомогательного регистра 2. Вследствие этого в регистр 2 записывается код операнда X, младший разряд которого но сигналу из блока 7 управляет слон ением кода операнда X, поступающего из регистра 1, с содержимым регистра первого промежуточного результата. Затем блок 7 открывает схемы 5, подключенные к выходу младшего разряда регистра первого промежуточного результата. Вследствие этого младший разряд полученной ранее суммы управляет сложением операнда X с содержимым регистра второго промежуточного результата и т. д. После окончания сложения X с содержимым всех () регистров промежуточных результатов следует сдвиг содержимого регистров 2, 3 и 4 на один разряд вправо. При этом из регистра (Л-1)-го промежуточного результата в регистр 4 переписывается младшая цифра результата. Далее описанпый выше процесс повторяется (т. е. второй разряд операнда X в регистре 2 управляет сложением X с содержимым регистра первого промежуточного результата и т. д., до тех пор нока не будут сформированы все Nn разрядов результата). С помош,ью предлагаемого устройства можно вычислить и выражения вида Х-, где . Для этого в начале вычислений операнд X необходимо записывать не во вспомогательный регистр 2, а в регистр (.V-1-/)-го промежуточного результата. Кроме того, регистр 4 результата не обязательно должен иметь Nti разрядов, так как старших разрядов результата могут находиться в регистре (:V-1)-го промежуточного результата. Предмет изобретения Устройство для возведения в степень, содержащее регистр операнда, вспомогательный регистр, регистр результата, (N-1) регистров промежуточных результатов (где N - показатель степени), (V-1) сумматор, N групп схем «И, блок местпого управления, отличающееся тем, что, с целью упрощения устройства, выходы регистра операнда соединены с нервыми входами схем «И всех групп, вторые входы нервой группы схем «И соединены с выходом блока местного унравления, а выходы нервой группы схем «И соединены с входами вспомогательного регистра, выход младшего разряда которого соединен со вторыми входами второй грунны схем «И, выходы второй - Л-ой группы схем «И соединены с входами первого - (/V-1)-го сумматоров, выходы этих сумматоров соединены с входами первого- (N-1)-го регистров промежуточных результатов, выходы этих регистров соединены с входами первого-(Л-1)-го сумматоров, выход младшего разряда i-ro регистра промежуточных результатов соединен со вторыми входами (Н-2)-ой группы схем «И, выход младшего разряда (N-1)-го регистра промежуточных результатов соединен с входом регистра результата, третьи входы второй Л/-ой групп схем «П соединены с блоком местного управления, управляюшие входы регистров промежуточных результатов, вспомогательного регистра, регистра результата соединены с блоком местного управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления значений полиномов вида | 1972 |

|

SU451088A1 |

| УСТРОЙСТВО Д.ПЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 1971 |

|

SU300449A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1034033A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

Даты

1974-04-25—Публикация

1972-06-30—Подача