Изобретение относится к области вычислительной техники, а именно к арифметическим устройствам (АУ) цифровой вычислительной машины (ЦВМ) и может найти применение при создании надежных управляющих специализированных ЦВМ.

Известны арифметические устройства, содержащие регистры хранения онерандов, сумматор параллельного действия с цеиью сквозного переноса, схему определения контрольного кода результата действий над операндами, схему формирования (определения) контрольного кода по контрольным кодам операндов, схему сравнения контрольных кодов, запрещающую использоваиие результата в случае несовпадения контрольных кодов. Однако в таких устройствах при неисиравности одного электроэлемента, искажающей результат, выходные сигналы устройства нельзя использовать дальще без отключения схемы, в состав которой входит неисправный элемент.

Описываемое изобретение нозволяет создать надежное арифметическое устройство, позволяющее при иеисправиости одного элемента цепей переноса или суммы получить правильный результат вычислений на том же сумматоре без отключения логической схемы, в состав которой входит иеисправный элемент.

падения на выходах каждого из регистров операндов, причем на первые входы первых схем совпадения подключен инверсный выход схемы сравнения, а на вторые - прямой выход соответствующего регистра операнда, на первые входы вторых схем совпадения подключен прямой выход схемы сравнения, а на вторые - инверсный выход соответствуюн1его регистра операнда, выходы схем совпадеиия подключе ы к входам сумматора, вход схемы формирования единичного сигнала соедннен с выходом схемы сравнения, а выход - с входом сумл атора.

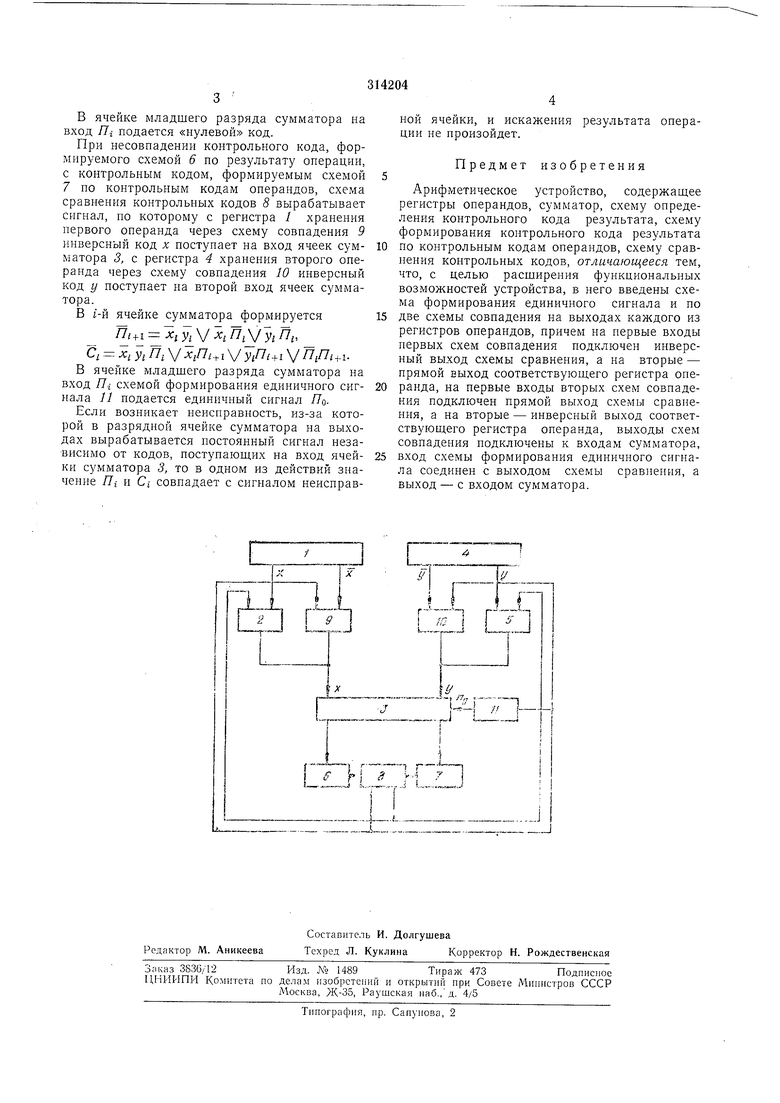

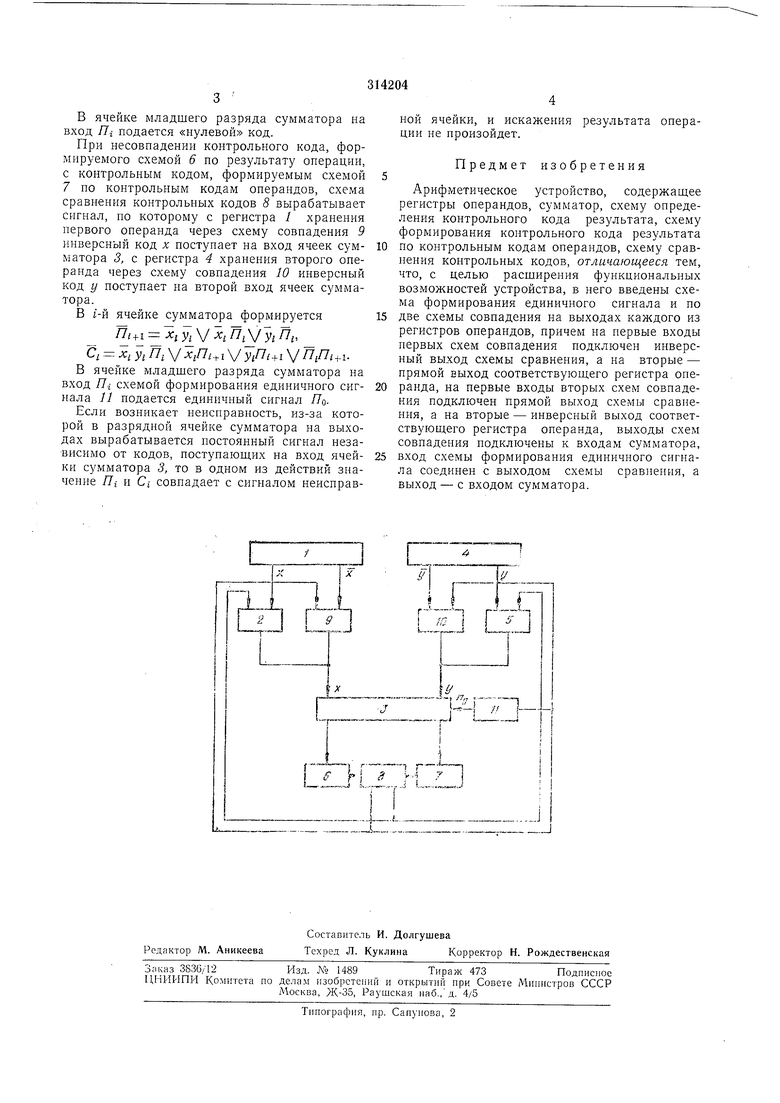

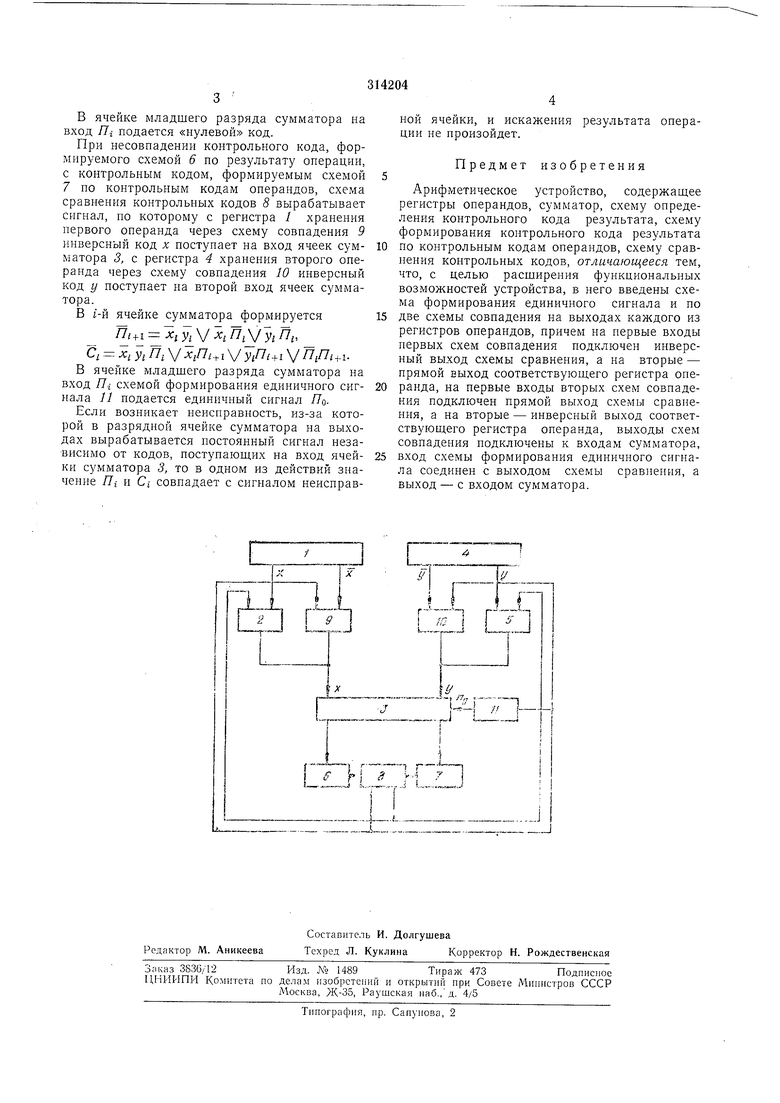

На чертеже прнведена блок-схема арифметического устройства.

Арифметическое устройство работает следующим образом. С регистра 7 хранения перрого операнда л: через схему совпадения 2 код X поступает на вход ячеек сумматора 3. С регистра 4 хранения второго операнда /у через схему совпадения 5 код у поступает иа второй вход ячейки сумматора.

В (-Й ячейке сумматора формируется перепое в i-j-1-й разряд

Я,-.,.,уЛ/ ;ЯеУуА и значение суммы г-го разряда результата

В ячейке младшего разряда сумматора на вход Пг подается «нулевой код.

При несовпадении контрольного кода, формируемого схемой 6 по результату операции, с контрольным кодом, формируемым схемой 7 по контрольным кодам операндов, схема сравнения контрольных кодов 8 вырабатывает сигнал, по которому с регистра / хранения первого операнда через схему совпадения 9 инверсный код х поступает на вход ячеек сумматора 3, с регистра 4 хранения второго операнда через схему совпадения 10 инверсный код у поступает на второй вход ячеек сумматора.

В i-й ячейке сумматора формируется

Яг+1 JC, у; V / Til, Ci Xi У1 /7 V i/7/+i V Д/7/+1.

В ячейке младшего разряда сумматора на вход Пi схемой формирования единичного сигнала // подается единичный сигнал По.

Если возникает неисправность, из-за которой в разрядной ячейке сумматора на выходах вырабатывается постоянный сигнал независимо от кодов, поступаюш,их на вход ячейки сумматора 3, то в одном из действий значение Яг и С; совпадает с сигналом неисправной ячейки, и искажения результата операции не произойдет.

Предмет изобретения

Арифметическое устройство, содержащее регистры операндов, сумматор, схему определения контрольного кода результата, схему формирования контрольного кода результата

по контрольным кодам операндов, схему сравнения контрольных кодов, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены схема формирования единичного сигнала и по

две схемы совпадения на выходах каждого из регистров операндов, причем на первые входы первых схем совпадения подключен инверсный выход схемы сравнения, а на вторые - прямой выход соответствуюш.его регистра онеранда, на первые входы вторых схем совпадения подключен прямой выход схемы сравнения, а на вторые - инверсный выход соответствующего регистра операнда, выходы схем совпадения подключены к входам сумматора,

вход схемы формирования единичного сигнала соединен с выходом схемы сравнения, а выход - с входом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сумматора | 1983 |

|

SU1111167A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО С КОНТРОЛЕМ И КОРРЕКЦИЕЙ ОШИБОК | 1973 |

|

SU387362A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Устройство для обучения | 1987 |

|

SU1580423A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Процессорный элемент | 1980 |

|

SU881757A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

Даты

1971-01-01—Публикация