I

Изобретение относится к области вычислительной техники и может быть использовано при разработке арифметических устройств.

Известно многовходовое суммирующее устройство, содержащее в каждом разряде сумматоры, сгруппированные в линейки. Выходы «сумма каждого сумматора младших линеек соединены с входами сумматоров последующих линеек.

Цель изобретения - повышение быстродействия устройства.

Это достигается тем, что в нем шины всех слагаемых каждого разряда подключены к входам сумматоров первой линейки, а выходы переноса сумматоров младших линеек соединены с одними из входов сумматоров последующих линеек соседнего старшего разряда.

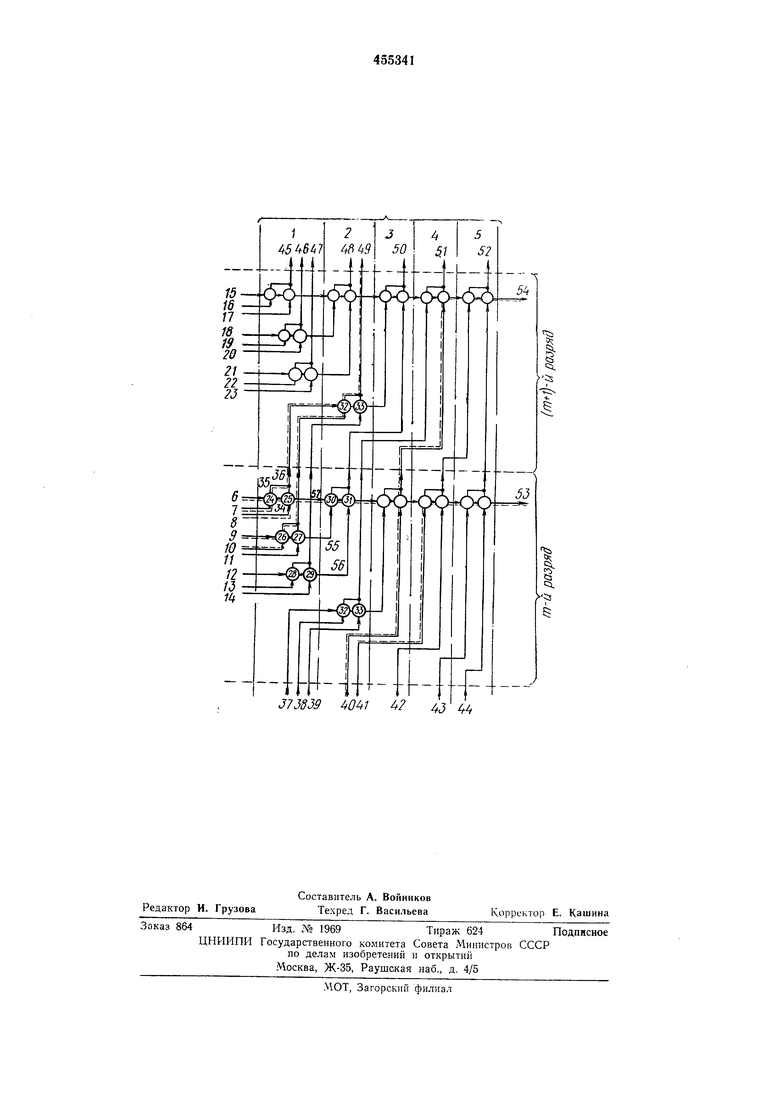

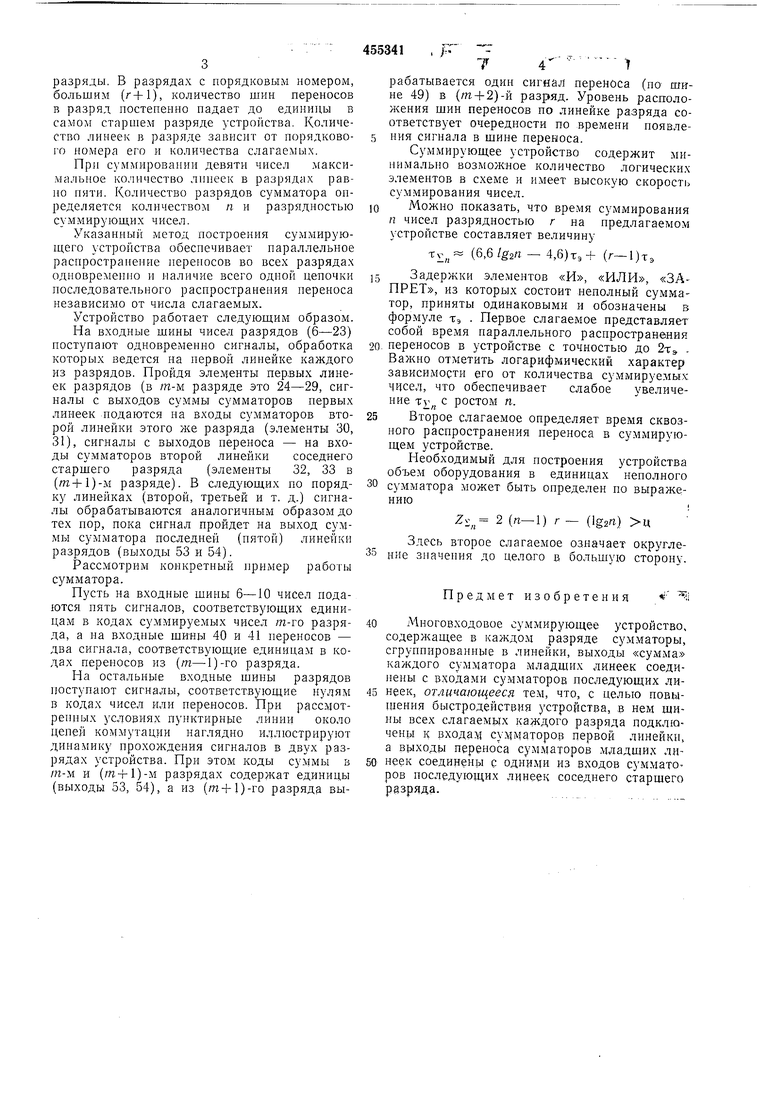

На чертеже приведена схема двух разрядов суммируюшего устройства на девять чисел.

Каждый разряд устройства разбит на линейкн 1-5 (ноказаны штрихпунктирными линиями), на входные шипы 6-23 которых поступают цифры разрядов девяти слагаемых.

В состав первой липейки входят пенолные суМ1маторы 24-29, во вторую - сумматоры 30-33, а остальные трн линейки содержат по два таких сумматора. Каждая пара неполных сумматоров образует полный сумматор

на трп входа, для че1о иыход 34 каждого неполного сумматора 24 соединен с входом сумматора 25, а выходы 35 переноса обоих неполных сумматоров 24 н 25 объединены и образуют один выход 36 переноса. На вхо.л,ы 37-44 младшего разряда суммируюп его устройства подаются сигналы переносов с младп его разряда. С выходов 45-52 снимаются переносы со старшего разряда, с выходов 53 н 54 - значение суммы каждого нз разрядов сумматора.

Выходы 55, 56 и 57 су: 1маторов первой линейки подключены к входам сумматоров 30, 31 второй линейки. Аналогично соединяются выходы су.мматоров каждой линейки разряда суммнрующего устройства.

Число входных шип переносов в разряд определяется количеством суммируемых чисел п и порядковым номером разряда. С ростом порядкового номера разряда, начиная с самого младншго, увелнчпвается количество 1ПП1 переносов в )iero. В процессе этого роста достигается предельная цифра (п-1), которая остается п для всехболее старших разрядов с порядковым номером не более (/+), где / - разрядность суммируемых чисел. Самый младшнй разряд, содержащий (п-I) шин нереносов, имеет ту особенность, что с него начинается непочка последовательного распространения нереноса в старнтие

разряды. В разрядах с порядковым номером, большим (г+1), количество шин переносов в разряд постепенно падает до единицы в самом старшем разряде устройства. Количество линеек в разряде зависит от иорядкового номера его и количества слагаемых.

При суммировании девяти чисел максимальное количество линеек в разрядах равно пяти. Количество разрядов сумматора определяется количеством п и разрядностью суммируюш,их чисел.

Указанный лметод построения суммирующего устройства обеспечивает параллельное распростраиепие переиосов во всех разрядах одновременно и наличие всего одной цеиочки последовательного распространения переноса независимо от числа слагаемых.

Устройство работает следующим образом.

На входные шины чисел разрядов (6-23) поступают одновремеино сигналы, обработка которых ведется на иервой лииейке каждого из разрядов. Пройдя эле.менты пер.вых линеек разрядов (в /п-м разряде это 24-29, сигналы с выходов суммы сумматоров первых линеек подаются на входы сумматоров второй линейки этого же разряда (элементы 30, 31), сигналы с выходов переноса - на входы сум.маторов второй линейки соседнего старшего разряда (элементы 32, 33 в (пг+1)-м разряде). В следующих по порядку линейках (второй, третьей и т. д.) сигиалы обрабатываются аналогичным образом до тех пор, пока сигнал пройдет на выход суммы сумматора последней (пятой) линейки разрядов (выходы 53 и 54).

Рассмотрим конкретный пример работы сумматора.

Пусть на входные ш;ииы 6-10 чисел подаются пять сигналов, соответствующих единицам в кодах суммируемых чисел разряда, а иа входные шины 40 и 41 переносов - два сигнала, соответствующие единицам в кодах переносов из (т-1)-го разряда.

На остальные входные шины разрядов поступают сигналы, соответствующие нулям в кодах чисел или переносов. При рассмотреппых условиях пунктирные линии около цепей коммутации наглядно иллюстрируют динамику прохождения сигналов в двух разрядах устройства. При этом коды суммы в т-м и (/п+1)-м разрядах содержат единицы (выходы 53, 54), а из (/п-М)-го разряда вы55341 , 74 Т

рабатывается один сигнал переноса (по шине 49) в (/п + 2)-й разряд. Уровень расположения шин переносов по линейке разряда соответствует очередности по времени появле5 иия сигнала в шине переноса.

Суммирующее устройство содержит минимально возможное количество логических элементов в схеме и имеет высокую скорост суммирования чисел.

10 Можно показать, что вре.мя суммирования п чисел разрядностью г на предлагаемом устройстве составляет величину

TV,, (6,6te« - 4,б)тэ+ ()т,

5 Задержки элементов «И, «ИЛИ, «ЗАПРЕТ, из которых состоит неполный сумматор, приняты одинаковыми и обозначены в формуле Тэ . Первое слагаемое представляет собой время параллельного распространения

20. переносов в устройстве с точностью до 2тэ Важно отметить логарифмический характер зависимости его от количества суммируемых чисел, что обеспечивает слабое увеличение TV с росто.м п.

25 Второе слагаемое определяет вре.мя сквозного распространения переноса в суммирующем устройстве.

Необходимый для построения устройства объем оборудования в единицах неполного

30 су.мматора может быть определен по выражению,

Zv 2 (п-1) г (Ig2n) ц

Здесь второе слагаемое означает округле35 i-nie значения до целого в большую сторону.

Преддмет изобретения

40 Многовходовое суммирующее устройство, содержащее в каждом разряде су.м.маторы, сгруппированные в линейки, выходы «сумма ка кдого сумматора младших линеек соединены с входами сумматоров последующих линеек, отличающееся те.м, что, с целью повышения быстродействия устройства, в нем щины всех слагаемьгх каждого разряда подключены к входам сумматоров нервой линейки, а выходы переноса су.мматоров младщих линеек соединены с одними из входов сумматоров последующих линеек соседнего старщего разряда.

37X59

44

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовое суммирующее устройство | 1980 |

|

SU898422A1 |

| Устройство для суммирования | 1978 |

|

SU955036A1 |

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| СХЕМА УСКОРЕННОГО ПЕРЕНОСА (ВАРИАНТЫ) | 1999 |

|

RU2149443C1 |

| Устройство для сложения @ чисел | 1980 |

|

SU1012243A1 |

| Устройство для возведения в квадрат @ -разрядных двоичных чисел | 1990 |

|

SU1784977A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Устройство для суммирования N чисел | 1987 |

|

SU1462293A1 |

| Суммирующее устройство | 1987 |

|

SU1451681A1 |

| Фазо-импульсный сумматор | 1977 |

|

SU651343A1 |

Авторы

Даты

1974-12-30—Публикация

1971-09-24—Подача