Одна из комбинаций кода ветвления служит для определения нризнака конца операции. В конце операции в адресном регистре 2 устанавливается фиксированный адрес (например, нулевой), который определяет начало микропрограммы выборки следующей команды.

При этом адресное поле 7 регистра микрокоманды 4 свободно используется для установки регистра признака результата 9. Если команда требует установки регистра призпака результата 9, то в поле ветвлепня 6 последней микрокоманды записывается код признака конца операции, а в адресное поле 7 - код, определяющий тип операции с точки зрения признака результата.

Например, во всех арифметических операциях с фиксированной запятой, использующих знаковую арифметику, записывается один код во всех логических операциях - другой код, в операциях с плавающей запятой - третий код и т. д.

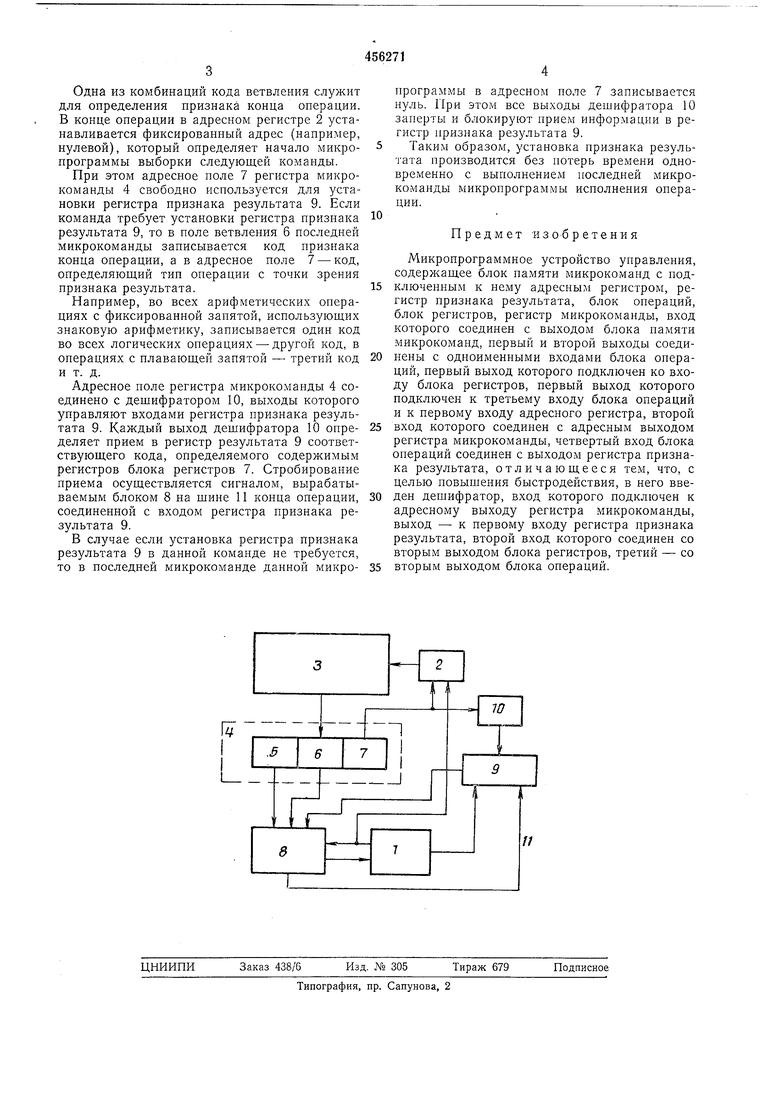

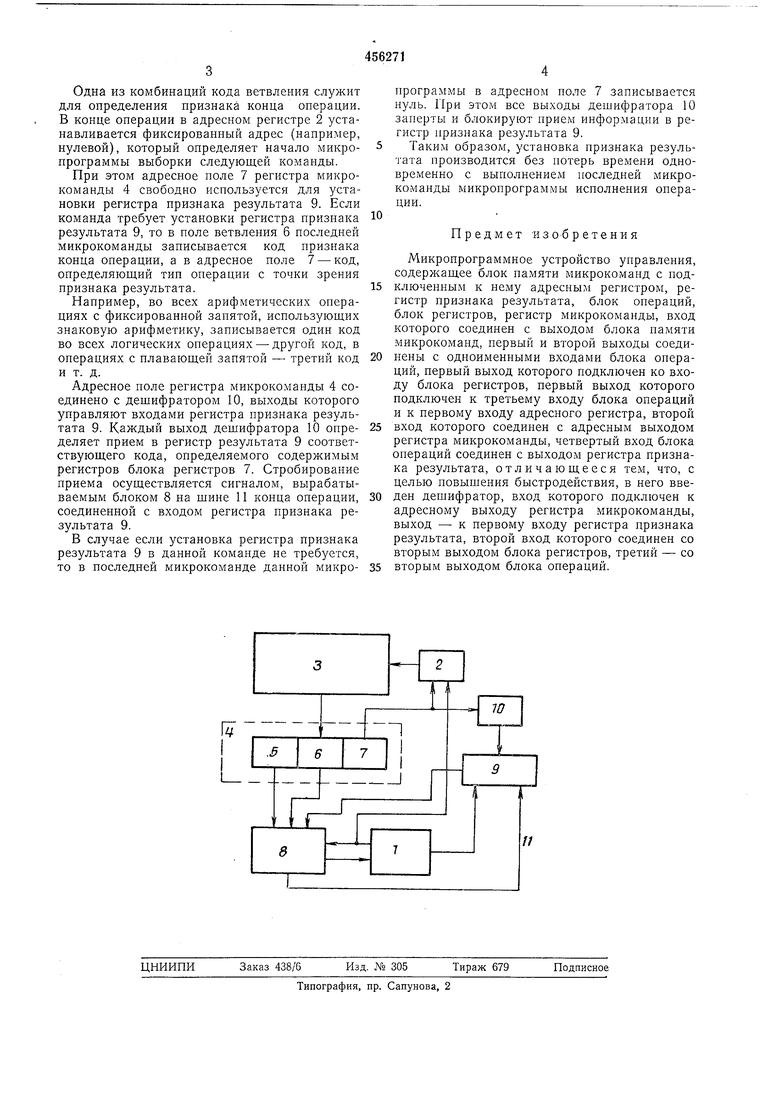

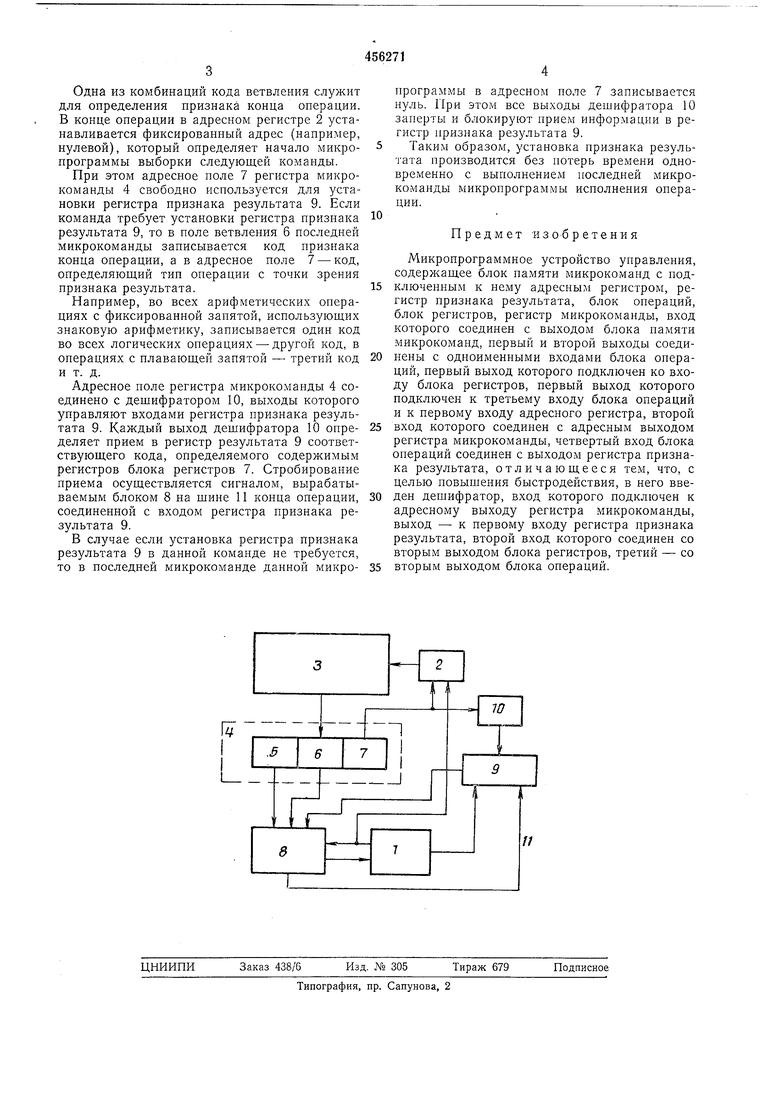

Адресное поле регистра микрокоманды 4 соединено с дешифратором 10, выходы которого управляют входами регистра признака результата 9. Каждый выход дешифратора 10 определяет прием в регистр результата 9 соответствующего кода, определяемого содержимым регистров блока регистров 7. Стробирование приема осуществляется сигналом, вырабатываемым блоком 8 на щине 11 конца операции, соединенной с входом регистра признака результата 9.

В случае если установка регистра признака результата 9 в данной команде не требуется, то в последней микрокоманде данной микропрограммы в адресном ноле 7 записывается нуль. При этом все выходы дешифратора 10 заперты и блокируют прием информации в регистр признака результата 9.

Таким образом, установка признака результата производится без потерь времени одновременно с выполнением последней микрокоманды микропрограммы исполнения операции.

Предмет изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд с подключенным к нему адресным регистром, регистр признака результата, блок операций, блок регистров, регистр микрокоманды, вход которого соединен с выходом блока памяти микрокоманд, первый и второй выходы соединены с одноименными входами блока операций, первый выход которого подключен ко входу блока регистров, первый выход которого подключен к третьему входу блока операций и к первому входу адресного регистра, второй вход которого соединен с адресным выходом регистра микрокоманды, четвертый вход блока операций соединен с выходом регистра признака результата, отличающееся тем, что, с целью повышения быстродействия, в него введен дешифратор, вход которого подключен к адресному выходу регистра микрокоманды, выход - к первому входу регистра признака результата, второй вход которого соединен со вторым выходом блока регистров, третий - со вторым выходом блока операций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU934473A1 |

| Микропрограммное устройство управления | 1974 |

|

SU503240A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммный процессор | 1974 |

|

SU512471A1 |

| Микропрограммный процессор | 1973 |

|

SU490122A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный модуль | 1984 |

|

SU1193675A1 |

Авторы

Даты

1975-01-05—Публикация

1973-01-24—Подача