1

Изобретение относится к вычислительной технике и предназначено для суммирования или вычитания Последовательности входных импульсов.

Известен реверсивный счетчик, каждый разряд которого выполнен на счетном триггере, состоящем из триггера памяти, коммутационного триггера и трех схем И-НЕ, причем единичный выход триггера намяти соединен с нулевым входом коммутационного триггера, единичный выход коммутационного триггера соединен с нулевым входом триггера иамяти, а нулевой выход коммутационного триггера соединен с входом второй схемы И-НЕ, выход которой соединен € входом третьей схемы И-НЕ, выход третьей схемы И-НЕ соединен с входом лервой схемы И-НЕ и с единичным входом триггера намяти. Кроме того, нулевой выход коммутационного триггера соединен со схемой И-НЕ управления вычитанием, выход которой соединен с нулевым и единичным входами коммутационного тритгера носледующего старшего разряда, а выход второй схемы И-НЕ данного разряда соединен с входом схемы управления еложением, выход которой соединен с входами первой и третьей схем И-НЕ последующего старшего разряда.

Целью изобретения является повышение быстродействия.

Для этого выход единичного плеча ком.мутационного триггера и выход первой схемы И- НЕ соединены с входами схемы И-НЕ управления Сложением.

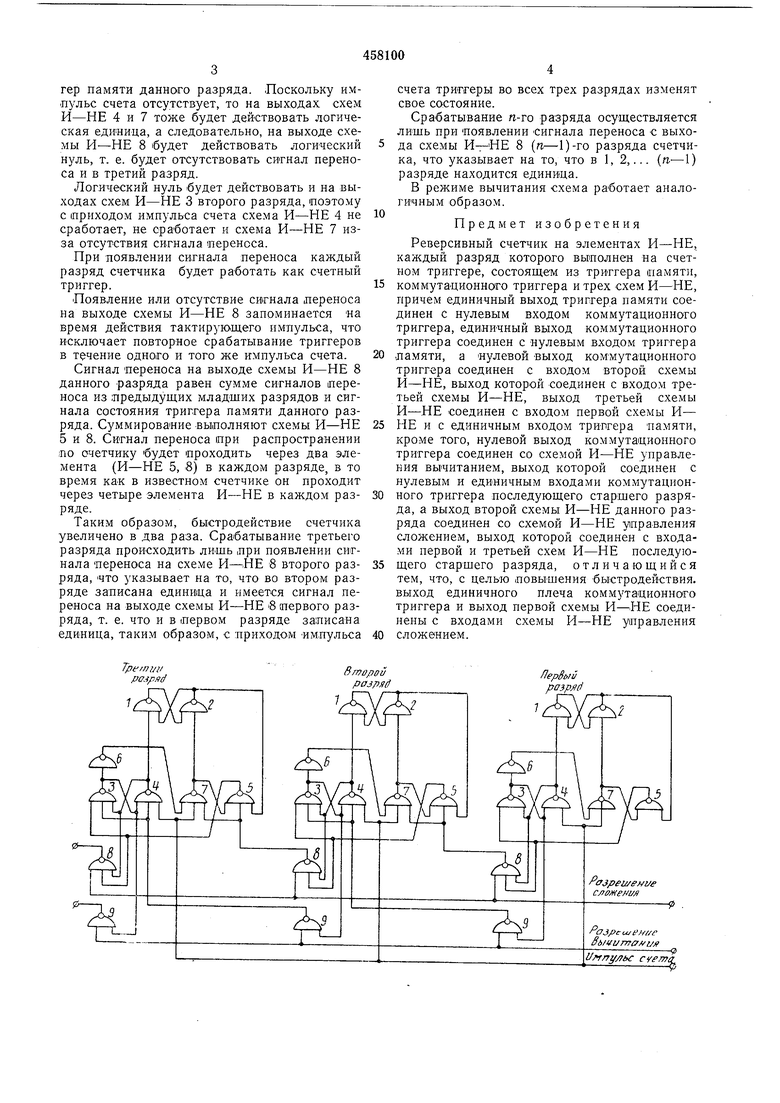

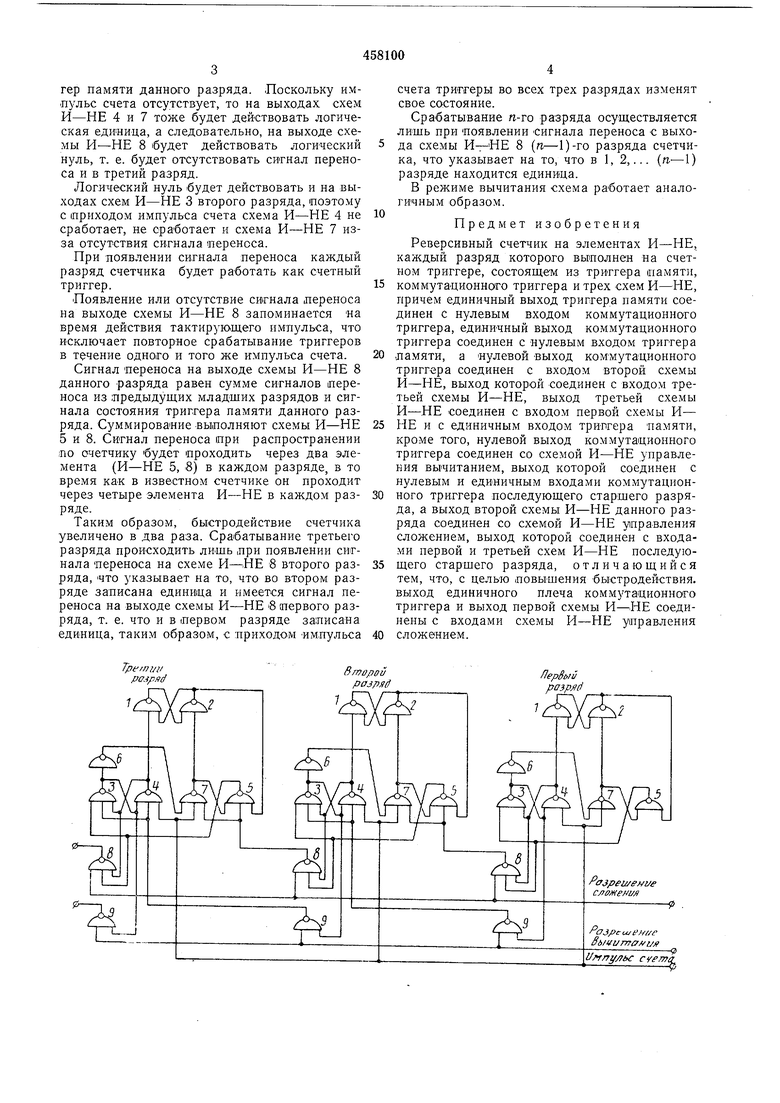

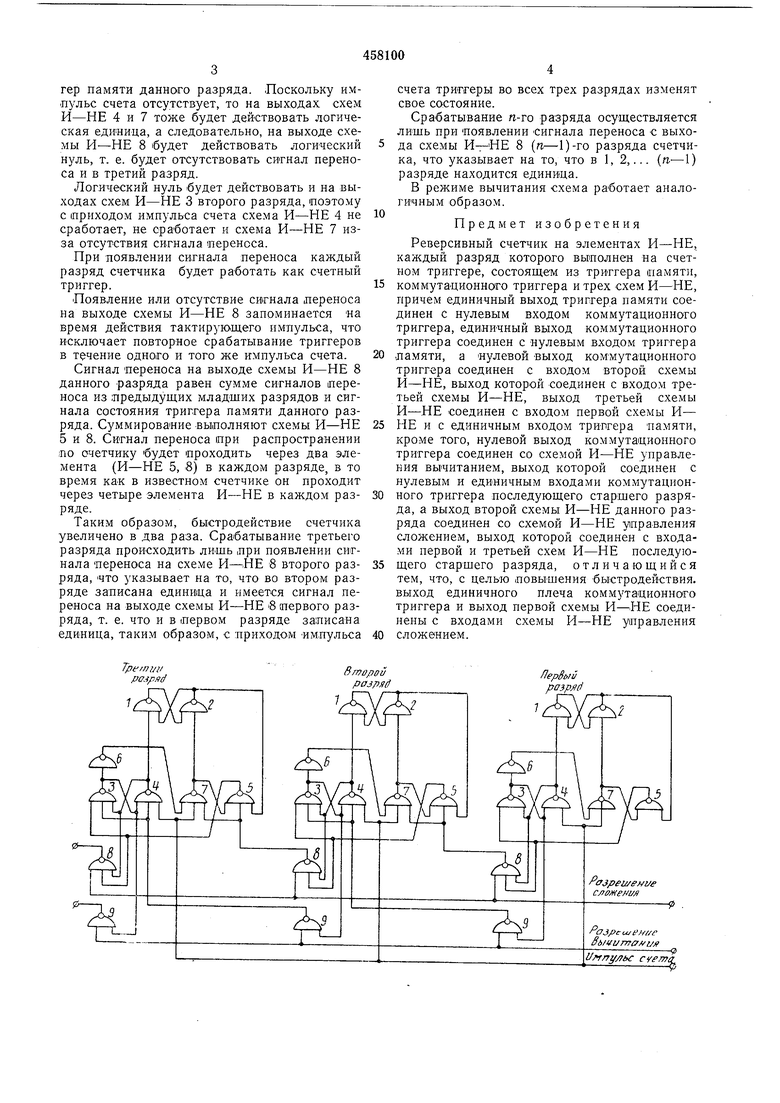

На чертеже приведена блок-схема счетчика.

Реверсивный счетчик содержит схемы И- НЕ 1 и 2, образующие триггер памяти, схемы И-НЕ 3 и 4, образующие коммутационный триггер, схемы И-НЕ 5, 6, 7, образующие соответственно первую, вторую и третью схемы И-НЕ. Схемы И-НЕ 8 образуют схемы управления сложением, а схемы И-НЕ 9 - схемы управления вычитанием.

Счетчик работает следующим образом.

В режиме суммирования на входы схе.м И- НЕ 8 поступают сигналы, равные логической едииипе, а иа входы схем И-НЕ 9 - сигналы, равные логическому нулю.

Нервый разряд счетчика работает, как обычный триггер со счетным входом. Носкольку на выходе схем И-НЕ 9 сигнал равен логической единице, срабатывание второго разряда осуществляется лишь при поступлении сигнала переноса с выхода.

Схема И-НЕ 8 первого разряда содержит единицу. Если сигнал переноса отсутствует, т. е. если он равен логическому нулю, то на выходе схемы И-НЕ 7 второго разряда логическая единица будет действовать независимо от того, в каком состоянии находится триг

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик | 1973 |

|

SU476687A1 |

| Реверсивный счетчик с последовательным переносом | 1974 |

|

SU516196A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Коррелятор | 1981 |

|

SU1024933A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Быстродействующий счетчик | 1971 |

|

SU444330A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для формирования тестовой последовательности | 1986 |

|

SU1529293A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2004 |

|

RU2284653C2 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2004 |

|

RU2269199C2 |

Авторы

Даты

1975-01-25—Публикация

1973-04-12—Подача