ш СЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Устройство для встроенного тестового контроля | 1984 |

|

SU1196877A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для вывода информации | 1986 |

|

SU1377849A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

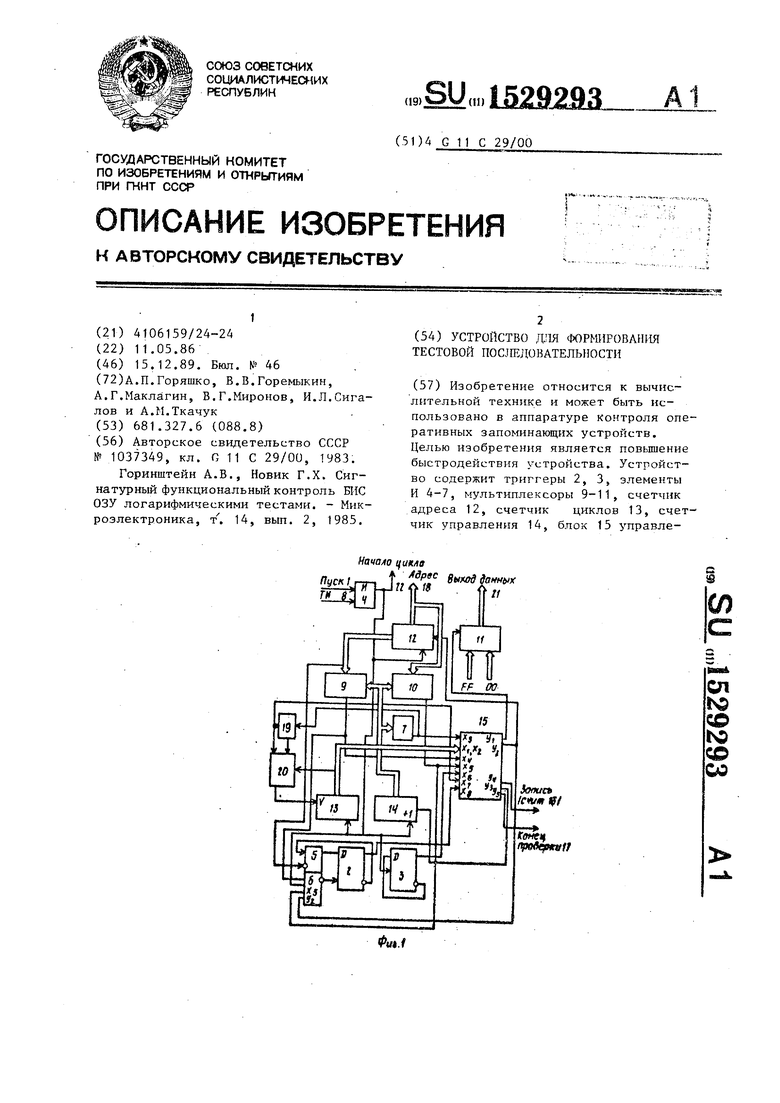

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре контроля оперативных запоминающих устройств. Устройство содержит триггеры 2, 3, элементы И 4-7, мультиплексоры 9-11, счетчик адреса 12, счетчик циклов 13, счетчик управления 14, блок 15 управления, элемент И 19 с соответствующими функциональными связями. Устройство значительно сокращает время контроля блоков оперативной памяти, т.к.весь режим контроля состоит из двух режимов: режима записи эталонных сигналов и режима чтения и сравнения. 2 ил.

ел

1чЭ

1C

со оо

iiiijij элемент И 19 с соответствующими функциональными связями. Устройство значительно сокращает время контроля блоков оперативной намяти, т.к. весь

Изобретение относится к вычисли- |тельиой технике и может быть использовано в апнаратуре контроля оперативных запоминающих устройств.

И.елью изобретения является повышение быстродействия устройства.

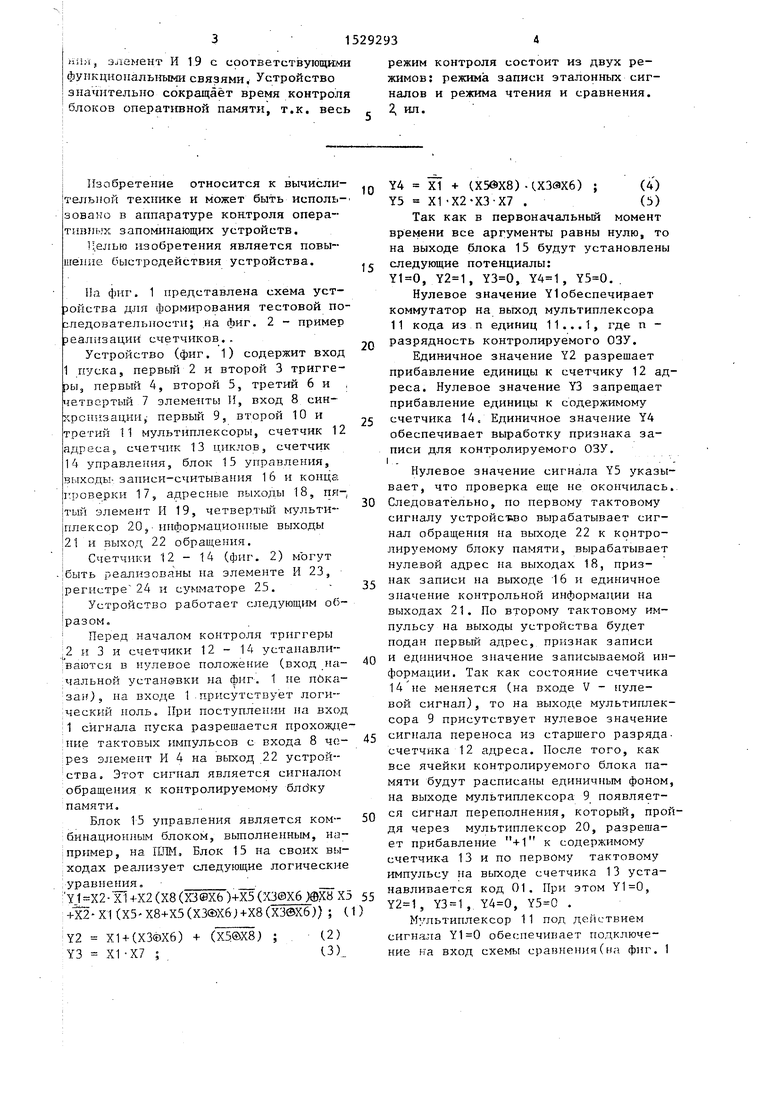

ila фиг. 1 представлена схема устройства для формирования тестовой последовательности; .На фиг, 2 - пример реал5 зации счетчиков. .

Устройство (фиг. 1) содержит вход 1 пуска, первый 2 и второй 3 тригге- рЫз первый 4, второй 5, третий 6 и четвертый 7 элементы И, вход 8 сии- хрсн5;зации,; первый 9, второй 10 и третий 11 мультиплексоры, счетчик 12 адреса5 счетчик 13 циклов, счетчик 14 управления, блок 15 управления, выходы-записи-считывания 16 и конца проверки 17, адресные выходы 18, пя|ть й элемент И 19, четвертый мульти - |плексор 20,-информационные выходы 121 и выход 22 обращения. I Счетчики 12-14 (фиг. 2) могут . ;быть реализованы на элементе И 23, {регистре 24 и сумматоре 25. I Устройство работает следующим об- |разом„

Перед началом контроля триггеры и 3 и счетчики 12-14 устанавли- : ваются в нулевое положение (вход на- :чальной устанэвки на фиг. 1 не пйка- зан), на вхо;,е 1 .присутствует логи-- ческий ноль. При поступлении на вход 1 сигнала пуска разрешается прохожде :ние тактовых импульсов с входа 8 чс- :рез элемент И 4 на выход 22 устройства. Этот сигнал является сигналом обращения к контролируемому бло ку памяти.

Блок 15 управления является комбинационным блоком, выполненным, на- ;пример, на ШТМ., Блок 15 на своих вы- ходах реши1зует следующие логические

уравнения. .

YJ X2- X1 +Х2 (Х8 (X3SX6 )+Х5 (ООХб )ФХ8 Х +Х2-Х1(Х5 Х8+Х5(ХЗ®Х6;+Х8(ХЗ®Х6)) ; (

iY2 Х1+(ХЗ®Х6) + (Х5®ХВ) Y3 Х1Х7 ;

(2) U)

режим контроля состоит из двух режимов: режима записи эталонных сигналов и режима чтения и сравнения. 2, ил.

0

5

0

5

0

5

5

0

5

0

Y4 XI + (Х5вХ8) ЧХЗахб) ; (4) Y5 Х1Х2-ХЗ-Х7 .(5)

Так как в первоначальный момент времени все аргументы равны нулю, то на выходе блока 15 будут установлены следующие потенциалы: , , , , . .

Нулевое значение Y1обеспечивает коммутатор на выход мультиплексора 11 кода из п единиц 11 ... 1 , где п - разрядность контролируемого ОЗУ.

Единичное значение Y2 разрешает прибавление единицы к счетчику 12 адреса. Нулевое значение Y3 запрещает прибавление единицы к содержимому счетчика 14. Единичное значение Y4 обеспечивает выработку признака записи для контролируемого ОЗУ. I . . Нулевое значение сигнала Y5 указывает, что проверка еще не окончилась. Следовательно, по первому тактовому сигналу устройство вырабатывает сигнал обращения на выходе 22 к контролируемому блоку памяти, вырабатывает нулевой адрес на выходах 18, признак записи на выходе 16 и единичное значение контрольной информации на выходах 21. По второьгу тактовому импульсу на выходы устройства будет подан первый адрес, признак записи и единичное значение записываемой информации. Так как состояние счетчика 14 не меняется (на входе V - нулевой сигнал), то на выходе мультиплексора 9 присутствует нулевое значение сигнала переноса из старшего разряда, счетчика 12 адреса. После того, как все ячейки контролируемого блока намяти будут расписаны единичным фоном, на выходе мультиплексора 9 появляется сигнал переполнения, который, пройдя через мультиплексор 20, разрешает прибавление +1 к содержимому счетчика 13 и по первому тактовому импульсу на выходе счетчика 13 устанавливается код 01. При этом , , Y3 1 ,, , .

fyльтиплeкcop 11 под действием сигн;1ла обеспечивает подключение вход схемы сравнения (на фиг, 1

не показана) сигнала логических единиц, на второй вход поступает считанный сигнал из контролируемого блока памяти. Так как , то на Jixofl блока памяти поступает признак считыва- ния, и сигналом разрешается вьщача на выход устройства сигнала на сравнение. Единичный сигнал Y3 обеспечивает снятие сигнала запрета счета на счетчик 14. В результате под действием тактового сигнала счетчик 14 установит их в единичное состояние, после чего в соответствии с уравнением (3) Y3 станет равным нулю, так как сигнал Х7 станет равным нулю, из-за того, что счетчик 12 этим тактовым импульсом установится в нулевое состояние. Таким образом, Y1, Y2, Y3, Y4 и Y5 не будут меняться до тех пор, пока счетчик 12 не досчитает до половины его емкости.

Независимо от разрядности счетчика описанный процесс будет продолжаться без изменения до тех пор, пока не будет установлен в единицу предпоследний разряд. При этом на выходе мультиплексора 10 возникает единичный сигнал (). Это приводит к тому, что Y2 становится равным единице, , , . При этом устройство из режима считывания переходит в режим записи, мультиплексор 11 на выход пропускает код 00.

По следу101цему тактовому импульсу в контролируемый блок памяти по адресу 1 будет записан код 00. Следующий тактовый импульс установит в единицу триггер 3. При этом на выходах блока 15 управления будут ус тановлень следующие значения: , , , . По следующему тактовому импульсу счетчик 12 изменит свое состояние (триггер 3 сбросится в нуль по счетному входу) и устрой- ство обеспечит считывание и сравнени данных с нулем. Следующий тактовый сигнал установит триггер .3 в единицу и работа устройства будет происходить аналогично описанному.

Работа устройства будет продолжаться, пока не закончится роспись всего контролируемого ОЗУ инверсными кодами. После окончания росписи контролируемого ОЗУ происходит пере- полнение счетчика-12 адреса, вьфаба- тывается сигнал , который, пройдя через элемент И 19 и мультиплексор 20, разрешит прибавление +1 к

.д jr20

92936

содержимоь{у счетчика 13. На выходе

r 0

5 о

5

0 5 0

блока 15 будут установлены следующие коды: , , , , . Следующим тактовым импульсом на счетчике 13 будет установлен код 10, на счетчике 14 - код 1, При этом на выход мультиплексора 9 будет ском- мутирован перенос из (n-l)-ro разряда счетчика 12 адреса (п - количество разрядов счетчика), а на выход мультиплексора 1.0 - (,п-1 )-й разряд счетчика. На выходе блока 15 управления будут установлены следующие значения. , , , , . Работа устройства будет протекать аналогично описанному до тех пор, пока сигнал на выходе мультиплексора 10 не примет единичное значение, а значит, пока устройство не проверит 1/4 всех ячеек контролируемого блока памяти, т.е. пока не установится в единицу (п-1 )-й разряд счетчика 12 адреса. Блок 15 управления на своих выходах установит коды: , , , , .

Следующим тактовым iмпyльcoм устройство по адресу () произведет запись нуля. После этого еще одним тактовым импульсом триггер 3 установится в единичное значение и тем самым будет обеспечена выработка на выходе блока 15 следующих значений : , , , . Таким образом, следующим тактовьм импульсом будет считана информация с адреса 2 , .а затем в этот же адрес будет занесена инфорьшция инверсная записанной, так как сигнал Y1 примет единичное значение. Описанньп процесс будет продолжаться до тех пор, пока триггер 2 не установится в единичное значение. Установка триггера 2 произойдет, когда сигнал на выходе мультиплексора 9 и . В этом случае по тактовому импульсу триггер 2 переключится в состояние 1 и останется в этом состоянии до конца проверки, так как нулевое значение сигнала на втором входе элемента И 5 с нулевого выхода триггера 2 установит на D-входе нулевой потенциал;

После того, как процесс проверки ОЗУ (с первоначальной росписью единицами) окончится, появится перенос из старшего разряда счетчика 12, который через элемент И 19 поступит на единичный вход мультиплексора 20 и далее на вход разрешения счетчика.

71

в состояние 1, появится .второй перенос из старшего разряда счетчика 12 и на счетчике 13 будет уставов-лен код 10. При этом устройство пе- рендет в режим рс)спись контролируемо го ОЗУ фоном нулей , , , , , т.е. до переполнения счетчяка 12 сигнал переполнения укажет на окончание росписи контролируемого ОЗУ фоном нулей.

Далее процесс будет протекать так )KOj как описано, с той лишь разницей что па счетчике 13 будет-установлен код 11. Процесс контроля будет.продолжаться, пока па счетчике 14 не установится код из п единиц 1... 1 и не появится четвертый перенос из счетчика 12. Единичное значение Yb укажет на конец проверки,.по которому снимается сигнал пуска на входе 1. Снятие сигнала пуска происходит так же при обнаружении ошибки (на фиг. 1 не показано).

Формула изобретения

Устройство для формирования тестовой последовательности, содержащее блок управления, триггер, счетчик адреса, выходы младших разрядов которого являются адресными выходами- устройства и соединены с информационными входами второго мультиплексора, счетчик управления, выходы которого подключен к управляюш;им входам первого и второго мультиплексоров, третий гyльтишleкcop, отличаю- щ е е с я тем, что, с целью повьшю- ния быстродействия, в устройство введены элементы И с первого по пятый, счетчик циклов, четвертый мультиплексор, счетный триггер, причем входы первого элемента И являются соответственно входами пуска и синхронизации устройства, выход первого-элемента И является выходом начала цикла устройства и соединен с синхровхо- дамп счет чика адреса, счетчика управления и счетчика циклов, с синхровхо- дом счетного триггера и с вторым вхо-1

92938

дом третьего элемента И, первый вход которого подключен к четвертому входу блока управления и к выходу первого мультиплексора, информационные входы которого соединены с выходами страших разрядов,счетчика адреса, выход переполнения которого подключен к седьмому входу блока управле- ,4 ПИЯ, инверсному входу второго элемента И, первому входу пятого элемента И и к первому информационному входу четвертого мультиплексора, второй информационный вход, управляю,г щий вход и выход которого соединены соответственно с выходом переполнения счетчика циклов, выходом пятого элемента И и с управляющим входом счетчика циклов, выходы которого

подключены к первому и второму входам блока управления третий вход которого соединен с вторым входом пятого элемента И и с выходом четвертого элемента И, входы ко.торог о подключены к выходам счетчика управления, управляющий вход которого соединен с третьим выходом блока управления, первый выход которого подключен к управляющему входу третьего

мультиплексора, информационные входы первой и второй групп которого являются входами прямых и инверсных эталонных данных устройства, а выходы являются информационньйчи выходами устройства, второй выход блока управления соединен с управляющим выходом счетчика адреса и с четвертым входом третьего элемента И, третий вход которого подключен к выходу второго мультиплексора и к пятому входу блока управления, шестой и восьмой входы которого соединены с прямыми выходами соответственно счетного триггера и триггера, инверсный выход которого подключен к прямому входу второго элемента И, выход которого соединен с информационным входом триггера, синхровход которого подключен к инверсному выходу третьего элемента И, четвертый и пятый выходы блока управления являются соответственно выходами записи считывания и конп.а проверки устройства.

Фм.г

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Сигнатурный функциональный контроль БНС ОЗУ логарифмическими тестами, - Микроэлектроника, т | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-12-15—Публикация

1986-05-11—Подача