1

Изобретение относится к построению узлов Ёычислительной техники и Дискретной автоматики на потенциальных логических элементах в микроэлектронном исполнении.

Известен реверсивный счетчик с иоследовательным переносом, каждый разряд которого содержит триггер памяти и два коммутационных триггера, содержащих по два элемента «И-НЕ каждый, соединенных по схеме счетного триггера, а также, начиная со второго, 1ервый и второй элементы «И-НЕ, шины сложения и вычитания.

Однако известные реверсивные счетчики имеют невысокое быстродействие.

С целью повышения быстродействия в предлагаемом счетчике входы и выходы первого и второго элементов «И-НЕ соединены аналогично соединению входов и выходов элементов «И-НЕ соответственно первого и второго коммутационных триггеров, выходы которых соединены с входами триггеров памяти, шина сложения подключена к входам тех элементов «И-НЕ коммутационных триггеров, выходы которых соединены с входами триггеров памяти соответствуюш,их разрядов, кроме первого, шина вычитания соединена с входами первого и второго элементов «И-НЕ всех разрядов, единичный выход триггера памяти соединен с входами первого

И второго элементов «И-НЕ следукзщего разряда.

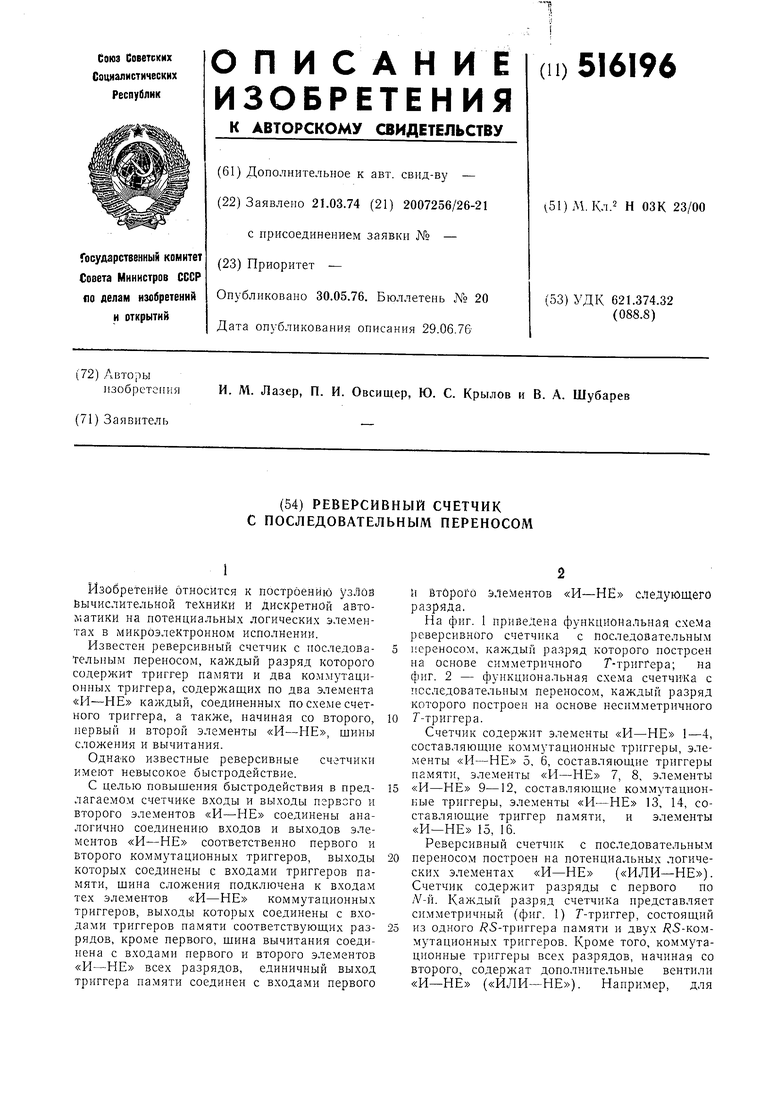

На фиг. 1 приведена функциональная схема

реверсивного счетчика с последовательным

переносом, каждый разряд которого построен

на основе симметричного Г-тригГера; па

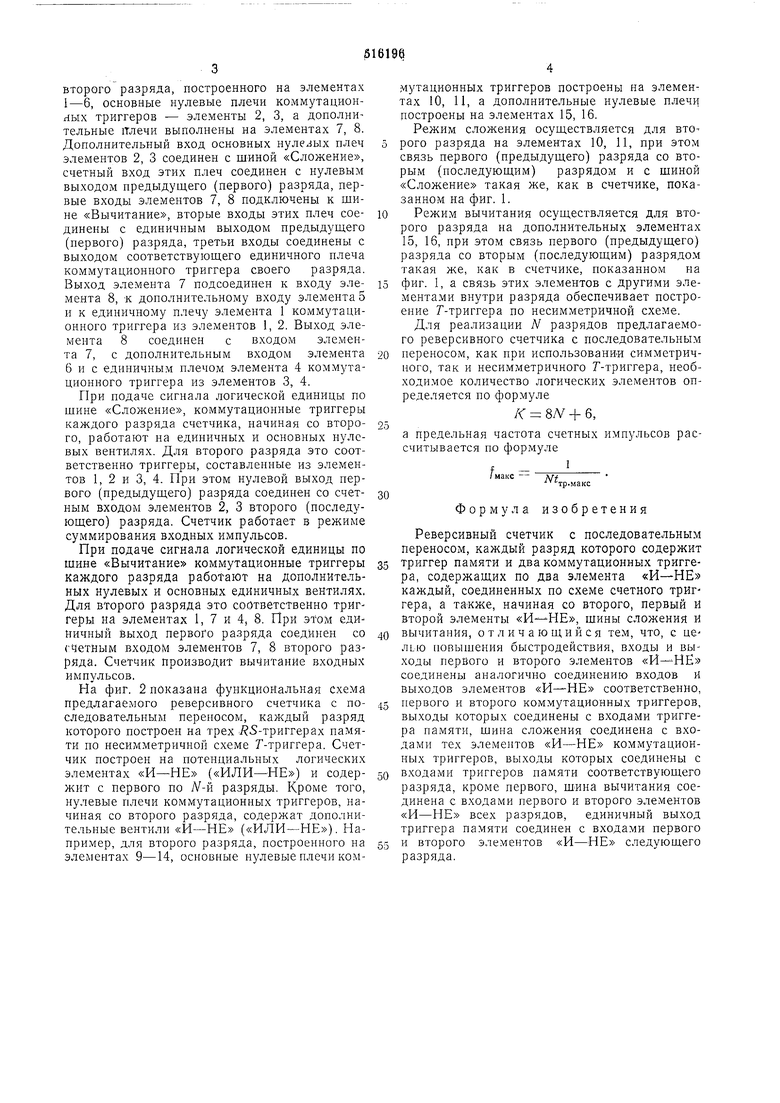

фиг. 2 - функциональная схема счетчика с

последовательным переносом, каждый разряд

которого построен на основе несимметричного

Г-триггера.

Счетчик содержит элементы «И-НЕ 1-4, составляющие коммутационные триггеры, эле.менты «И-НЕ 5, 6, составляющие триггеры памяти, элементы «И-НЕ 7, 8, элементы «и-НЕ 9-12, составляющие коммутационные триггеры, элементы «И-НЕ 13, 14, составляющие триггер памяти, и элементы «И-НЕ 15, 16.

Реверсивный счетчик с последовательным переносом построен на потенциальных логических элементах «И-НЕ («ИЛИ-НЕ). Счетчик содержит разряды с первого по jV-й. Каждый разряд счетчика представляет симметричный (фиг. 1) Г-триггер, состоящий из одного / 5-триггера памяти и двух RS-Koyiмутационных триггеров. Кроме того, коммутационные триггеры всех разрядов, начиная со второго, содержат дополнительные вентили «И-НЕ («ИЛИ-НЕ). Например, для

второго разряда, построенного на элементах 1-6, основные нулевые плечи коммутационных триггеров - элементы 2, 3, а дополнительные плечи выполнены на элементах 7, 8. Дополнительный вход основных нулевых плеч элементов 2, 3 соединен с шиной «Сложение, счетный вход этих плеч соединен с нулевым выходом предыдущего (первого) разряда, первые входы элементов 7, 8 подключены к шине «Вычитание, вторые входы этих плеч соединены с единичным выходом предыдущего (первого) разряда, третьи входы соединены с выходом соответствующего единичного плеча коммутационного триггера своего разряда. Выход элемента 7 подсоединен к входу элемента 8, к дополнительному входу элемента 5 и к единичному плечу элемента 1 коммутационного триггера из элементов 1, 2. Выход элемента 8 соединен с входом элемента 7, с дополнительным входом элемента 6 и с единичным плечом элемента 4 коммутационного триггера из элементов 3, 4.

При подаче сигнала логической единицы по шине «Сложение, коммутационные триггеры каждого разряда счетчика, начиная со второго, работают па единичных и основных нулевых вентилях. Для второго разряда это соответственно триггеры, составленные из элементов 1, 2 и 3, 4. При этом нулевой выход нервого (предыдущего) разряда соединен со счетным входом элементов 2, 3 второго (последующего) разряда. Счетчик работает в режиме суммирования входных импульсов.

При подаче сигнала логической единицы по шине «Вычитание коммутационные триггеры каждого разряда работают на дополнительных нулевых и основных единичных вентилях. Для второго разряда это соответственно триггеры на элементах 1, 7 и 4, 8. При этом едийичный выход первого разряда соединен со счетным входом элементов 7, 8 второго разряда. Счетчик производит вычитание входных импульсов.

На фиг. 2 показана функциональная схема предлагаемого реверсивного счетчика с последовательным переносом, каждый разряд которого построен на трех 7 5-триггерах памяти по несимметричной схеме Г-триггера. Счетчик построен на потенциальных логических элементах «И-НЕ («ИЛИ-НЕ) и содержит с первого по разряды. Кроме того, нулевые плечи коммутационных триггеров, начиная со второго разряда, содержат дополнительные вентили «И-НЕ («ИЛИ-НЕ). Например, для второго разряда, построенного на элементах 9-14, основные нулевые плечи коммутационных триггеров построены на элементах 10, 11, а дополнительные нулевые плечи построены на элементах 15, 16.

Режим сложения осуществляется для второго разряда на элементах 10, 11, при этом связь первого (предыдущего) разряда со вторым (последующим) разрядом и с шиной «Сложение такая же, как в счетчике, показанном на фиг. 1.

Режим вычитания осуществляется для второго разряда на дополнительных элементах 15, 16, при этом связь первого (предыдущего) разряда со вторым (последующим) разрядом такая же, как в счетчике, показанном на фиг. 1, а связь этих элементов с другими элементами внутри разряда обеспечивает построение Г-триггера по несимметричной схеме.

Для реализации Л разрядов предлагаемого реверсивного счетчика с последовательным переносом, как при использовании симметричного, так и несимметричного Г-триггера, необходимое количество логических элементов определяется по формуле

K 8N + 6,

а предельная частота счетных импульсов рассчитывается по формуле

f1

/макс - rf

тр.макс

Формула изобретения

Реверсивный счетчик с последовательным переносом, каждый разряд которого содержит триггер памяти и два коммутационных триггера, содержащих по два элемента «И-НЕ каждый, соединенных по схеме счетного триггера, а та«же, начиная со второго, первый и второй элементы «И-НЕ, шины сложения и вычитания, отличающийся тем, что, с целью повышения быстродействия, входы и выходы первого и второго элементов «И-НЕ соединены аналогично соединению входов и выходов элементов «И-НЕ соответственно, первого и второго коммутационных триггеров, выходы которых соединены с входами триггера памяти, шина сложения соединена с входами тех элементов «И-НЕ коммутационных триггеров, выходы которых соединены с входами триггеров памяти соответствующего разряда, кроме первого, ш«на вычитания соединена с входами первого и второго элементов «И-НЕ всех разрядов, единичный выход триггера памяти соединен с входами первого и второго элементов «И-НЕ следующего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик | 1977 |

|

SU708516A2 |

| Реверсивный счетчик | 1985 |

|

SU1257839A1 |

| Реверсивный счетчик импульсов | 1976 |

|

SU664300A1 |

| Реверсивное счетное устройство | 1989 |

|

SU1713100A1 |

| Реверсивный счетчик | 1973 |

|

SU476687A1 |

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ГРУППОВЫМ ПЕРЕНОСОМ | 1970 |

|

SU287121A1 |

| Счетчик с параллельным переносом | 1974 |

|

SU507943A1 |

| Разряд счетчика по модулю три | 1971 |

|

SU445989A1 |

| Реверсивный счетчик | 1973 |

|

SU458100A1 |

Авторы

Даты

1976-05-30—Публикация

1974-03-21—Подача