1

Изобретение относится к технике измерений в области передачи дадных по дискретным каналам связи и может быть использовано ори иоследова1ниях, испытаниях и регламентных проверках дискретных каналов связи.

Известны устройства для контроля гканалов связи по 1веЛИчи1не иотерИ достоверности, -вкоторых анализатор принимаемых импульсов отмечает неправильно принятые элементы, .накапливаемые счетчиком ошибок, периодически сбрасываемым в нулевое состояние сигналом от датчика импульсов статистического сброса. Если счетчик переполняется до прихода очередного импульса сброса, то формируется сигнал о неисправности канала.

Отсутствие IB таком устройстве аппаратуры для запоминания результатов контроля не позволяет многократно иапользо1вать результаты контроля для получения статистических данных.

Цель изобретения - повышение эффективности контроля.

Цель достигается тем, что предлагаемое устройство содержит ап1паратуру для запоминания реального потока ошибок, выявленных в процессе анализа дискретного канала связи. Аппаратура для демодуляции силналов, записанных на (Магнитную ленту, позгволяет многократно использовать записи потока ошибок, например, для моделирования воздействия помех в тракте передачи данных, для проверки эффективности корректирующих кодов, для исследования закономерностей распределения ошибок в дискретных каналах и т. д.

Двоичные состояния, отображающие регистрируемую информацию, выводятся для запоминания iB виде синхро.нных квазисинусоидальных частотно-манипулированных сигналов, что позволяет исключить отдельную дорожку для записи синхронизирующих импульсов, разделение информационных импульсов (модулей ошибок) и синхронизирующих импульсов производится IB блоках обработки при демодуляции сигналов с магнитной ленты; предусматривается также выход для запоминания знаков ошибок.

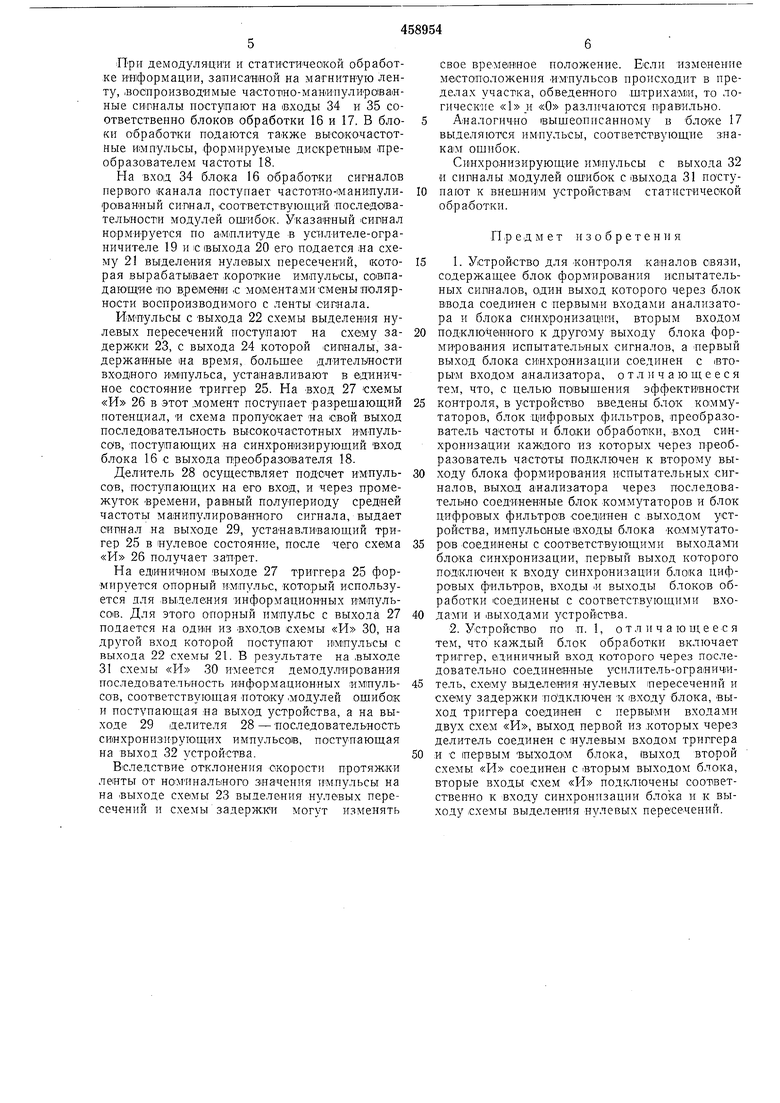

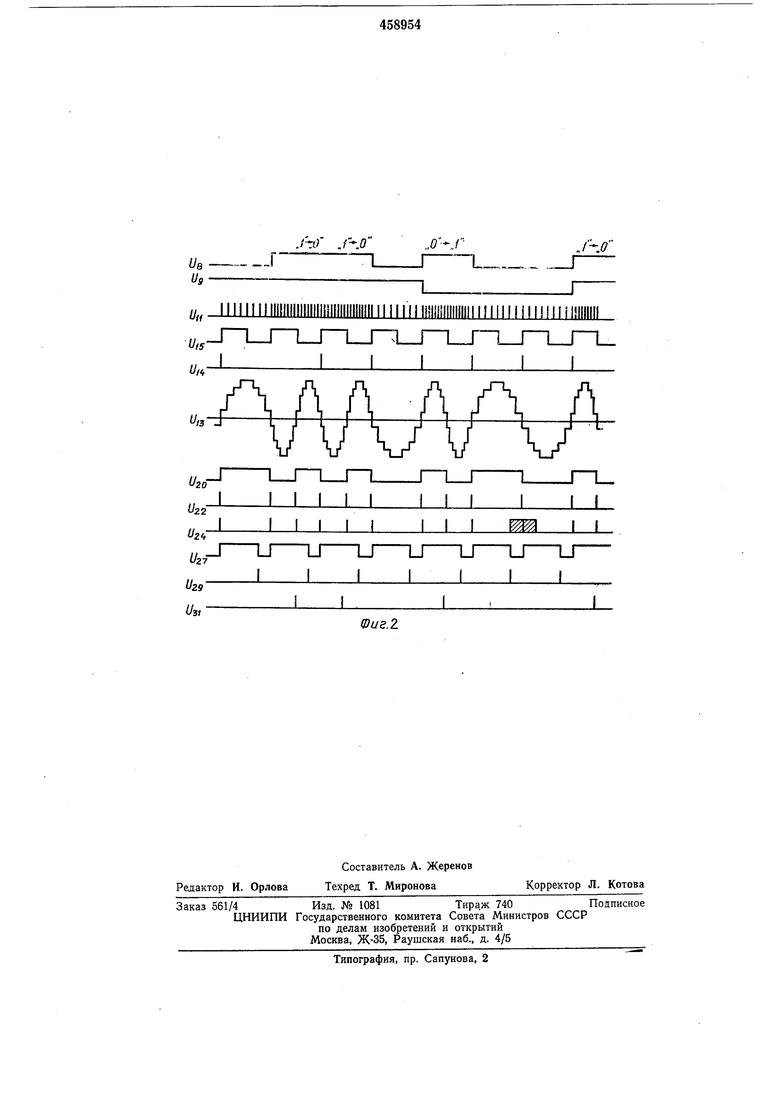

Сущность изобретения заключается в том, что в устройстве введены блок коммутаторов, блок цифровых фильтров, преобразователь частоты и блоки обработки, вход синхронизации каждого из которых через преобразователь частоты подключен к второму выходу блока формирования испытательных сигналов, выход анализатора через последовательно соединенные блок коммутаторов и блок цифровых фильтров соединен с выходом устройства, импульсные входы блока коммутаторов соединены с соответствующими выходами блока синхронизации, первый выход которого подключай ,к входу синхронизации блока цифровых фильтров, входы и выходы блоков обработки соединены .с соответствующими входами и выходами устройства. В устройстве каждый блок обработки включает триггер, еди1НИ Ч«ый вход которого через последовательно соединенные усилитель-ограиичитель, схему выделения нулевых иересечен ий и схему задержки подключен к входу блока, (ВЫХОД три.лгера соединен с первыми входами двух схем «И, .выход 1пе,рвой из которых через делитель соедвнен с нулевым входом триггера и с первым выходом блока, выход второй схемы «И соедияен с вторым выходом блока, вторые входы схем «И подключены соответственно к входу синхроиизации блока и 1К выходу схемы выделен-ия нулевых 1иереоечений. На фиг. 1 приведена блок-схема Предлагаемого устройства; на фиг. 2-временные диаграммы импульсов в характерных точках схемы, иричем индекс напряжения соответствует позиции точки, в которой наблюдается это напряжение. Устройство Содержит блок 1 фор;мирования иапытательных сигналов, блок ввода 2, блок синхронизации 3, состоящий из фазового различнтеля 4 узла управления 5 и управляемого делителя 6, анализатор 7 с выходами 8 и 9 сигнал а ошибки и сигнала знака ощ1ибки, блок коммутаторов 10 с выходом 11 импульсных сигналов, блок 12 цифровых фильтров с выходами 13 и 14 записываемых сигналов и импульсных сигналов установки, вырабатываемых в блоке .цифровых фильтров из тактовых импульсов на выходе 15 делителя 6, блоки 16, 17 обработки, преобразователь частоты.18, усилитель-ограничитель 19 с выходом 20, схему 21 выделения нулевых пересечений ,21 с выходом 22, схему 23 задержки с выходом 24, триггер 25, схему «И 26 с разрешающим сигналом на входе 27, делитель 28 с выходом 29, схему «И 30 1C информационными импульсами на выходе 31, выходы Э2, 33 устройства; входы 34, 35 устройства. Испытательная последовательность с выхода блока 1 формирования испытательных сигналов поступает в дискретный канал связи. После прохождения через исследуемый канал испытательная последовательность поступает в приемник, где производится выявление элементав, содержа-щих ощ1ибки. Приемник состоит из блока ввода 2, блока синхронизации 3 и анализатора 7. Блок ввода в моменты сманы полярности входного сигнала выдает короткие импульсы, поступающие яа фазовый различитель 4 блока синхронизации 3. Фазовый различитель осуществляет слежение за частотой приходящих из канала импульсов и выдает на узел упра1вления 5 сишалы, под действием которых происходит добаюлбние или вычитание импульсав в первом каскаде управляемого делителя 6. Таким образом осуществляется поэлементная синхронизация приходящей из канала связи испытатель(ной последовательности и эталонной комбинации, вырабатьгваемой анализатором 7. Анализатор 7 осуществляет исследование прини1маемой из канала связи испытательной последовательности с целью выявления ошибок. Для этого производится циклового фазирование принимаемой комбинации с эталонной, вырабатываемой в анализаторе 7; в результате на схему сраинения анализатора 7 подаются две одинаковые по структуре -и согласованные во времени ооследователыности, которые сравниваются поэлементно. Если 1ПОД действием мешающих факторов в канале связи значение элемента принимаемой последовательности меняется, то на выходе 8 модулей ошибок анализатора 7 имеется импульс ошибки (эиюра 8), сопровождаемый сигаалом знака ошибки на выходе 9. Эти сигналы поступают на управляющие входы блока коммутаторов 10, на импульсные входы которого с промежуточных ячеек управляемого делителя 6 блока синхронизации 3 подаются две импульсные последовательности, частоты которых кратны соответствующим рабочи частотам квазисинусоидального сигнала, записываемого на магнитную лшту. При отсутствии ошибок с выхода анализатора 7 поступает низкий потенциал, и блок коМ|Мутаторов 10 пропускает на свой выход 11 импульсы, соответствующие нижней рабочей частоте манипулированного сигнала. В блоке цифровых фильтров, состоящем из счетчиков и преобразователей код-аналог, этим импульсы преобразуются в -квазисинусоидальный сигнал, подаваемый для запоминания результатов анализа на выход 13. Записываемые сигналы синхронизируются импульсами установки с выхода 14, вырабатываемьши в блоке 12 цифровых фильтров из тактовых импульсов, поступающих с выхода 15 управляемого делителя 6 в блоке синхронизации 3. При появлении ошибок в анализируемой нформации на выходе В модулей ошибок анаизатора 7 имеется высокий потенциал, и блок оммутаторов 10 пропускает импульсы, соотетствующие верхней рабочей частоте, а на ыходе блока цифровых фильтров формируетя квазисинусоидальный сигнал. Таким образом, двоичные состояния, отобраающие отсутствие ошибок и наличие ошибок, ыводятся для ревистрации в виде синхронных 1вазисинусоидальных частотно-манипулироанных сигналов с нижней и верхней частотаи соответственно. Аналогично на выходе 14 блока цифровых ильтров формируется частотно-манипулироанный сигнал знака ошибки. Этот сигнал моет быть записан на отдельную дорожку магитной ленты. Ошибке типа трансформации 1 в «О соответствуетВЫСОКИЙ потенциал на ыходе знака ошибки анализатора 7, а ошибке ипа трансформации «О в «1 -низкий поенциал.

При демодуляЦ-ии и статистической обработке информации, записанной на магнитную ленту, .восироизводимые частотно-мандапулированные сирналы иоступают на входы 34 и 35 соответственно блоков обработки 16 и 17. В блоки обработки подаются также вьгсокочастотные импульсы, формируемые дискретным преобразователем частоты 18.

На вход 34 бло-ка 16 обработки сигналов первого канала поступает частотно-манилули|р01ван«ый сипнал, соответствующий последователыности модулей ошибо«. Укаэаиный сигнал нормируется по амплитуде в ус нлителе-ограничителе 19 и с (выхода 20 его подается на схему 21 выделения нулевых пересечений, которая вырабатывает .короткие имлульсы, совпадающие то времени .с моментами смены полярности воспроизводимого с ленты сигнала.

Импульсы с выхода 22 схемы выделения нулевых пересечений поступают на схему задержки 23, с выхода 24 которой сигналы, задержанные на время, большее длителыности входного импульса, устанавливают в единичное состояние триггер 25. На вход 27 схемы «И 26 в этот .момент поступает разрешающий потенциал, и схема пропускает на свой выход последовательность высокочастотных импульсов, поступающих на синхрониз-ирующий вход блока 16 с выхода П реобразо1вателя 18.

Делитель 28 осуществляет подсчет импульсов, поступающих на его вход, и через промежуток времени, равный полупериоду средней частоты манипулироваиного сигнала, выдает сипнал на выходе 29, устанавливающий тригер 25 в нулевое состояние, после чего схема «И 26 получает запрет.

На единичном выходе 27 триггера 25 формируется опорный импульс, который используется для выделения информанионных импульсов. Для этого опорный импульс с выхода 27 подается на один из входов схемы «И 30, на другой вход которой поступают импульсы с выхода 22 схемы 21. В результате на выходе 31 схемы «И 30 имеется демодулирован-ия последовательность информационных импульсов, соответствующая потоку модулей ошибок и поступающая на выход устройства, а на выходе 29 делителя 28-последовательность синхронизирующих импульсов, поступающая на выход 32 устройства.

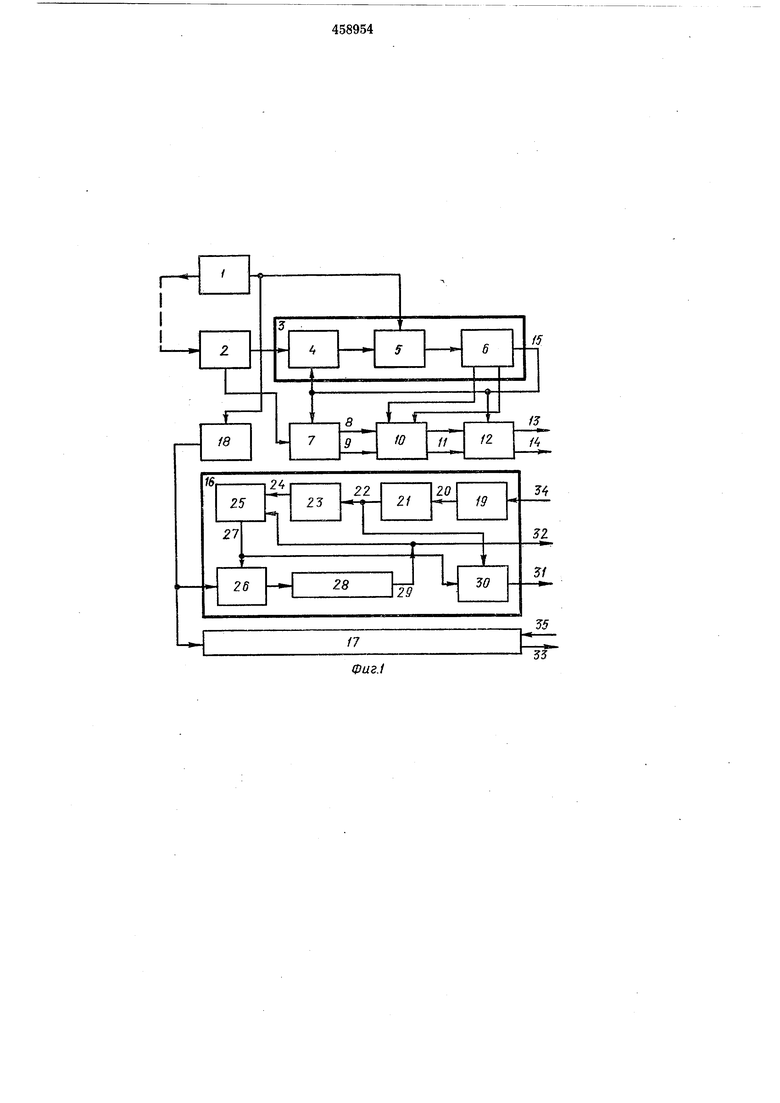

Вследствие отклонения скорости протяжки ленты от но:минального значения импульсы на на выходе схемы 23 выделения нулевых пересечений и схемы задержки могут изменять

свое временное положение. Если изменение местоположения импульсов происходит в пределах участка, обведенного штрихами, то логические «О различаются правильно.

Аналогично щыщеописанному в блоке 17 выделяются импульсы, соответствующие знакам ошибок.

Синхронизирующие им1пульсы с выхода 32 « сигналы .модулей ощибок с (выхода 31 поступают к внешний устройства м статистической обработки.

Предмет изобретения

1. Устройство для контроля каналов связи, содержащее блок формирования испытательных сигналов, один выход которого через блок ввода соединен с первыми входами анализатора и блока синхронизации, вторым входом

подключенного к другому выходу блока формирования испытательных сигналов, а первый выход блока синхронизации соединен с вторьгм входом анализатора, отличающееся тем, что, с целью повыщения эффективности

контроля, в устройство введены блок коммутаторов, блок цифровых .фильтров, преобразователь частоты и блоки обработки, вход синхронизации каждого из которых через преобразователь частоты подключен к второму выходу блока формирования испытательных сигналов, выход анализатора через последовательно соединенные блок коммутаторов и блок цифровых фильтров соединен с выходом устройства, импульсные входы блока коммутаторов соединены с соответствующими выходами блока синхронизации, первый выход которого подключен к входу синхронизации блока цифровых фильтров, входы .и выходы бло.ков обработки соединены с соответствующими в.ходами и выходами устройства.

2. Устройство по п. 1, отличающееся тем, что каждый блок обработки включает триггер, единичный вход которого через последовательно соединенные усилитель-ограничп- тель, схему выделения нулевых пересечений и схему задержки подключен к входу блока, выход триггера соединен с первыми входами двух схем «И, выход первой из .которых через делитель соединен с нулевым входом триггера

и с (первым выходом блока, (выход второй схемы «И соединен с вторым выходом блока, вторые входы схем «И подключены соответственно к входу синхронизации блока и к выходу схемы выделения нулевых пересечений.

. ,

Г

Ue Us

UH

J,0

L. .,

J

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля каналов связи | 1974 |

|

SU544165A2 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| Устройство для испытания регенераторов цифровых систем связи | 1985 |

|

SU1305878A1 |

| Устройство для измерения проскальзываний цифровых сигналов | 1989 |

|

SU1674388A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

Авторы

Даты

1975-01-30—Публикация

1972-07-14—Подача