1

Изобретение относится к области вычислительной техники II может быть использовано ири построен ИИ цифровых вычислительных машин.

Известны MHKpoHporpaMiMiHbie устройства управления, содержащие блок памяти микропрограмм, регистр, генератор тактовых импульсов, дешифратор кода онерации, денгифратор признаков, триггер условных переходов, дешифратор адреса, два входа которого подключены к регистру адреса и генератору тактовых имиульсов, а выход соединен с входом блока памяти микропрограмм. Вход информационного регистра подключен к выходу блока намяти микропрограмм. Выходы признаковых разрядов информационного регистра соединены с входом дешифратора признаков, а выходы операционных разрядов соединены с входом ден:ифратора кода операции. Выводы двух элементов «И соединены с входами регистра адреса. Входы первого элемента «И подключены к единичному выходу триггера условных переходов и выходам адресных разрядов информационного регистра, два входа второго элемента «И нодключены к нервому входу устройства и нулево.му выходу триггера условных переходов. Входы элементов «И первой группы подключепы к выходу дешифратора признаков и второму входу устройства, а выходы соединены с единичным входом триггера условных переходов, выходы элементов «И второй группы соединены с выходом устройства, а первые входы подключены к выходу дешифратора кода операции.

Иедостатком известных устройств является большой объем оборудования.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство содержит триггер совмещения операций, счетный вход которого подключен к выходу разряда совмещения информационного регистра, нулевой вход подключен к единичному выходу триггера условных переходов, а выход соединен со вторым входом элементов «И второй группы и третьим входом второго элемента «И.

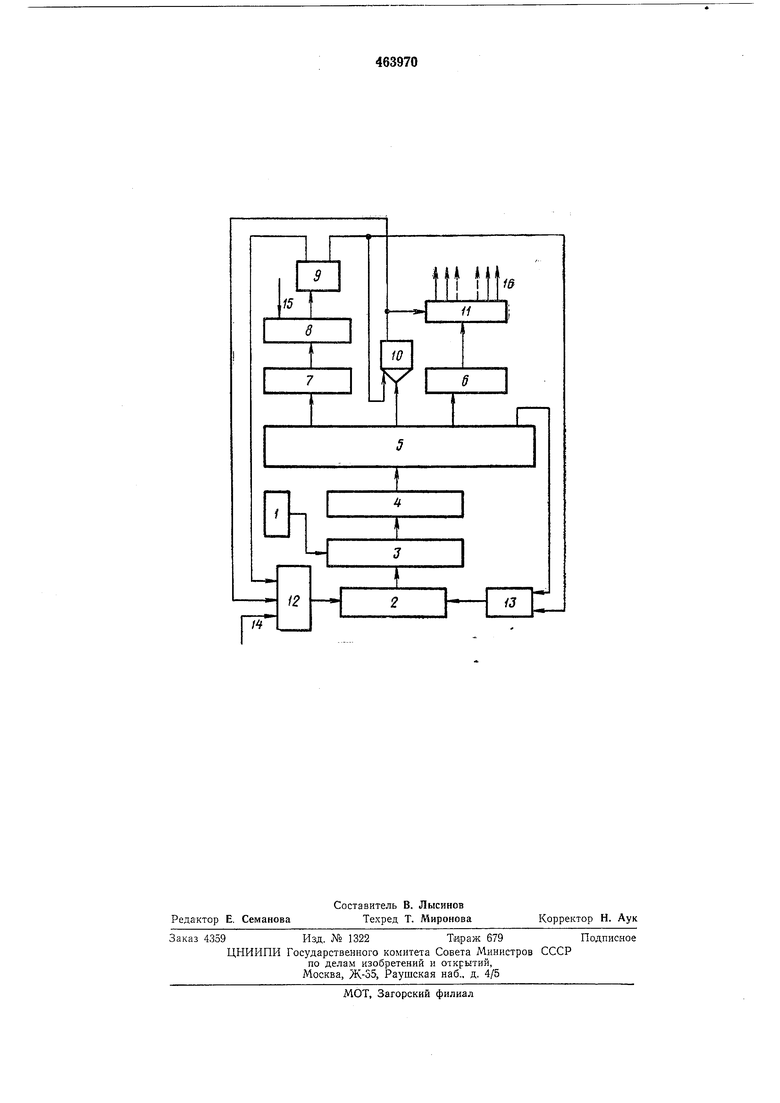

Па чертеже представлена блок-схема предлагаемого устройства.

Оно содержит генератор тактовых импульсов 1, регистр адреса 2, дешифратор адреса 3, блок намяти микропрограмм 4, информационный регистр 5, деншфратор кода операции 6,

дешифратор признаков 7, первую группу элементов «И 8, триггер условных переходов 9, триггер совмещения 10 операций, вторую группу элементов «И 11, элементы «И 12 и 13, входы 14 и 15 устройства и выход 16 устройства.

Устройство работает следующим образом.

Миирокомаяды делятся на два типа. В микрокомандах первого типа возможно совмещение по времени вынолпения данной элементарной операции и анализа признаков. Разряд совмещения в данной микрокосм а нде равен нулю.

В микрокомандах второго типа элементарная операция может вьшолияться только при отсутствий анализируемого признака. Разряд совмещения равен единице.

В блоке памяти микропрограмм 4 для микрокоманды любого типа отводится одна ячейка.

Генератор тактовых импульсов 1 вырабатывает сигналы считывания из блока памяти Микропрограмм 4. Информация, считанная из блока памяти микропрограмм 4 по адресу, установленному в регистре адреса 2, передается в информационный регистр 5. Если считывается микрокоманда первого типа, то в соответствии с кодом операции на выходах 16 формируется сигнал элементарной операции и определяется наличие определенного признака. При наличии признака триггер условных переходов 9 устаиавливается в единицу, и в регистр адреса 2 через элемент «И 13 передается адрес перехода, записанный в адресных разрядах информационного регистра 5. Если признака нет, то к содержимому регистра адреса 2 прибавляется единица через элемент «И 12.

При считывапии макрокоманды второго типа устанавливается в единицу по счетному входу триггер совмещения 10, и тем самым запрещается формирование сигналов элементарных операций на выходе 16. Производится анализ соответствующего признака. Если значение признака равно единице, то устанавливаются в единицу триггер условных переходов 9 и в ноль триггер совмещения 10, а в регистр адреса 2 через элемент «И 13 передается адрес перехода.

При отсутствии признака триггер условных переходов 9 остается в нулевом состоянии, и тем самым блокируется прибавлевие единицы к содержимому регистра адреса 2. Таким образом, в следующем такте в информационный

регистр 5 считывается та.же микрокоманда.

Триггер совмещения 10 устанавливается

по счетному входу в ноль, и вынолнение

микрокоманды аналогично выполнению микрокоманды первого типа.

Предмет изобретения

Микропрограммное устройство управления,

содержащее блок памяти микропрограмм, регистр адреса, генератор тактовых импульсов, дешифратор кода операции, дешифратор призиаков, триггер условных переходов, деншфратор адреса, два входа которого подключены к регистру адреса и генератору тактовых импульсов, а выход соединен с входом блока памяти микронрограмм, информационный регистр, вход которого подключен к выходу блока памяти микропрограмм, выходы

признаковых разрядов информационного регистра соединены с входом дешифратора признаков, а выходы операционных разрядов соединены с входом дешифратора кода операции, два элемента «И, выходы которых соедипены с входами регистра адреса, входы первого элемента «И подключены к единичному выходу триггера условных переходов и выходам адресных разрядов информационного регистра, два входа второго элемента «И

подключены к первому входу устройства и нулевому выходу триггера условных переходов, две группы элементов «И, входы элементов «И первой группы подключены к выходу дешифратора признаков и второму входу устройства, а выходы соединены с единичным входом триггера условных нереходов, выходы элементов «И второй группы соединены с выходом устройства, а первые входы подключены к выходу дешифратора кода операции, отличающееся тем, что, с целью уменьП1ения объема оборудования, оно содержит триггер совмещения операций, счетный вход которого подключен к выходу разряда совмещения информационного регистра, нулевой

вход подключен к единичному выходу триггера условных переходов, а выход соединен со вторым входом элементов «И второй группы и тр.етьим входом второго элемента «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179339A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

Авторы

Даты

1975-03-15—Публикация

1972-08-28—Подача