ляющих импульсов ti и tz, соответственно, на

шины 12 и 16.

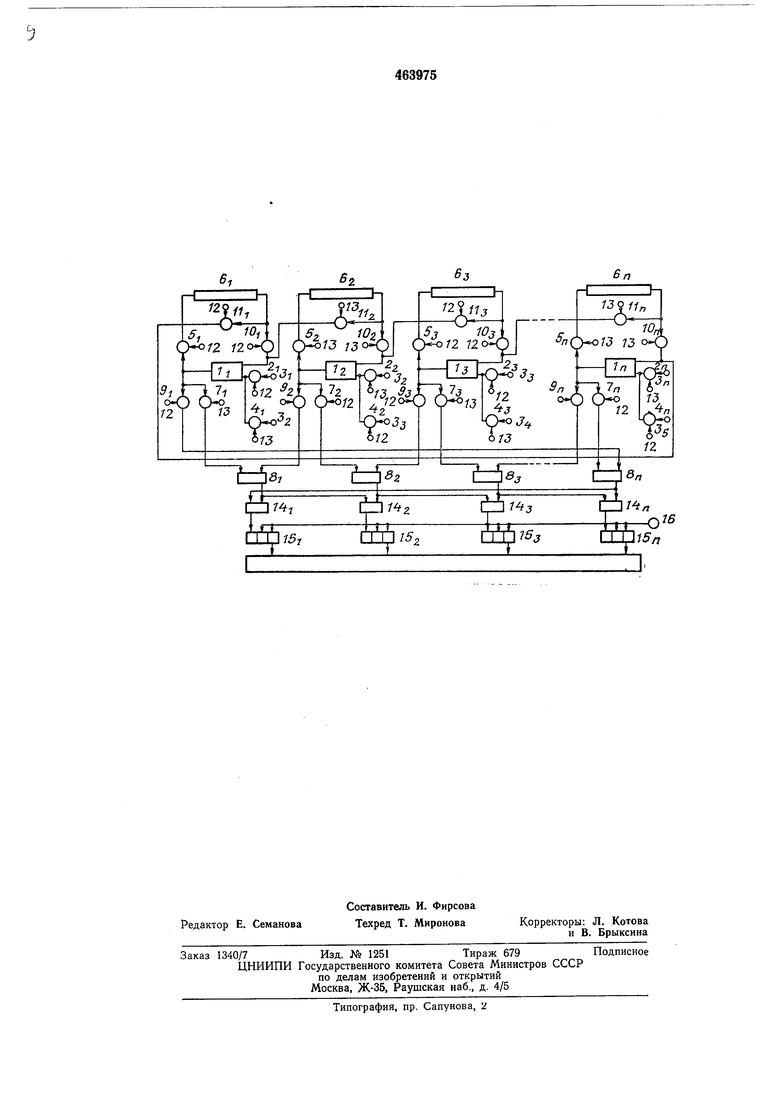

Ьо время действия первого управляющего импульса ti входные данные, соответственно, подаются через ключи 2i, 2,... 2«-i на входы только нечетных процессоров первой группы, а также - в определенные четные процессоры второй группы посредством ключей 2, 44,..., 42п, т. е. входные данные, предназначенные для процессора ij, подаются также и на вход процессора in, данные, поданные на вход процессора д, подаются также и на вход процессора ii+i (, 3,..., /г-1) и т. д.

Ь течение действия второго управляющего импульса 12 входные данные подаются соответственно через ключи 2, 2,..., 2п на входы только четных процессоров 1 второй группы, а также - в соответствующие нечетные процессоры посредством ключей 4i, 4з,..., .

Регистры bi-6и состоят из подрегистров, количество которых определяется фазностью регистров, например восемь подрегистров. 1Чоммутация подрегистров нечетных регистров DI, Ьз,..., bn-i со входами и выходами соответствующих -процессоров h, 1з In-i производится последовательностью импульсов равной длительности (), общая длительность которой равна 2- Каждый подрегистр на соответствующем такте (1, 5, Ь 15) осуществляет вместе с соответствующим процессором обраоотку информации и контроль функционирования его на каждом из тактов управляющего импульса ti. Выходные данные соседних процессоров попарно (1 и 2, 2 и 3...,л и 1} подаются на входы соответствующих компараторов 8i-8я, которые выдают единичный сигнал в случае, когда результаты, полученные на выходах этих процессоров, оОраоатывающих одну и ту же информацию, не совпадают. Компараторы реализуют логическую функцию «Исключающее ИЛИ. Коммутация подрегистров четных регистров 62, 64,..., 6п со входами и выходами соответствующих процессоров 12, 14,- 1 производится последовательностью импульсов равной длительности (2/8), общая длительность которой составляет 2- Каждый подрегистр на соответствующем такте (2, 4, ...,16) осуществляет как обработку информации, так и контроль функционирования соответствующего четного процессора.

При отказе (ошибке) одного и более процессоров, например процессора 12, появляются на выходах соответствующих пар компараторов единичные сигналы, например на

паре компараторов 8i и 82 за время действий импульсов t и ts,. Соответствующие троичные триггеры 15i-15п, находящиеся в исходном состоянии 100, фиксируют единичные сигналы, например триггеры i5i и 152 переходят в состояние OiO. Но благодаря наличию функциональной связи между выходами компараторов 8i-8 и входами элементов «ИЛИ 14i-14ш триггеры одноименных цепей с отказавшими процессорами фиксируют двойной сигнал, переходя в состояние lui, например триггер 152 фиксирует сигнал от компараторов 8i и 82. Индикатор Г/, получив единичные сигналы от двоичных выходов триггеров 15i-

iQn, опознает неисправный процессор.

Предмет изобретения

Устройство для обработки и контроля данных, содержащее процессоры, первые входы которых соответственно соединены, через первые и вторые ключи с соответствующими щинами ввода информации, выходы процессоров через третьи ключи соответственно соединены со входами регистров сдвига, через четвертые ключи соответственно - с первыми входами компараторов, а также через пятые ключи соответственно - со вторыми входами компараторов, выходы регистров сдвига подключены через шестые ключи ко вторым входам соответствующих процессоров, а также через седьмые ключи - ко вторым входам соответственно предыдущих процессоров, входы первых, третьих, пятых, шестых и седьмых

ключей нечетных процессоров и входы вторых и четвертых ключей четных процессоров подключены к первой управляющей шине, входы вторых, пятых, шестых, третьих и седьмых ключей четных процессоров и входы вторых и четвертых ключей нечетных процессоров подключены ко второй управляющей шине, а также индикатор и триггеры, отличающееся тем, что, с целью упрощения устройства, в него введены элементы «ИЛИ, а

триггеры выполнены с тремя устойчивыми состояниями, причем выходы компараторов соединены с первыми входами соответствующих элементов «ИЛИ, а также соответственно со вторыми входами последующих элементов

«ИЛИ, выходы которых подключены к единичным входам соответствующих триггеров, входы установки «О которых соединены с тактовой шиной, двоичные выходы триггеров соединены с соответствующими входами индикатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для тренировки памяти обучаемого | 1989 |

|

SU1683050A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Устройство для отображения информации | 1987 |

|

SU1429156A2 |

| Селекторный канал | 1973 |

|

SU517019A1 |

Авторы

Даты

1975-03-15—Публикация

1973-11-30—Подача