рой дополнительный элемент И, к второй группе входов которого подключены выходы элемента И, и элемент ИЛИ, к одному из входов которого подключен выход элемента НЕТ, другой вход которого соединен с входом ос- 5 новного счетчика непосредственно и через дополнительный элемент ИЛИ - с выходами элемента И, причем выход основного счетчика соединен с входом регистра сдвига, а выход дополнительного счетчика-с входами ю сброса дешифратора, блока памяти и дополнительного счетчика, а также в него введен дополнительный узел памяти, состоящий из последовательно соединенных элемента И, входы которого соединены с выходами гене- 15 ратора, дешифратора и счетчика соответственно, элемента памяти, на второй вход которого подан информационный сигнал, а на третий - тактовые импульсы, первый вентиль, к второму входу которого подключен один из 20 выходов триггера, и элемент ИЛИ, второй вход которого подключен к другому входу триггера через второй вентиль, к другому входу которого подключен выход элемента НЕТ, при этом к входам триггера подключены 25 выходы элемента памяти и второй вход элемента НЕТ соответственно.

В таком устройстве информация, которая в известном устройстве терялась до вхождения в синхронизм, теперь запоминается и, зо когда синхронное состояние найдено, считывается.

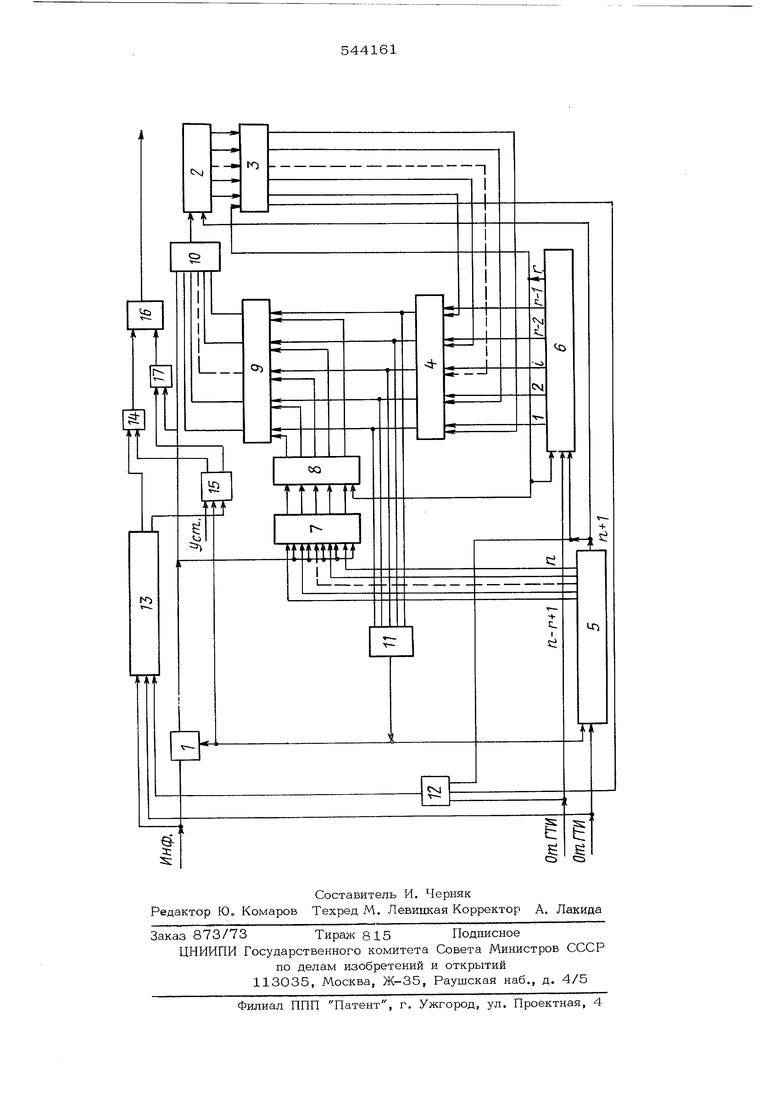

На чертеже представлена структурная электрическая схема устройства.

Устройство фазирования аппаратуры пере-35 дачи информации циклическим кодом содержит на входе элемент НЕТ 1 и последовательно соединенные регистр сдвига 2, дешифратор 3, элемент И 4, одна группа входов которого соединена с выходом основного счетчика 5 40 через дополнительный счетчик 6, а другие выходы основного счетчика 5 подключены к входу регистра сдвига 2 через последовательно соединенные первый дополнительный элемент И 7, к второй группе входов кото- 45 рого подключен выход элемента НЕТ 1, блок памяти 8, второй дополнительный элемент И 9, к второй группе входов которого подключены выходы элемента И, и элемент ИЛИ 10, к одному из входов которого подключен вы- 50 ход элемента НЕТ 1, другой вход которого соединен с входом основного счетчика 5 непосредственно и через дополнительный элемент ИЛИ 11 - с выходами элемента И 4, причем выход основного счетчика 5 соединен 55 с входом регистра сдвига 2, а выход дополнительного счетчика 6 - с входом сброса дешифратора 3, блока памяти 8 и дополнительного счетчика 6; кроме того, устройство содержит дополнительный узел памяти, состоя-60

щий из последовательно соединенных элемента И 12, входы которого соединены с выходми генератора (ГТИ), дешифратора 3 и основного счетчика 5 соответственно, элемента памяти 13, на второй вход которого подан информационный сигнал, а на третий тактовые импульсы, первый вентиль 14, к второму входу которого подключен один из выходов триггера 15, и элемент ИЛИ 16, второй вход которого подключен к другому входу триггера 15 через второй вентиль 17 к другому входу которого подключен выход элемента НЕТ 1, при этом к выходам триггера 15 подключены выходы элемента памяти 13 и второй вход элемента НЕТ 1 соответственно.

Устройство работает следующим образом.

Для осуществления фазирования информационная последовательность сигналов поступает в регистр сдвига 2 и обрабатывается в нем.

После записи в регистр сдвига 2 последнего разряда делимого в нем фиксируется окончательный остаток или, если комбинация относится к разрешенным кодовым комбинациям, регистр 2 переходит в нулевое состояние.

И -ый импульс основной тактовой частоты f пропускает сигналы с выхода регистра 2 на дешифратор 3.

Последние n-l +i-rn символов запоминаются в блоке памяти 8 при совпадении в элементе И 7 соответствующих тактовых импульсов с основного счетчика 5 разрядов и информационных символов, поступающих через элемент НЕТ 1, который находится в разрешающем состоянии.

В зависимости от того, на каких выходах дешифратора 3 i-4 появляется сигнал, в регистр сдвига 2 записываются в качестве первых символов и-i т п -ый символы, поступающие через второй дополнительный элемент И 9 с соответствующими импульсами с дополнительного счетчика 6, которые проходят через элемент И 4.

Необходимое количество тактовых импульсов с дополнительного счетчика 6 через элемент И 4 и элемент ИЛИ 10 записывается также в основной счетчик 5. В это же время элементом НЕТ 1 осуществляется запрет прохождения информационных символов на регистр 2.

h -ый символ с дополнительного счетчика 6 сбрасывает регистр 2 на нуль, а также переводит блок памяти 8 и дешифратор 3 в нулевое состояние.

На регистр сдвига 2 поступают следующие символы информационной последовательности из канала связи, т.е. на регистр сдвига 2 поступают -i последних символа предыдущей комбинации и п-ч символа следующей. Поступившее ц -поэлементное слово анализируется таким же образом, как описано выше на остаток.

Как только остаток, записанный после

проверки в регистре 2, становится равным нулю и ни на одном из выходов дешифратора 3 не будет появляться сигнал, схема войдет в синхронное состояние.

Таким образом, за счет запоминания СИМволов предшествующих комбинаций и использования этих символов при проверке следующей комбинации, уменьшается число проверяемых информационных символов до вхождения в синхронизм по сравнению с прототипом.

Одновременно с осуществлением поиска синхронного состояния устройство осуществляет запоминание поступающей информационной последовательности в элементе памяти 13.

Как только на выходе регистра сдвига 2 появится нулевой остаток, с нулевого выхода дешифратора 3 на элемент И 12 поступит сигнал. Сюда же поступает импульС основного счетчика 5 (этот импульс формируется между задним фронтом h -ого импульса и передним первого импульса счетчика 5

В результате этого на элемент памяти 13 поступит дополнительная тактовая частота, и записанная в элементе памяти 13 информация будет считываться со скоростью дополнительной тактовой частоты и поступат через вентиль 14 и элемент ИЛИ 16 на декодер.

Триггер 15 устанавливается начальным импульсом сброса в такое состояние, чтобы на декодер поступила информация из элемента памяти 13, т.е. вначале состояние триггера 15 соответствует режиму вхождения в синхронизм.

При опросе последней ячейки элемента памяти 13 триггер 15 перебрасывается в противоположное состояние, т.е. в режим синхронной работы, и через второй вентиль 17 и элемент ИЛИ 16 поступает информация непосредственно из канала связи.

Как только синхронное состояние нарушит ся, триггер 15 перейдет в режим вхождения в синхронизм.

Таким образом, предлагаемое устройство фазирования информации работает без потери информационных комбинаций, необходимых дл вхождения в синхронизм.

Благодаря этому, можно осуществить фазирование непосредственно по передаваемой информационной последовательности и более рационально использовать канал связи,

Формула изобретения

1.Устройство фазирования аппаратуры передачи информации циклическим кодом, содержащее на входе элемент НЕТ и последовательно соединенные регистр сдвига, деширатор, элемент И, одна группа входов которого соединена с в{ 1ходом основного счетчика, отличающееся тем, что.

с целью уменьшения времени вхождения в синхронизм, в него введены дополнительный счетчик, блок памяти, дополнительные первый и второй элементы И и ИЛИ, при это.м между упомянутым выходом основного счетчика и второй группой входов элемента И включен дополнительный счетчик, а другие выходы основного счетчика подключены к входу регистра сдвига через последовательно соединенные первый дополнительный элемент И, к второй группе входов которого подключен выход элемента НЕТ, блок памяти, второй дополнительный элемент И, к второй группе входов которого подключены выходы элемента И, и элемент ИЛИ, к одному из входов которого подключен выход элемента НЕТ, другой вход которого соединен с входом основного счетчика непосредственно и через дополнительный элемент ИЛИ - с выходами элемента И, причем выход основного счетчика соединен с входом регистра сдвига, а выход дополнительного Счетчика - с входами сброса дешифратора, блока памяти и дополнительного счетчика.

2.Устройство поп. 1, отлича ющ е е с я тем, что в него введен дополнительный узел памяти, состоящий из последовательно соединенных элемента И, входы которого соединены с выходахп генератора, дешифратора и счетчика соответственно, элемента памяти, на второй вход которого подан информационный сигнал, а на третий тактовые импульсы, первый вентиль, к второму входу которого подключен один из выходов триггера, и элемент ИЛИ, второй вхо которого подключен к другому входу триггера через второй вентиль, к другому входу которого подключен выход элемента НЕТ, при этом к входам триггера подключены выходы элемента памяти и второй вход элемента НЕТ соответственно.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР

№ 316204, М. Кл. Н O4L 1/10, 1968

2.Авторское свидетельство СССР

№ 465748, М. Кл. Н О4 L 27/14, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ фазирования при передаче информации циклическим кодом | 1973 |

|

SU465748A1 |

| Устройство для фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU478450A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU658771A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

Авторы

Даты

1977-01-25—Публикация

1974-10-29—Подача