(54) УСТРОЙСТВО ДЛЯ ПЕРВИЧНОЙ ОБРАБОТКИ

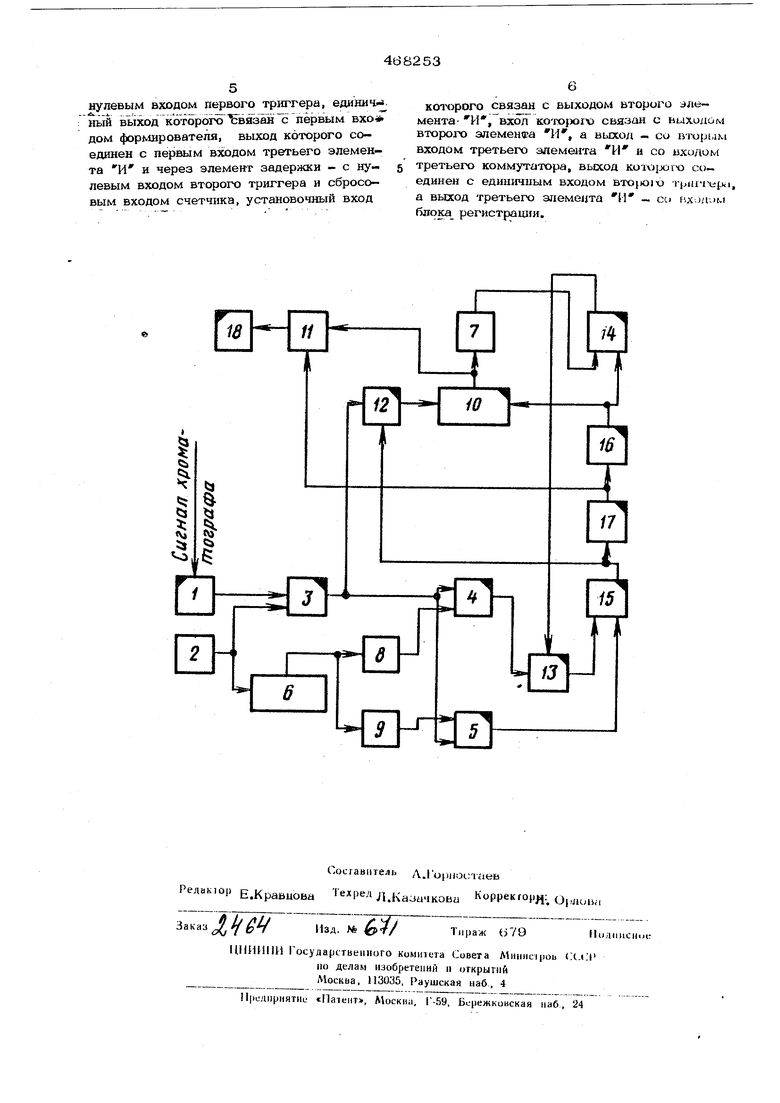

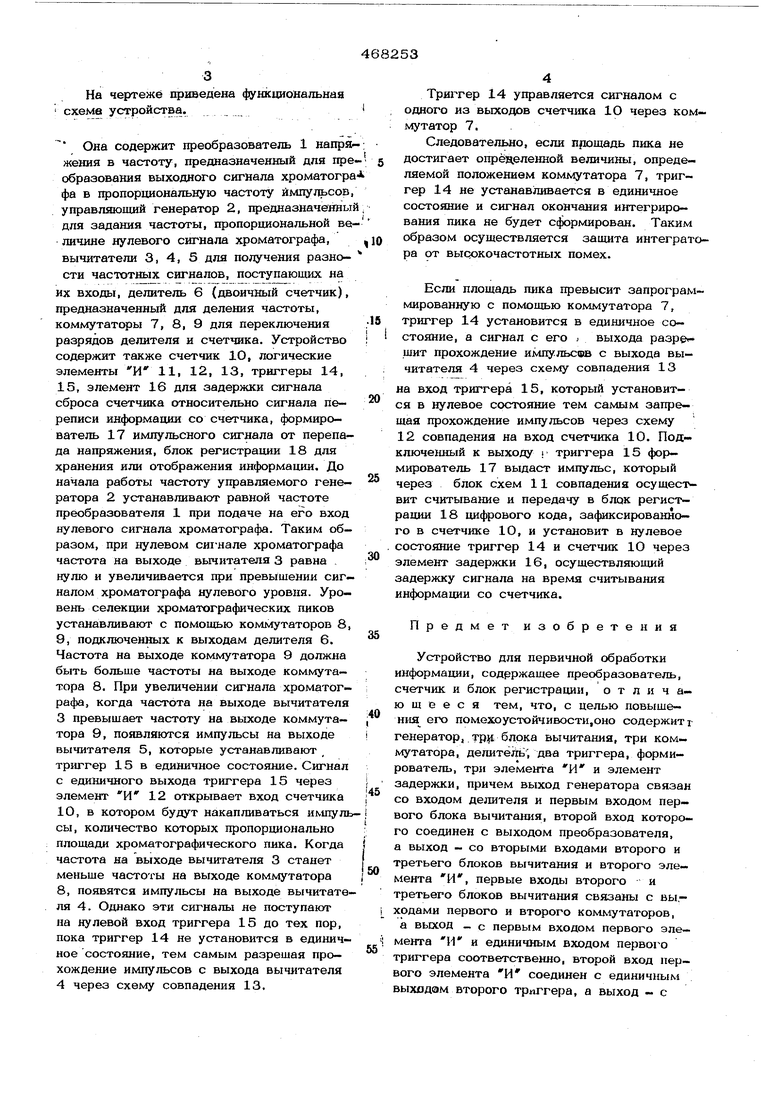

ИНФОРМАЦИИ На чертеже приведена функциональная схеме устройства. Она содержит преобразователь 1 напря жения в частоту, предназначенный дпя пре образования выходного сигнала хроматогра фа в пропорциональную частоту импульсов управляющий генератор 2, предназначенны для задания частоты, пропорциональной ве личине нулевого сигнала хроматографа, вычитатели 3, 4, 5 для получения разности частотных сигналов, поступающих на их входы, делитель 6 (двоичный счетчик), предназначенный для деления частоты, коммутаторы 7, 8, 9 для переключения разрядов делителя и счетчика. Устройство содержит также счетчик 10, логические элементы И 11, 12, 13, триггеры 14, 15, элемент 16 для задержки сигнала сброса счетчика относительно сигнала переписи информации со счетчика, формирователь 17 импульсного сигнала от перепада напряжения, блок регистрации 18 для хранения или отображения информации. До начала работы частоту управляемого генератора 2 устанавливают равной частоте преобразователя 1 при подаче на его вход нулевого сигнала хроматографа. Таким образом, при нулевом сиг-нале хроматографа частота на выходе вычитателя 3 равна . нулю и увеличивается при превышении сигналом хроматографа нулевого уровня. Уровень селекции хроматографических пиков устанавливают с помощью коммутаторов 8, 9,подключенных к выходам делителя 6. Частота на выходе коммутатора 9 должна быть больше частоты на выходе коммутатора 8. При увеличении сигнала хроматографа, когда частота на выходе вычитателя 3превышает частоту на выходе коммутатора 9, появляются импульсы на выходе вычитателя 5, которые устанавливают Tpiarep 15 в единичное состояние. Сигнал с единичного выхода триггера 15 через элемент И 12 открывает вход счетчика 10,в котором будут накапливаться икшуль сы, количество которых пропорционально площади хроматографического пика. Когда частота на выходе вычитателя 3 станет меньше частоты на выходе коммутатора 8, появятся импульсы на выходе вычитате ля 4. Однако эти сигналы не поступают на нулевой вход триггера 15 до тех пор, пока триггер 14 не установится в единич- ное состояние, тем самым разрешая прохождение импульсов с выхода вычитателя 4через схему совпадения 13. Триггер 14 управляется сигналом с одного из выходов счетчика 1О через коммутатор 7. Следовательно, если П|ющадь пика не достигает определенной величины, определяемой положением коммутатора 7, триггер 14 не устанавливается в единичное состояние и сигнал окончания интегрирования пика не будет сформирован. Таким образом осуществляется защита интегратора от высокочастотных помех. Если площадь пика превысит запрограммированную с помощью коммутатора 7, триггер 14 установится в единичное состояние, а сигнал с его выхода разре шит прохождение импульсшв с выхода вычитателя 4 через схему совпадения 13 на вход триггера 15, который установится в нулевое состояние тем самым запрещая прохождение импульсов через схему 12 совпадения на вход счетчика 10. Подключе1шый к выходу i триггера 15 формирователь 17 выдаст импульс, который через блок схем 11 совпадения осуществит считывание и передачу в блок регистрации 18 цифрового кода, зафиксированного в счетчике 10, и установит в нулевое состояние триггер 14 и счетчис 10 через элемент задержки 16, осуществл5пощий задержку сигнала на время считывания информации со счетчика. Предмет изобретения Устройство для первичной обработки информации, содрржащее преобразователь, счетчик и блок регистрации, отличающееся тем, что, с целью повыше- Н1Ш его помехоустойчивости.оно содержитг генератор, тр блока вычитания, три коммутатора, делитель; два триггера, формирователь, три элемента И и элемент задержки, причем выход генератора связан со входом делителя и первым входом первого блока вычитания, второй вход которого соединен с выходом преобразователя, а выход - со вторыми входами второго и третьего блоков вычитания и второго элемента И, первые входы второго и третьего блоков вычитания связаны с выходами первого и второго коммутаторов, а выход с первым входом первого элемента И и единичным входом первого триггера соответственно, второй вход первого элемента И соединен с единичным выходом второго триггера, а выход - с

нулевым входом первого триггера, единиЧя.

- л.v, :, , ,...1. .......... -яг

ный выход которого связан с первым вхо дом фор{ шрователя, выход которого соединен с первым входом третьего элемента И и через элемент задержки - с нулевым входом второго триггера и сбросовым входом счетчика, установочный вход

которого связан с выходом второго элемента- И, вхол ко1Х){югх) связан с выходом

второго элемента И

, а выход - со Bixjpi.iM И входом третьего элемента

и со ьхо/юм

5 третьего коммутато{.)а, выход .ю1чэ соединен с единичным входом rpinuxij.i.i, а выход третьего элемента И со Eix;Jn-,i блока регистрашш.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для первичнойОбРАбОТКи иНфОРМАции | 1978 |

|

SU809188A1 |

| Устройство для контроля родовой деятельности | 1988 |

|

SU1605259A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Устройство для вычисления дисперсии случайного процесса | 1981 |

|

SU1029183A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

Авторы

Даты

1975-04-25—Публикация

1973-08-21—Подача