(54) УСТРОЙСТВО ДЛЯ ПЕРВИЧНОЙ ОБРАБОТКИ ЙНФОР/ПАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство первичной обработки информации | 1973 |

|

SU468253A1 |

| Устройство для ввода информации | 1979 |

|

SU842769A1 |

| Устройство для интегрированияпиКООбРАзНыХ фуНКций | 1978 |

|

SU813453A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для измерения вихрево-гО КОМпОНЕНТА СКОРОСТи пОТОКА | 1979 |

|

SU822038A1 |

I

Изобретение относится к вычислительной технике и может быть использовано в научноисследовательских лабораториях, на предприятиях химической, нефтехимической, нефтеперерабатывающей и других отраслей промышленности. Устройство предназначено для интегрирования получаемых на выходе анализатора сигналов, имеющих форму пиков (сигналы хромотографов, масспектрометров, спектрофотометров и т. п.) и может использоваться как автономно (для уменьщения ручного труда при расчете количественного состава анализируемых смесей), так и в комплекте с УВМ (при полной автоматизации обработки результатов анализа).

Известны устройства для первичной обработки информации, одно из которых содержит преобразователь, счетчик, блок регистрации, генератор, три блока вычитания, три коммутатора, делитель, два триггера, формирователь, три элемента И и элемент задержки 1 и 2. В известном устройстве приняты специальные меры по повыщению пдмехозащищенности только селектора (схемы, формирующей сигналы начала и конца интегрируемого пика).

Недостаток известного устройства заключается в слабой помехозащищенности интегрирующего счетчика и недостаточной точности интегрирования полезного сигнала, обусловленный тем, что в промежутке между моменто м окончания предыдущего пика и началом последующего пика в счетчике осуществляется интегрирование высокочастотных (по сравнению с частотой полезных сигналов) помех. Накопленные за этот промежуток времени импульсы затем суммируются с полезным сигналом и тем самым увеличивают погрещность интегрирования полезного сигнала.

Цель изобретения - повыщение точности и помехозащищенности устройства.

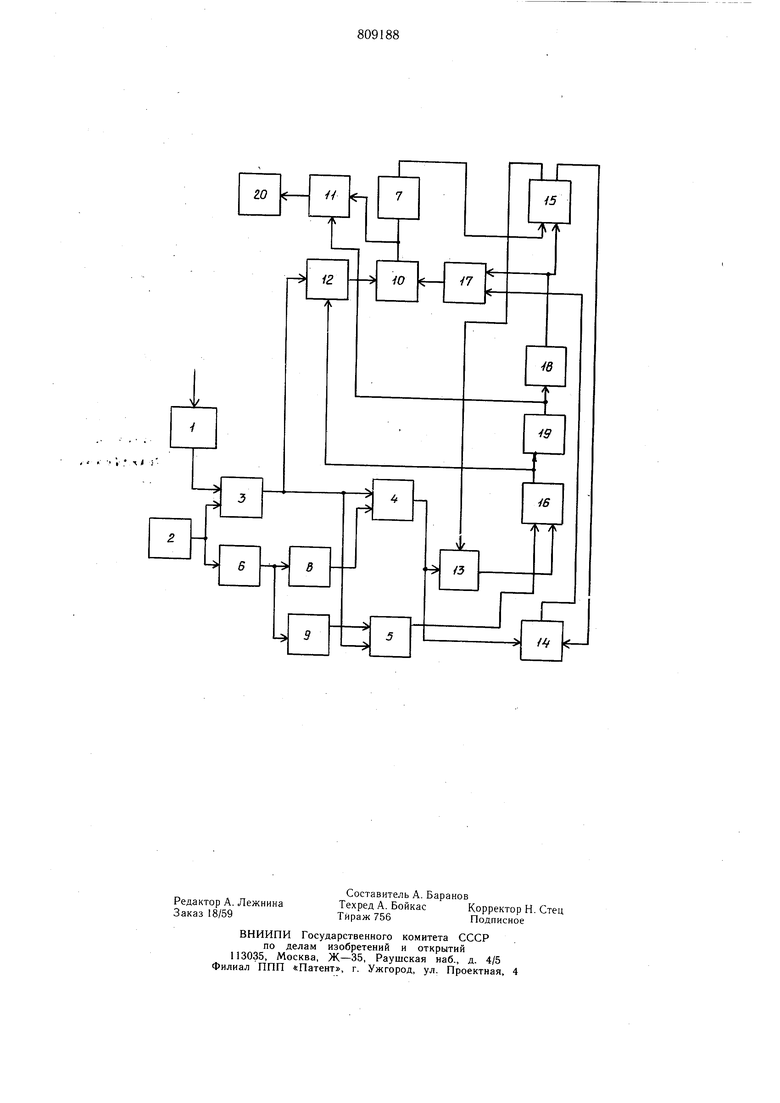

Указанная цель достигается тем, что в устройство, содержащее генератор импульсов, три вычитателя, три коммутатора, блок регистрации, формирователь импульсов, два счетчика, три элемента И, два триггера, элемент задержки и преобразователь напряжения в частоту, выход которого соединен с первым входом первого вычитателя, выход которого соединен с первым входом первого элемента И и первыми входами второго и третьего вычитателей, выходы которых подключены соответственно к первым входам второго элемента И и первого триггера, выход которого соединен со вторым входом первого элемента И и входом формирователя импульсов, выход которого подключен к первому входу третьего элемента И и входу элемента задержки, выход которого соединен с первым входом второго триггера, первый выход которого подключен ко второму входу второго элемента И, выход генератора импульсов соединен со вторым входом первого вычитателя и входом первого счетчика, выход которого подключен ко входам первого и второго коммутаторов, выходы которых подключены ко вторым входам второго и третьего вычитателей, выход первого элемента И соединен с первым входом второго счетчика, выход которого соединен со вторым входом третьего элемента И и входом третьего коммутатора, выход которого соединен со вторым входом второго счетчика, выход третьего элемента И соединен со входрм блока регистрации, а вход преобразователя напряжения в частоту является входом устройства, введены элемент ИЛИ и четвертый элемент И, причем выход второго вычитателя соединен с первым входом четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен ко второму входу второго счетчика, второй выход второго триггера соединен со вторым входом четвертого элемента И, выход элемента задержки соединен со вторым входом элемента ИЛИ, а выход второго элемента И подключен ко второму входу первого триггера. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит преобразователь 1 напряжения в частоту импульсов, предназначенный для преобразования выходного сигнала анализатора в пропорциональную частоту импульсов, управляемый генератор 2 импульсов, предназначенный для задания частоты, пропорциональной величине базисного сигнала анализатора, вычитатели 3 - 5 для получения разности частотных сигналов, поступающих на их входы, двоичный счетчик (делитель) 6, предназначенный для деления частоты, коммутаторы 7 - 9 для переключения разрядов делителя (счетчика). Устройство содержит также счетчик 10, логические элементы И 11 - 14, триггеры 15 и 16, элемент ИЛИ 17, элемент 18 задержки сигнала переписи информации со счетчика, формирователь 19 импульсов, блок 20 регистрации для хранения или отображения информации. Устройство работает следующим образом. До начала работы частоту управляемого генератора 2 устанавливают равной частоте преобразователя 1 при подаче на его вход базисного сигнала анализатора. Таким образом, при базисном смгнаДе анализатора частота на выходе вычитателя 3 равна нулю и увеличивается при превышении сигналом анализатора уровня базисного сигнала. Уровень селекции пиков устанавливают с помощью коммутаторов 8 и 9, подключенных к выходам счетчика 6. Частота на выходе коммутатора 9 должна быть больше частоты на выходе коммутатора 8. При увеличении сигнала анализатора, когда частота на выходе вычитателя 3 превышает частоту на выходе коммутатора 9, появляются импульсы на выходе вычитателя 5, которые устанавливают триггер 16 в единичное состояние. Сигнал с единичного выхода триггера 16 через элемент И 12 открывает вход счетчика 10, в котором накапливаются импульсы, количество которых пропорционально интегралу входного сигнала устройства. Когда частота на выходе вычитателя 3 становится меньше частоты на выходе коммутатора 8, появляется импульс на выходе вычитателя 4. Однако эти сигналы не поступают на нулевой вход триггера 16 до тех пор, пока триггер 15 не устанавливается в единичное состояние, тем самым разрешая прохождение импуль.сов с выхода вычитателя 4 через элемент и13. В то же время сигнал с выхода вычитателя 4 проходит через элемент И 14 (так как на второй его вход подается разрешающий сигнал с нулевого плеча триггера 15), элемент ИЛИ 17 и устанавливает счетчик 10 в нулевое состояние. Триггер 15 устанавливается в единичное состояние сигналом с одного из выходов счетчика 10 через коммутатор 7. Следовательно, если интеграл пика не достигает определенной величины, определяемой положением коммутатора 7, триггер 15 не устанавливается в единичное состояние и сигнал окончания интегрирования пика не сформируется, а счетчик 10 сигналом с элемента И 14 устанавливается в нулевое состояние, при этом фиксируемое счетчиком число импульсов представляет собой высокочастотные помехи. При интегрировании полезного сигнала, интеграл которого превышает интеграл помехи, триггер 15 сигналом с коммутатора 7 устанавливается в единичное состояние, разрешая прохождение сигнала конца интегрирования через элемент И 13 на нулевой ВХОД триггера 16. При этом сигналом с единичного плеча триггера 16 вход счетчика 10 закрывается. При переходе триггера 16 из единичного состояния в нулевое на выходе формирователя 19 импульсов появляется импульс, который через элемент И 11 переписывает содержимое счетчика 10 в блок 20 регистрации, а затем, пройдя через элемент 18 задержки, уста-навливает счетчик 10 в нулевое состояние. Таким образом, повышение точности интегрирования сигналов анализаторов достигается за счет того, что интегральные значения помех не суммируются с полезным сигналом. Минимальное допусти.мое значение (интегральное) полезного сигнала устанавливается с помощью коммутатора 7. Если интегральное значение сигнала на входе анализатора не достигает этого значения,то но окончании интегрирования. пикового сигнала через элемент И 14 и ИЛИ 17 осуществляется установка счетчика 10 в нулевое положение. Это исключает возможность накопления сигналов помех в счетчике 10 и суммирования их с полезным .сигналом и, таким образом, повышает помехозащищенность устройства в интервале между двумя соседними пиками полезных сигналов. При этом точность интегрирования полезных сигналов увеличивается в десятки раз, а помехозащищенность устройства. характеризуемая отнощением полезного сигнала к помехе, достигает 0,8-0,9. Формула изобретения Устройство для первичной обработки информации, содержащее генератор импульсов, три вычитателя, три коммутатора, блок регистрации, формирователь импульсов, два счетчика, три элемента И, два триггера, элемент задержки и преобразователь напряжения в частоту, выход которого соединен с первым входом первого вычитателя, выход которого соединен с первым входом первого элемента И и первыми входами второго и третьего вычитателей, выходы которь1х подключены соответственно к первым входам второго.элемента И и первого триггера, выход которого соединен со вторым входом первого элемента И и входом формирователя импульсов, выход которого подключен к первому входу третьего элемента И и входу элемента задержки, выход которого соединен с первым входом второго триггера, первый выход которого подключен i;o второму входу второго элемента И, выход генератора импульсов соединен со вторым входом первого вычитетеля и входом первого счетчика, выход которого подключен ко входам первого и второго коммутаторов, выходы которых подключены ко вторым входам второго и третьего вычитателей, выход первого элемента И соединен с первым входом второго счетчика, выход которого соединен со вторым входом третьего элемента И и входом третьего коммутатора, выход которого соединен со вторым входом второго счетчика, выход третьего элемента И соединен со входом блока регистрации, а вход преобразователя напряжения в частоту является входом устройства, отличающееся тем, что, с целью повышения точности и помехозащищенности, в него введены элемент ИЛИ и четвертый элемент И, причем выход второго вычитателя соединен с первым входом четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен ко второму входу второго счетчика, второй выход второго триггера соединен со вторым входом четвертого элемента И, выход элемента задержки соединен со вторым входом элемента ИЛИ, а выход второго элемента И подключен ко второму входу первого триггера. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 378833, кл. G 06 F 3/04, 1970. 2.Авторское свидетельство СССР № 468253, кл. G 06 F 15/00, 1973 (прототип). . t :

Авторы

Даты

1981-02-28—Публикация

1978-08-07—Подача