(54) ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ | 1970 |

|

SU269600A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1971 |

|

SU293300A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Двоичный счетчик импульсов с контролем ошибок | 1977 |

|

SU687601A1 |

| Селектор импульсов по длительности | 1979 |

|

SU813760A1 |

| Устройство для проведения телевизионных игр | 1984 |

|

SU1205921A1 |

| ДВОИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1971 |

|

SU301858A1 |

Изобретение относится к радиотехнике и может быть использовано в устройствах вычислительной техники.

Известен двоичный счетчик импульсов с контролем ошибок, содержащий разрядные пе ресчетные ячейки на двух триггерах и:, вентилях записи, входную шину единичного сигнала и выходную шину контрольного счетчика.

Однако известное устройство обладает низкой достоверностью работы и не дает возможности определения места неисправности.

Целью изобретения является повышение достоверности работы счетчика и определение места неисправности.

Для этого в нем дополнительно установлены схема задержки, формирователь и общая схема совпадения, а в каждом разряде счетчика установлены транзисторный каскад сравнивающая схема, два инвертора и две схемы совпадения, причем вход счетчика соединен с вентилями записи одного триггера каждой пересчетной ячейки, с одним входом формирователя и входом схемы задержки, выход которой подключен к вентилям записи другого триггера каждой пересчетной ячейки и к другому входу формирователя, выход которого соединен с эмиттерным входом транзисторного каскада первой пересчетной ячейки, выходы двух триггеров каждой пересчетной ячейки соединены со сравнивающей схемой этой же ячейки, выхо которой подключен к одному входу одной схемы совпадения и одному инвертору, выход которого подключен к одному входу другой схемы совпадения, выходы обеих схем совпадения соединены с входами

общей схеглы совпадения, выход которой подсоединен к выходной шине контроля

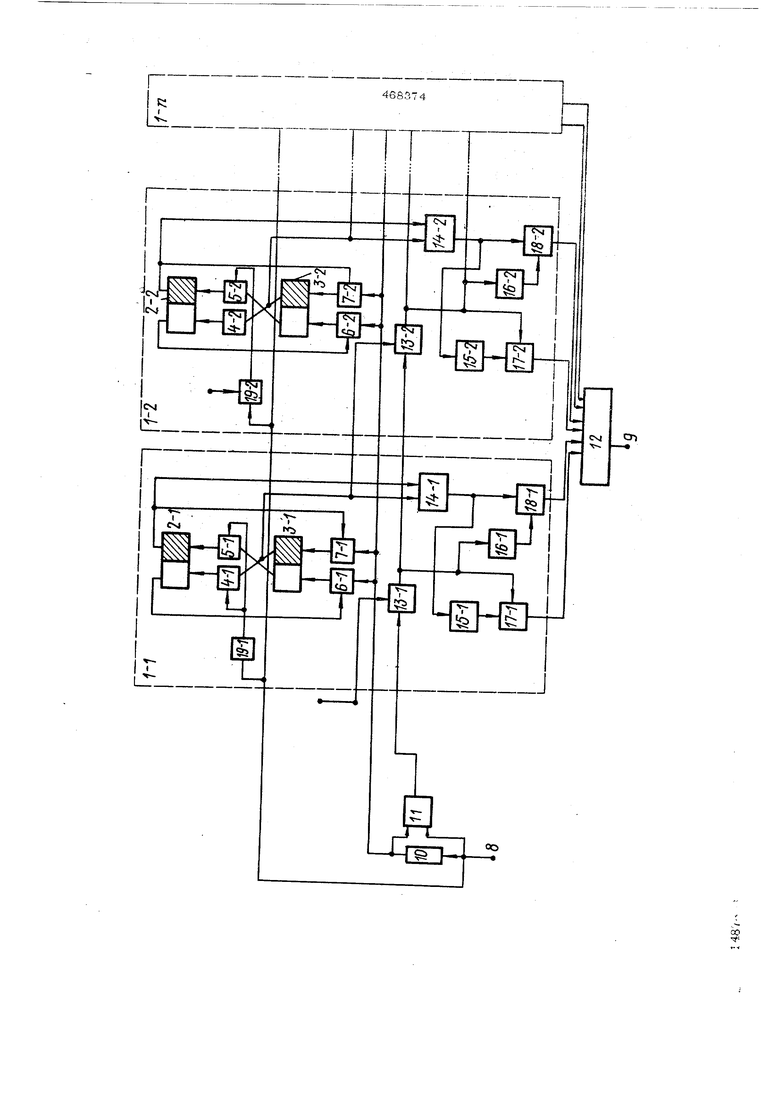

счетчика, вторые входы одной и другой схем совпадения соответственно через другой инвертор и непосредственно соединены с коллекторным выходом транзисторного каскада, соединенным с эмиттерным входом транзисторного каскада последующего разряда, базовые входы транзисторных каскадов всех пересчетных ячеек, кроме первой, соединены с выходом другого триггера предыдущей пересчетной ячейки, а базовый вход транзисторного каскада первой пересчетной ячейки соединен с входной ш единичного . На чертеже приведена блок-схема устройства. Двоичный счетчик импульсов содержит разрядные пересчетные ячейки 1-1 - 1- П на триггерах 2-1 - 2- П и 3-1 - 3- п вентилях 4-1 - 4- П , 5-1 - 5-tV , 6-1 -6 п и - 7-П , входную шину еди ничного сигнала 8 и выходную шину контр ля 9 счетчика. На чертеже ячейки 1- п. не раскрыта, показано только две ячейки - 1-1 и 1-2. В двоичный счетчик импульсов входят также схема задержки 10, формирователь и схема совпадения 12. В разрядных ячейках 1-1 - 1- 11, уста новлены соответственно транзисторные каскады 13-1 - 13-П , сравнивающие схем 14-1 - 14-П , инверторы 15-1 - 15-п 16-1 - 16-п, , схемы совпадения 17-1 17- П , 18-1 - -18-П и инверторыЛЭ19- П . Двоичный счетчик импульсов работает следующим образом. На входную шину 8 поступают импульс счета. Эти импульсы подаются на триггеры 2-1 - 2- Ц , проходят через схему за держки 10 и поступают на триггеры 3-1 3 tl . Импульсы триггеров 2-1 - 2-71 и 3-1 - 3- fl оказьтаются смещенными друг относительно друга. Импульсы с входа и выхода схемы задержки 10 поступают на формирователь 1 вырабатьтающий импульсы, длительность которых равна интервалу между сдвинутыми импульсами. Сигнал с выхода формирователя 11 поступает на эьлиттерный вход транзисторног каскада 13-1. Базовые входы транзисторных каскадов 13-1 - 13-1г соединены с выходами триггеров :.,3-1 - 3--П Транзисторные каскады 13-1 - 13-гг образуют цепочку последовательно соединенных транзисторов, у которых коллектор предыдущего (младшего) каркада (Соединен с эмиттером последующего (старшего) каскада соответствующих пересчетных ячеек 1-1 - 1-а . При действии импульсов записи через инверторы 19-1 - 19-п в зависимости от состояния пересчетных ячеек 1-1 - 1-П в триггеры 2-1 - 2- П записьшаются инверсные состояния триггеров 3-1-З-п . Таким образом, в этот момент в пересчетных ячейках 1-1 - 1-П состояния триггеров должно быть разными. Проверка этоIo обстоятельства осуществляется при помощи сравнивающих схем 14-1 - 14-П При этом с соответствующих транзисторных каскадов 13-1 - 13-Я, поступает нулевой сигнал.который открывает схемы совпадения 17-1 17-71. Если запись в триггеры 2-1 2 71-соответствуюших пересчелных ячеек прошла правильно,то со сравнивающих схем 14-1 - 14-ft снимаются нулевые с5игналы, ,-:огорые через инверторы 15-1 - 15-fl закрызают схемы совпадения 17-1 - 17-1т,. Если при записи возникли ошибки, то с одной или нескольких сравнивающих схем 14-1 - 14-TV снимается единичный сигнал, который проходит через схемы совпадения 17-1 - 17- Н и через схему совпадения 12 поступает на выходную шину контроля 9. Одновременно может быть снята информация с выходов схем совпадения 17-1 - 17- fl . Эта информация позволяет локализовать место возникновения ошибки с точностью до одной пересчетной схемы. Так как записи в триггеры разделены во времени, то правильность записи в триггеры 3-1 - 3- tl производится аналогичным образом. При этом с выходов транзисторных каскадов 13-1 - 13- tV снимается единичный сигнал и производится контроль триггеров. Их состояния должны быть одинаковыми. При одной или нескольких ошибках сигналы со сравнивающих схем 14-1 -14-11 поступают через схемы совпадения 18-1 - 18-tv на схему совпадения 12, а с нее - на выходную щину контроля 9. Предмет изобретения Двоичный счетчик импульсов с контролем ошибок, содержащий разрядные пере- счетные ячейки на двух триггерах и вентилях записи, входную шину единичного сигнала и выходную шину контроля счетчика, отличающийся тем, что, с целью повышения достоверности работы и определения места неисправности счетчика, в нем дополнительно установлены схема задержки, формирователь и общая схема coBnaAOHKHj а в каждом разряде счетчика установлены транзисторные каскады, сравнивающую схему, два инвертора и две схемы совпадения, причем вход счетчика соединен с вентилями записи одного триггера каждой пересчетной ячейки, с одним входом формирователя и входом схемы задержки, выход которой подключен к вентилям записи другого триггера каждой пересчетной ячейки и к крутому входу формирователя, выход которого соединен с эмиттер- ным входом транзисторного каскада первой пересчетной ячейки, выходы двух iTJiirrepOB каждой первсчетной ячейки соединены со сравнивающей схемой этой же ячейки, выход которой подключен к одному входу одной схемы совпадения и одному инвертору, выход которого подключен к одному входу другой схемы совпадения, выходы обеих схем совпадения соединены с входами общей схемы совпадения, выход которой подсоединен к выходной шине контроля счетчика вторые входы одной и другой схем совпадения соответственно через другой инвертор и непосредственно соединены с коллекторным выходом транзисторного каскада, соединенным с эмиттерным входом транзисторного каскада последующего разряда, базовые входы транзисторных каскадов всех пересчетных ячеек, кроме первой, соединены с выходом другого триггера пре10 дьщушей пересчетной ячейки, а базовый вход транзисторного каскада первой пересчетной ячейки соединен с входной шиной единичного сигнала.

I

u

LL

X

П-Ш:

S

csi

ш-ёь

x

I-JH

468374

-J-l

ГТТ

CNJ

T

;i

50

m

CvT

SO

to

CT

Csl

-t

гггГ

r-i

CO

V

Авторы

Даты

1975-04-25—Публикация

1972-01-07—Подача