Изобретение относится к вычислительной технике и, в частности, к проектированию процессоров с контролем.

Известны микропрограммные процессоры с восстановлением при сбоях, содержащие блок регистров, первый выход которого соединен выходной магистралью с первыми входами блока контроля и арифметико-логического блока, второй вход которого соединен со вторым выходом блока регистров, а выход соединен со вторым входом блока контроля, с первым входом регистра адреса микрокоманд, с первым входом блока сопряжения с. оперативной памятью и входной магистралью с первым входом блока регистров, второй вход которого соединен со вторым входом арифметико-логического блока и с первым выходом блока управления, второй выход которого соединен с третьим входом блока контроля, первый выход блока контроля соединен со счетным входом счетчика сбоев, единичный выход старшего разряда которого соединен со вторым входом регистра адреса микрокоманд, выход которого соединен со входами регистра адреса повтора и блока памяти микрокоманд, выход которого соединен со входом регистра микрокоманд, выход регистра микрокоманд соединен со входом блока управления и с четвертым входом блока контроля, второй выход которого соединен m входом

гашения счетчика сбоев, третий выход блока управления соединен со вторым входом блока сопряжения с оперативной памятью, выход которого соединен входной магистралью с первым входом блока регистров.

Однако в известных устройствах восстановление работы при сбоях возможно при выполнении не всех микрокоманд. При выпол-, нении некоторых микрокоманд, размещающих

результат операции на месте исходных данных, восстановление работы но производится и случайный сбой фиксируется как отказ аппаратуры. Это снижает надежность работы. Кроме того, размещение признаков восстановления в микрокоманде увеличивает ее разрядность и приводит к увеличению затрат оборудования в памяти микрокоманд.

Целью настоящего изобретения является сокращение оборудования на восстановление

работы.

Предлагаемый микропрограммный процессор с восстановлением при сбоях отличается от известных тем, что он дополнительно содержит регистр промежуточных результатов

и две группы схем «И, причем первый вход регистра промежуточных результатов соединен с выходом арифметико-логического блока, второй вход - с первым выходом блока управления, а выход - входной магистралью

блока регистров с первым вхопом блока регистров и с пятым входом блока контроля, выход которого соединен с первыми входами первой группы схем «И, вторые входы которых соединены с нулевым выходом старшего разряда счетчика сбоев, третьи входы соединены с выходом регистра адреса повтора, а выходы соединены с третьим входом регистра адреса микрокоманд, второй выход блока контроля соединен с первыми входами второй группы схем «И, вторые входы которых соединены с выходом регистра микрокоманд, а выходы - с четвертым входом регистра адреса микрокоманд.

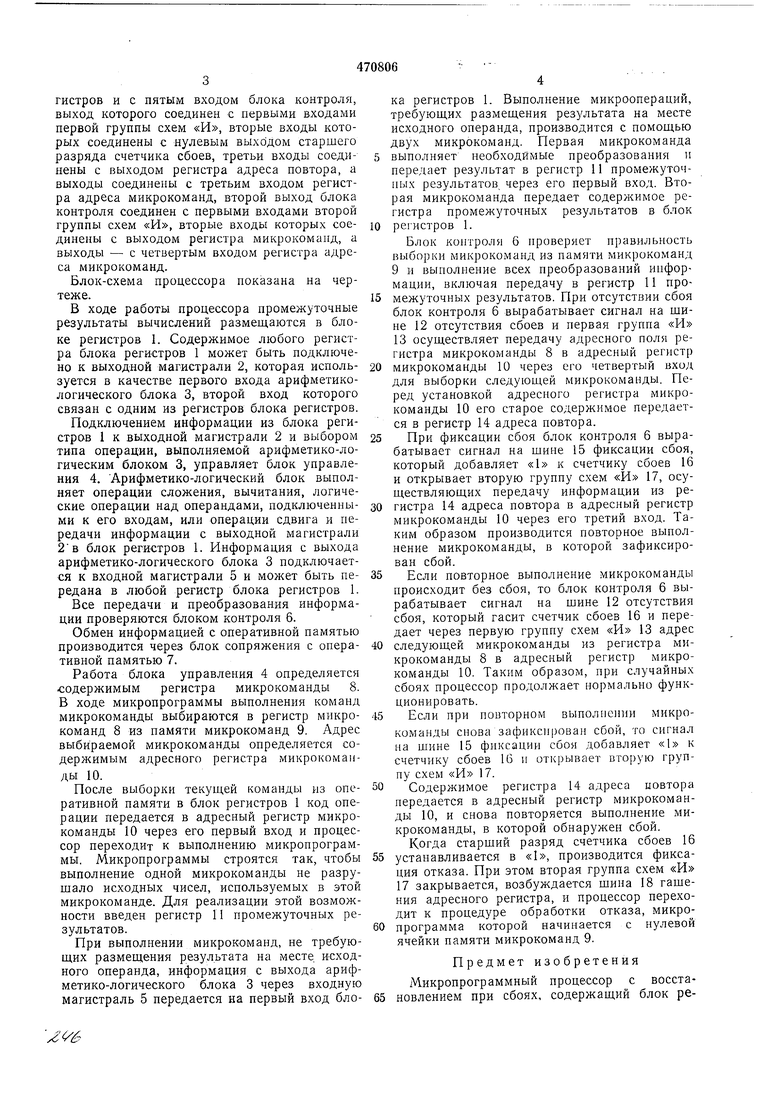

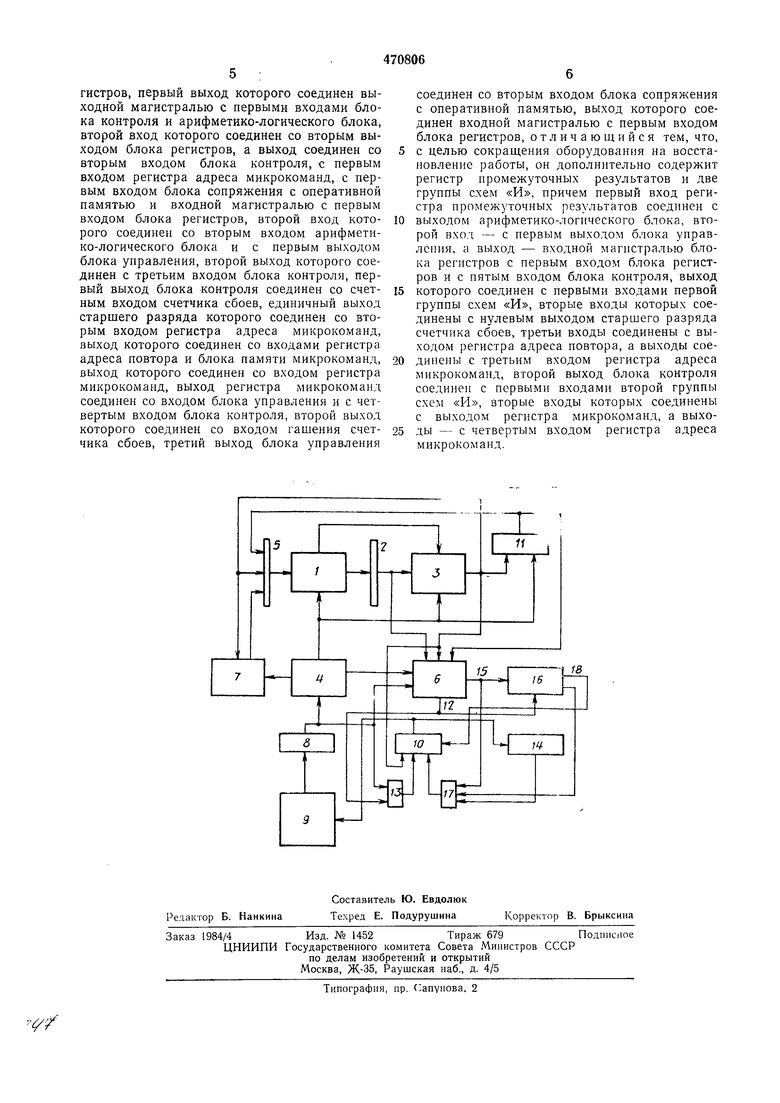

Блок-схема процессора показана на чертеже.

В ходе работы процессора промежуточные результаты вычислений размещаются в блоке регистров 1. Содержимое любого регистра блока регистров 1 может быть подключено к выходной магистрали 2, которая используется в качестве первого входа арифметикологического блока 3, второй вход которого связан с одним из регистров блока регистров.

Подключением информации из блока регистрав 1 к выходной магистрали 2 и выбором типа операции, выполняемой арифметико-логическим блоком 3, управляет блок управления 4. Арифметико-логический блок выполняет операции сложения, вычитания, логические операции над операндами, подключенными к его входам, или операции сдвига и передачи информации с выходной магистрали 2в блок регистров 1. Информация с выхода арифметико-логического блока 3 подключается к входной магистрали 5 и может быть передана в любой регистр блока регистров 1.

Все передачи и преобразования информации проверяются блоком контроля 6.

Обмен информацией с оперативной памятью производится через блок сопряжения с оперативной памятью 7.

Работа блока управления 4 определяется содержимым регистра микрокоманды 8. В ходе микропрограммы выполнения ютманд микрокоманды выбираются в регистр микрокоманд 8 из памяти микрокоманд 9. Адрес выбираемой микрокоманды определяется содержимым адресного регистра микрокоманды 10.

После выборки текущей команды из оперативной памяти в блок регистров 1 код операции передается в адресный регистр микрокоманды 10 через его первый вход и процессор переходит к выполнению микропрограммы. Микропрограммы строятся так, чтобы выполнение одной микрокоманды не разрушало исходных чисел, используемых в этой микрокоманде. Для реализации этой возможности введен регистр 11 промежуточных результатов.

При выполнении микрокоманд, не требующих размещения результата на месте, исходного операнда, информация с выхода арифметико-логического блока 3 через входную магистраль 5 передается на первый вход блока регистров 1. Выполнение микроопераций, требующих размещения результата на месте исходного операнда, производится с помощью двух микрокоманд. Первая микрокоманда выполняет необходимые преобразования и передает результат в регистр 11 промежуточных результатов, через его первый вход. Вторая микрокоманда передает содержимое регистра промежуточных результатов в блок

регистров 1.

Блок ко1ггроля 6 проверяет правильность выборки микрокоманд из памяти микрокоманд 9 и выполнение всех преобразований информации, включая передачу в регистр 11 промежуточных результатов. При отсутствии сбоя блок контроля 6 вырабатывает сигнал на шине 12 отсутствия сбоев и первая группа «И 13 осуществляет передачу адресного поля регистра микрокоманды 8 в адресный регистр

микрокоманды 10 через его четвертый вход для выборки следующей микрокоманды. Перед установкой адресного регистра микрокоманды 10 его старое содержимое передается в регистр 14 адреса повтора.

При фиксации сбоя блок контроля 6 вырабатывает сигнал на шине 15 фиксации сбоя, который добавляет «1 к счетчику сбоев 16 и открывает вторую группу схем «И 17, осуществляющих передачу информации из регистра 14 адреса повтора в адресный регистр микрокоманды 10 через его третий вход. Таким образом производится повторное выполнение микрокоманды, в которой зафиксирован сбой.

Если повторное выполнение микрокоманды происходит без сбоя, то блок контроля 6 вырабатывает сигнал на шине 12 отсутствия сбоя, который гасит счетчик сбоев 16 и передает через первую группу схем «И 13 адрес

следующей микрокоманды из регистра микрокоманды 8 в адресный регистр микрокоманды 10. Такнм образом, при случайных сбоях процессор продолжает нормально функционировать.

Если при повторном выполпенни микрокоманды снова зафиксирован сбой, то сигнал на шнне 15 фиксации сбоя добавляет «1 к счетчнку сбоев 16 и открывает вторую группу схем «И 17.

Содержимое регистра 14 адреса повтора передается в адресный регистр микрокоманды 10, и снова повторяется выполнение микрокоманды, в которой обнаружен сбой. Когда старший разряд счетчика сбоев 16

устанавливается в «1, производится фиксация отказа. При этом вторая группа схем «И 17 закрывается, возбуждается шина 18 гашения адресного регистра, и процессор переходит к процедуре обработки отказа, микропрограмма которой начинается с нулевой ячейки памяти микрокоманд 9.

Предмет изобретения

Микропрограммный процессор с восстановлением при сбоях, содержащий блок регистров, первый выход которого соединен выходной магистралью с первыми входами блока контроля и арифметико-логического блока, второй вход которого соединен со вторым выходом блока регистров, а выход соединен со вторым входом блока контроля, с первым входом регистра адреса микрокоманд, с первым входом блока сопряжения с оперативной памятью и входной магистралью с первым входом блока регистров, второй вход которого соединен со вторым входом арифметико-логического блока и с первым выходом блока управления, второй выход которого соединен с третьим входом блока контроля, первый выход блока контроля соединен со счетным входом счетчика сбоев, единичный выход старшего разряда которого соединен со вторым входом регистра адреса микрокоманд, выход которого соединен со входами регистра адреса повтора и блока памяти микрокоманд, выход которого соединен со входом регистра микрокоманд, выход регистра микрокоманд соединен со входом блока управления и с четвертым входом блока контроля, второй выход которого соединен со входом гашения счетчика сбоев, третий выход блока управления

соединен со вторым входом блока сопряжения с оперативной памятью, выход которого соединен входной магистралью с первым входом блока регистров, отличающийся тем, что, с целью сокращения оборудования на восстановление работы, он дополнительно содержит регистр промежуточных результатов и две группы схем «И, причем первый вход регистра промежуточных результатов соединен с

выходом арифметико-логического блока, второй вход - с первым выходом блока управления, а выход - входной магистралью блока регистров с первым входом блока регистров и с пятым входом блока контроля, выход

которого соединен с первыми входами первой группы схем «И, вторые входы которых соединены с нулевым выходом старшего разряда счетчика сбоев, третьи входы соединены с выходом регистра адреса повтора, а выходы соединены с третьим входом регистра адреса микрокоманд, второй выход блока контроля соедине с первыми входами второй группы схем «И, вторые входы которых соединены с выходом регистра микрокоманд, а выходы - с четвертым входом регистра адреса микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1972 |

|

SU474008A1 |

| Микропрограммный процессор | 1973 |

|

SU490122A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммный процессор | 1974 |

|

SU512471A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Процессор | 1974 |

|

SU526902A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

Авторы

Даты

1975-05-15—Публикация

1973-02-21—Подача