1

Изобретение .относится к вычислительной технике и может быть использовано при построении систем обработки информации .

Целью изобретения является упрощение микропроцессора.

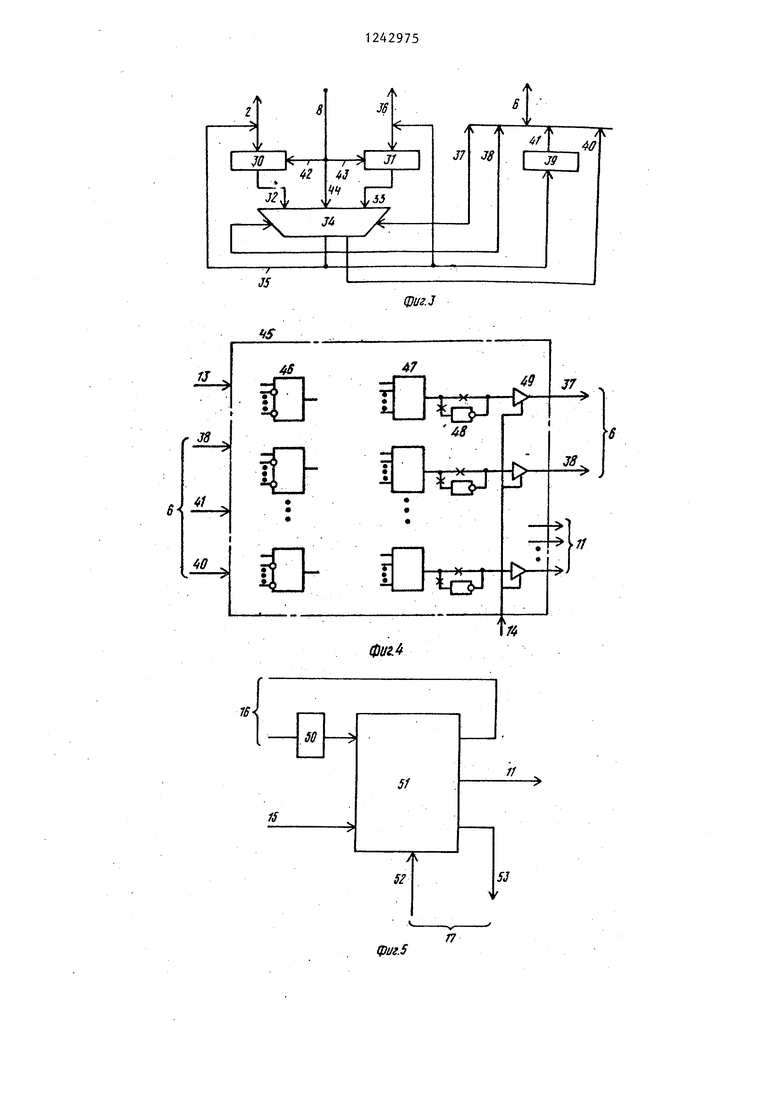

На фиг. 1 представлена функционал ная схема микропроцессора; на фиг, 2 функциональная схема блока многоканальной памяти; на фиг. 3 - функциональная схема арифметико-логического блока; на фиг. 4 - блок-схема блока памяти признаков результата; на фиг. 5 - функциональная схема блока приоритетного прерывания; на фиг. 6 функциональная схема блока микропрограммного управления; на фиг. 7 - ап горитм -выполнения типовой команды микропроцессора-.

Микропроцессор содержит арифметико-логический блок 1, первую внутреннюю магистраль 2, блок 3 двух- канальной сверхоперативной памяти, адресный выход 4 устройства, вторую внутреннюю магистраль 5,, вход-выход признаков состояния арифметико-логического блока, блок 7 памяти признаков операций, выход 8 кода микрооперации, блок 9 микропрограммного управления, блок 10 приоритетного прерывания, выход 11 вектора прерывания, блок 12 многоканальной памяти, входы, выходы и связи между злемен- (тами схемы микропроцессора 13 - 20. Блок многоканальной памяти содержит группу блоков 21-24 четырехка- нальной памяти, где 21 - секция хранения младших разрядов памяти, 22- 23 - секции хранения промежуточных разрядов памяти, .а 24 - секция хранния старших разрядо-в памяти, управляющие входы 25 - 29 блока. Арифметико-логический блок содержит регистр 30 первого операнда, регистр 3 второго операнда, выходы 32 и 33 регистров первого и второго операндов, комбинационное арифметико-логическое устройство 34, СВЯЗИ 35 - 38 между элементами блока; блок 39 формирования признака нулевого результ

та, входы и выходы 40 - 44 блока . Блок памяти признаков результата реализован на программируемой логической матрице 45, в состав которой входят элементы И 46j элементы ИЛИ 47, зле- менты НЕ 48 и трехстабильные элементы 49. Блок приоритетного прерывания содержит регистр 50 запросов прерывания, схему 51 приоритета.

975

2

вход 52 и выход 53 блока. Блок микропрограммного управления содержит генератор 54 тактовых импульсов, блок 55 памяти микрокоманд, регистр 56, микрокоманд, программируемую логическую матрицу 57, связи 58 и 59 между элементами блока. Арифме- тико-логический блок может быть реализован на микросхеме К1802ВС1, блок 7 - на К556РТ1, секции 21 - 24 .на базе КР1802ВВ1.

Каждая секция 12 многоканальной памяти содержит по крайней мере три ячейки для запоминания данных памяти. Кроме того, каждая секция имеет четыре канала ввода/вывода данных. Каждый канал разрядной имеет собственный управляющий вход 25-28, соответ- ственно для первого, второго, третье- 0 го и четвертого каналов. Управляющий вход каждого канала имеет цепи адре- са ячейки и цепь задания операции (чтение, запись) по выбранному каналу. Совокупность управляющих входов 5 для всех секций составляет управляют щий вход памяти. Совокупность входов/ выходов первых разрядных каналов каждой секции составляет вход/выход первого кансша памяти., Входы/выходы вторых разрядных каналов подключены к остальным узлам микропроцессора индивидусШьно как входы/выходы второго канала первой 11, второй 15, третьей и четвертой 19 секций. Совокупность входов/выходов третьих каналов .х с ёк1:1:ий составляет вход/выход третьего канала, а совокупность входов/выходов четвертых каналов всех секций образует вход/выход четвертого канала блока 12 памяти

Микропроцессор работает следующим образом.

Работа входящих в микропроцессор устройств, а также их взаимодействие между собой определяется блоком 9 микропрограммного управления. Задание микропрограмму интерпретации текущей команды осуществляется по выходу 13 четвертого канала блока 12 памяти, по которому в программируемую логическую матрицу 57 ветвления передается код исполняемой команды. Программируемая логическая матрица ветвле- нир 57 по коду текущей команды формирует код адреса первой исполняемой микрокоманды. Из памяти микрокоманд 55 производится выборка кода микрокоманды, которьй по тактовому импульсу от тактового генератора 54

0

5

50

55

Ш

фиксируется в регистре 56 микрокоманд. Выборка последующих микрокоманд осуществляется по коду адреса следующей микрокоманды, задаваемому на выходе 59. В случае необходимости разветвления микрокоманды по выходу 58 регис тра микрокоманд вьщается код номера проверяемого условия ветвления, который настраивает программируемую логическую матрицу 57 ветвления на формирование кода наложения на код адреса следующей микрокоманды по состоянию выхода 13 четвертого канала блока 12 памяти. Код наложения, вырабатываемый программируемой логичес- кой матрицей 57 ветвления, объединяется по функции ИЛИ с выходом 59 адреса следующей микрокоманды и поступает на адресный вход памяти микрокоманд 55.20

Арифметико-логический блок 1 работает следующим образом.

Входная информация (данные) поступает по первому выходу арифметико- логического блока с информационной 25 магистрали 2 и-по второму входу/выходу из блока 3 оперативных регистров соответственно на первый 30 и второй 31 регистры входных данных арифметико-логического блока 1. Управление загрузкой регистров 30 и 31 осуществляется по сигналам управления в цепях 41 и 42 от блока 9 микропрограммного управления по выходу 8. С выходов этих регистров данные поступают соответственно на первый 32 второй 33 входы комбинационной арифметико-логической схемы 34. Дополнительное состояние -арифметико-логической схемы 34 задается по цепям входного 37 и выходного переноса 38 от входа/выхода 6 блока 7 формирования признаков. Настройка комбинационной арифметико-логической схемы 34 на реализацию конкретной функции осу- б1ествляется по входу 43 арифметико- логического блока от входа 8 блока 9 микропрограммного управления. С выхо да 35 арифметико-логической схемы 9 результат операции поступает на первый и второй вход/выход арифметико- логического блока 1 для передачи в другие узлы микропроцессора. Кроме ТОГ0, этот же результат поступает на схему 39 формирования признака

30

40

45

50

по цепи 38, признака нуля результата по выходу 41 и признака переполнения .результата по выходу 40 передаются по обобщенной цепи 6 в блок 7 вания признаков.

Блок 7 работает следующим образом На вход программируемой логической матрицы 45 поступает с выхода 13 чет вертого канала блока 12 памяти код исполняемой инструкции и код признаков состояния микропроцессора. Логическая матрица 45 вьфабатывает на выходах код начального состояния ариф метикоглогического блока 1 и устанав ливает таким образом зависимость меж ду прежним состоянием микропроцессора и последующим результатом испол- няемой инструкции. В тоже время приз наки результата исполняемой инструкции такие как выходной перенос по це пи 38, признак нуля результата по це пи 41 или признак переполнения по цепи 40 также поступают с выхода арифметико-логического блока 1 на вход программируемой логической матрицы 45 и, образуя произведения на схемах 46 И с кодом исполняемой инструкции по выходу 13, формируют по второму выходу блока 7 формирования признаков новый код состояния микропроцессора j который поступает на вход 11 первой секции второго канала блока 12 памяти. Включение и работа блока 7-осуществляется по сигналу от блока 9 микропрограммного управления по его выходу 14. Включение и работа блока 7 производится на этапе вычисления результата и форьп ро- вания нового состояния исполняемой инструкции,.т.е. однократно за всю микропрограмму исполне1шя конкретной инструкции.

Работа блока приоритетного прерывания происходит следующим образом.

По входу-выходу 16 запроса ка пре- рыва ния на входной регистр 50. блока 10 приоритетного прерывания поступают сигналы запросов на прерывания и фиксируются в этом регистре. Приоритетная схема 51 блока приоритетного прерывания производит комбинационньй анализ поступивших запросов и текущего состояния приоритета процесссора по выходу 15 второй секции второго канала блока 12 памяти и производит

нуля результата. Второй выход 40 ариф- вьщачу сигналов разрешения прерываметико-логического блока содержитния по входу-выходу 16, а также

код признака переполнения результата.формирование кода разрешенного прерыЗначения сигналов выходного переносавания и кода по входу-выходу 17 для

Ш

нд , 20

25

30

40

45

50

по цепи 38, признака нуля результата по выходу 41 и признака переполнения .результата по выходу 40 передаются по обобщенной цепи 6 в блок 7 вания признаков.

Блок 7 работает следующим образом. На вход программируемой логической матрицы 45 поступает с выхода 13 четвертого канала блока 12 памяти код исполняемой инструкции и код признаков состояния микропроцессора. Логическая матрица 45 вьфабатывает на выходах код начального состояния ариф метикоглогического блока 1 и устанавливает таким образом зависимость между прежним состоянием микропроцессора и последующим результатом испол- , няемой инструкции. В тоже время признаки результата исполняемой инструкции такие как выходной перенос по цепи 38, признак нуля результата по цепи 41 или признак переполнения по цепи 40 также поступают с выхода арифметико-логического блока 1 на вход программируемой логической матрицы 45 и, образуя произведения на схемах 46 И с кодом исполняемой инструкции по выходу 13, формируют по второму выходу блока 7 формирования признаков новый код состояния микропроцессора j который поступает на вход 11 первой секции второго канала блока 12 памяти. Включение и работа блока 7-осуществляется по сигналу от блока 9 микропрограммного управления по его выходу 14. Включение и работа блока 7 производится на этапе вычисления результата и форьп ро- вания нового состояния исполняемой инструкции,.т.е. однократно за всю микропрограмму исполне1шя конкретной инструкции.

Работа блока приоритетного прерывания происходит следующим образом.

По входу-выходу 16 запроса ка пре- рыва ния на входной регистр 50. блока 10 приоритетного прерывания поступают сигналы запросов на прерывания и фиксируются в этом регистре. Приоритетная схема 51 блока приоритетного прерывания производит комбинационньй анализ поступивших запросов и текущего состояния приоритета процесссора по выходу 15 второй секции второго канала блока 12 памяти и производит

- вьщачу сигналов разрешения прерываодификации адреса следутощей микрооманды. Указанная связь. 17 блока икропрограммного управления присое- иняется к выходу программируемой огической матрицы 57 ветвления и участвует по функции проводного ИЛИ. в формировании адреса микропрограммь) обработки прерывания. Включение блока 10 приоритетного прерывания производится по его входу 52. от блока микропрограммного управления по входу-выходу 17 после каждого исполнения очередной инструкции.

ассмотрим далее работу блока 12 памяти. Перед микропрограммированием процессора ячейки блока 12 памяти специфицируются однозначным образом. Например, первая ячейка назначается для хранения кода команды, вторая - ,пля хранения кода состояния микропроцессора, третья - для хранения промежуточных данных.

Блок 9 микропрограммного управления по выходу 20 в каждой микрокоманде настраивает кажр,ую разрядную сек- . цию каждого из каналов блока 12 памяти. Для строгого изложения описания - запишем в общем виде функцию управления любого из каналов блока 12 памяти в виде

Yij A)j ,Rij ,W.j ,

где Yfj - функ1.щя управления, подаваемая на входы 25-28 соответственно для каналов 1 - 4 (1.б1ё4) и для каждой секции 21-24 () блока 12 памяти, причем

J

W

J

-адрес ячейки памяти для 1-го канала, j-й секции;

-функция чтения по i-му каналу и j-й секции;

-функция записи по i-му каналу и j-й секции.

Таким образом, информация на вхо- де/выходе каждого канала может быть выбрана NMKponporpaMMHbiM способом из отдельных разрядных частей любых яче- ек блока 12 па1Мяти, образуя на выходе канала составное данное. Так, например, на выходе 13 блока 12 памяти может быть образована для одновременного использования информации о значении старших разрядов кода исполняемой микропроцессором команды и младших разрядов ячейки блока 12 памяти, хранящей текущее состояние микропроцессора. Такое составное данное используется блоком микропрограммного управления для принятия решения о на0

5

0

5

0

5

0

5

0

5

правлении ветвления, микропрограммы в зависимости от типа команды условного перехода и значения текущих признаков в текущем состоянии микропро- цессора. Аналогичное составное данное используется блоком 7 формирования признаков для задания на третьем входе/выходе арифметико-логического блока входного состояния, которое зависит от кода команды и текущих признаков состояния микропроцессора.

Для обеспечения работы блока 10 приоритетного прерывания блок 9 микропрограммного управления выводит из блока 12 памяти код приоритета микропроцессора в текущей инструкции исполняемой программы. При этом блоком 9 генерируется следующая функция управления вторым каналом второй секции блока 12 памяти

Yz2 Арс -R W

что обеспечивает чтение кода приоритета микропроцессора из ячейки Ар хранения текущего состояния микропроцессора. Эта информация считывается с выхода 15 блока 12 памяти и посту- пает на первый вход блока 10 приоритетного- прерывания, а на второй вход этого блока поступают сигналы с входов-выходов 16 запроса и разрешения прерывания. Приоритетная схема блока 51 приоритетного прерывания производит приоритетное сравнение сигналов запроса на прерывание с текущим приоритетом микропроцессора. С этой целью каждой линии входа-выхода 16 присвоен жестко конкретньш уровень приоритета. Это сравнение обычно осу- йтествляется в определенной точке мик- ponporpaiNiMbi, которая вьщеляется выдачей блоком 9 микропрограммного управления управляющего сигнала по цепи 1 7. По выходу 20 блок 9 микропрограммного управления для обеспечения занесения в блок 12 памяти адреса вектора прерывания из блока приоритетного прерывания 10 по цепи 11 вьщает следующую функцию управления

Y, Ap3,R,W,

которая обеспечивает запись информации по входу 11 блока 12 памяти в ячейку промежуточных данных Ар.р.

Данная функция управления также как и сигнал разрешения прерывания на выходе 17 блока 9 микропрограммного управления генерируются этим блоком в конечной микрокоманде микропрограммы интерпретации инструкции.

Блок 12 памяти по данному изобретению с целью обеспечения обработки данных различной длины выполняет также операцию переноса старших полуслов (байтов) данных в младший байт внутренней информационной магистрали и наоборот. Так старший байт ячейки промежуточных данных блока 12 памяти согласно функции управления по второму и третьему каналу может быть перенесен на младший байт внутренней информационной магистрали 2 через объединение второго канала третьей и четвертой секции с третьим каналом для первой и второй секции. 19. Аналогичный перенос без применения дополнительных схем может быть осуществлен и в обратном направлении. Функции управления на выходе 20 блока 9 микропрограммного управления будут иметь следующий вид

Y Y Y Y А R W 31 3 З

V . у Д D -J

29 24

Операция переноса необходима в микропроцессоре для приведения данных различней длины к единому формату для правильной обработки арифметико- логическим блоком.

На фиг. 7 представлен пример работы микропроцессора при выполнении им типовой одноадресной команды. В микрокоманде 60 блок микропрограммного управления формирует на выходе 8 адрес оперативного регистра блока 3 оперативных регистров, содержащего адрес команды. Из блока 3 оперативных регистров по первому его входу/выходу производится чтение адреса команды на внутреннюю информационную магистраль 2 и линии 4 адреса интерфейсной шины 5. Одновременно этот адрес записывается в арифметико-логический блок 1, по второму входу которого записывается константа 1, поступающая из блока 3 оперативных регистров. На управляющий вход арифметико-логического блока 1 с выхода 8 блока 9 микропрограммного управления поступает управляющий код операции сложения в арифметико-логическом блоке 1.

Данные с входа-выхода 18 поступают на вход первого канала блока 12 памяти. Эти данные вводятся в блок 12 памяти в микрокоманде 35 и размещаются в ячейке хранения кода команды. Для обеспечения загрузки в блок 12 памяти считываемых по входу-выходу 18

15

данных блок 9 микропрограммного управления вьщает в микрокома1оде 60 на выход 20 следующую функцию управления

YH Y,2 :Y, )4 рк . где Ар - адрес ячейки регистровой памяти, предназначенный для хранения кода команды.

После загрузки кода команды по за- JQ дающему генерат-ору 54 в блоке 9 микропрограммного управления производится выборка следующей микрокоманды 61.

В микрокоманде 61 по состоянию выхода 8 блока 9 микропрограммного управления арифметико-логический блок 1 передает результат операции, заданной в предьщущей микрокоманде, через внутреннюю магистраль 2 в блок 3 Затем завершается формироваш е адре- 2Q са следующей микрокоманды.

Выход 20 блока 9 микропрограммно- fo управления задает следующую функ- . цию управления блока 12 -памяти

31 П 35 -

У При этом на вькоде 13 третьего канала регистровой памяти 12 будет считываться код, содержащийся в ячейке хранения кода команды блока 12 памяти. Этот код с выхода 13 блока 12 памяти поступает на вход блока 9 мик ропрограммного управления, а точнее на вход программируемой логической матрицы 57 в.етвления. По выходу этой матрицы производится формирование адреса следующей микрокоманды. По за дающему генератору 54 блока 9 микропрограммного управления производится выборка и фиксация следующей микрокоманды 62 в регистре 56 микрокоманд.

В примере на фиг. 7 принято, что адрес операнда в коде инструкции содержит косвенный тип обращения-. При этом адрес опера ща располагается в одном ,из оперативных регистров бло- ка 3. Адрес этого регистра содержится в коде команды, переданной в блок 9 микропрограммного управления по выходу 13 блока 12 памяти.

В микрокоманде 62 по линиям 18 данных по адресу, выставленному по линиям 4 адреса интерфейсной шины 5, производится чтение операнда, который загружается на вход первого канала блока 12 памяти по адресу, ячейки про межуточных данных.

Далее, по задающему генератору 54 блок 9 микропрограммного управления фиксирует в регистре микрокоманд 56

0

0

следующую микрокоманду 63. Б этой микрокоманде под управлением выхода 20 блока 9 микропрограммного.управ ления, блок 12 памяти выдает через магистраль 2 в арифметико-логический блок 1 значения ячейки промежуточных данных. На выходе 8 блока 9 микропрограммного управления выставляется код управления операцией в арифметико-логическом блоке 1. Этот код находится в соответствии с кодом команды на выходе 13 блока 12 памяти. В микрокоманде 63 начальное состояние арифметико-логического блока 1 (например, входной перенос) поступают в этот блок через третий вход/выход состояний арифметико-логического блока 1. Значение входа/выхода 6 состояний арифметико-логического блока 1 определяется блоком 7 формирования признаков по состоя.нию выхода 13 блока 12 памяти. С этой целью блок 9 микропрограммного управления вьщает на выход 20 следующую функцию управления

Уд, Ар ,R; W;

, ,, R; W, где А pj, - адрес ячейки хранения сос

тояния микропроцессора в регистровой

памяти 1.2; Арц- адрес ячейки хранения кода команды в регистровой памяти 12.

В следующей микрокоманде 64 блок 9 микропрограммного управления обеспечивает по выходу 8 считывание результата операции из арифметико-логичес- кого блока 1 через внутреннюю информационную магистраль 2 в блок 12 памяти. В этой микрокоманде арифметико-логический блок 1 выдает на свой третий вход/вьгход 6 выходное состояние результата (например, состояние нулевого результата, переполнение разрядной сетки, наличие выходного переноса). Состояние результата арифметико-логического блока поступает в блок 7 формирования признаков На выходе 11 этого,блока в зависимости от кода команды с выхода 13 блока 12 памяти выделяется окончательный код установки признаков в ячейку состояния микропроцессора.

Результат, занесенный в блок 12 памяти, передается в микрокоманде 65 в:а вход-выход микропроцессора по адресу, формируемому на адресном выхо- да 4 с выхода регистров 3.

В микрокоманде 66 по разрешающему сигналу по входу-выходу 17 от бло

0

5

0

5

0

0

0

ка 9 микропрограммного управления блок 10 приоритетного прерывания принимает запрось на прерывания с входа-выхода 16 микропроцессора и сравнивает их на приоритетной основе с кодом текущего приоритета микропроцессора на выходе 15 регистровой памяти 1. Для обеспечения чтения кода приоритета на выходе 20 блока 9 микропрограммного управления поддерживается функция управления

Y2,,Apo, R, W.

По результату сравнения приоритета микропроцессора и приоритета принятого запроса блок 10 приоритетного прерывания выдает на выход 11 первой секции второго канала регистровой памяти 12 адрес вектора прерывания. При этом второй канал получает с выхода 20 блока 9 микропрограммного управления функцию управления

Y, Apj,, R, W.

Блок приоритетного прерывания передает на выход 17 блока микропрограммного управления сигнал наличия прерывания, которьш поступает на вход программируемой логической матрицы 57 ветвления. Этот сигнал определит выборку первой микрокоманды 67 процедуры, прерывания..

Если в результате сравнения приоритетов запросов с линий 16 запроса и разрешения прерывания и кода приоритета микропроцессора с выхода 15 регистровой 12 приоритет процессора оказыва€ тся выше или равен приоритет / пришедшего запроса с входа-выхода 16 запроса и разрешения прерываний,- то прерывания не произойдет и сигнал нал:ичия прерывания будет отсутствовать. Блок микропрограммного управления при этом выберет следу ощую микрокоманду 60, с которой начнет выборку и исполнение следующей команды.

Приведенный на фиг. 7 алгоритм выполнения типовой команды показывает процесс преобразования данных одного формата. Микропроцессор имеет также возможность перестраиваться на обработку данных половинного, формата (например, байтов 16-разрядного слова. При этом следует различать мла дшую и старшую половину слова. Приведенный на фиг. 7 алгоритм в целом сохраняется за исключен ием микрокоманд 63 и 64, в которых меняются функции управления, задаваемый блоком 9 микропрограммного управления по его выходам 20 и 8, В микрокоманде 63 в случае обработки старшей половины слова, операнд считывается по второму каналу 19 третьей и чет- вертой секции блока 12 памяти, которые соедин.е ны с младшими разрядами внутренней информационной магистрали 2 . В микрокомандре 64 при считывании результата операции информация из арифметико-логического блока 1 через внутреннюю информационную маги страль 1 поступает на вход/выход 19 второго канала третьей и четвертой .секции блока 12 памяти и размещается, таким образом, в старших разрядах ячейки промежуточных данных блока 12 памяти.

Формула изобретения

1. Микропроцессор, содержащий арифметико-логический блок, блок двухка- нальной сверхоперативной памяти, бло приоритетного прерывания, блок памят признаков операций и блок микропрограммного управления, причем первый информационный вход-выход арифме тико логического блока через первую внут- реннюю шину соединен с первым информационным входом-выходом блока двух- канальной сверхоперативной памяти, отличающийся тем, что, с целью упрощения его конструкции, он содержит блок многоканальной памяти, причем инфopмaц ioнньш вход- выход первого канала блока многоканальной памяти подключен к информационному входу-выходу микропроцессора, информационный вход-выход старши разрядов второго канала блока многоканальной памяти, информационный вход-выход третьего канала блока многоканальной памяти соединены через первую внутреннюю шину с первым информационным входом-выходом арифметико-логического блока, второй ин- формац11онный вход-выход которого через вторую внутреннюю шину соединен с адресным выходом микропроцессора и вторым информационным кодом-выхо- дом блока двухканальной сверхопера- тивной памяти, информационный выход четвертого канала блока многоканальной памяти подключен к входу кода команды блока микропрограммного управления и к адресному входу старших разрядов блока памяти признаков

10

15

20

35

25п

40

5

5

результата, информационный вход-выход мпадцих разрядов второго канала блока многоканальной памяти соединеь с входом текущего приоритета блока приоритетного прерывания и с выходом кода вектора прерывания блока приори тетного прерывания, первьй и второй выходы блока микропрограммного управления подключены соответственно к адресному входу и входу записи-считывания блока многоканальной памяти, третий выход блока MiiKponporpaMMHoro управления подключен к входу выборки блока памяти признаков операций, четвертый выход блока микропрограммного управления подключен к входу кода микрооперации арифметико-логического блока, к адресному входу и к входу записи-считывания блока двухканальной сверхоперативной памяти, выход признака наличия прерывания- блока приоритетного прерывания подключен к входу признака модификации адреса блока микропрограмм 1ого управления, пятый выход блока микропрограммного управления -подключен к входу запуска блока приоритетного прерывания, вход запроса прерывания которого подключен к входу запросов на прерывание микропроцессора, выход признаков результата выполнения операции блока памяти признаков операций подключен к входу, признаков операндов арифметико-логического блока, выход признаков режима микропроцессора блока памяти признаков операций подключен . к входу-выходу младших разрядов второго канала блока многоканальной памяти, выход признаков результата арифметико-логичесхсого блока подключен к адресному дходу младших разрядов блока памяти признаков операций.

2. Микропроцессор по п. 1, отличающийся тем, что блок многоканальной памяти содержит группу блоков четырехканальной памяти, причем первые информационные входы- выходы блоков четырехканальной памяти группы подключены к информационному вход-выходу первого канала блока, информацион1-1ый вход-выход старших разрядов второго канала блока подключен к вторым информационным выходам первого и второго блоков четырехканальной памяти группы, вторые информационные выходы третьего и четвертого блоков четырехканальной памяти группы подключены к инфор -выходы блоков четырехканааьной памямационному входу-выходу младших .раз-ти группы подключены соответственно

рядов второго канала блока,третийк информационным входам-выходам

и четвертьй информационные входы- третьего и четвертого каналов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ И ЧЕРЕДУЮЩИМСЯ ОБСЛУЖИВАНИЕМ НЕСКОЛЬКИХ КОМАНДНЫХ ПОТОКОВ | 1995 |

|

RU2099780C1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

Изобретейие относится к вычислительной технике и может быть использовано при построении систем обработки информации. Цель изобретения - упрощение микропроцессора. Он содержит арифметико-логический блок, блок двухканальной сверхоперативной памяти, блок формирования признаков операций, блок микропрограммного управления, блок многоканальной памяти и блок приоритетного прерьгеания. Цель изобретения достигается за счет повьшения регулярности связей между элементами и однородности структуры. 1 з.п. ф-лы, 7 ил. G ю J 1чЭ Г) СП

(.z

rj

4S

О

37

5f

11

5Z

S3

фиг.5

17

Редактор В.Иванова

фиг. 7

Составитель М.Силин ; Техред М.Ходанич Корректор Т.Колб

Заказ .3707/49 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

фиг. 6

| Двторское свидетельство СССР № 747327, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-07-07—Публикация

1984-07-25—Подача