1

Изобретйше относится к области запоминающих устройств.

Известны ЗУ с автономным контролем П, 2.

Ощю из известных ЗУ coflq)KHT накопитель, подключеш1ый через блок воспроизведения к регистру числа, выполнещюму на триггерах со счетным входом, блок контроля достоверности информации, соедине шый с блоком управления и с регистром числа 1.

Это устройство позволяет исправить одиночные ошибки, однако такие ошибки в нем не фиксируются.

Из известных устройств наиболее близким техтиеским решением к изобретению является ЗУ с автономным контролем, содержащее , счетчик, выход которого подключен к первому входу блока индикации и входу блока памяти, соединешюго с блоком декодирования, блок контроля, блок останова, выход которого соединен со входом счетчика, и блок управления 2J,

В этом ЗУ в режиме работы с ЦВМ осуществляется исправление одиночщ,1Х и обнаружеяие двойных оишбок, а в режиме Проверка осуществляется обнаружение и устранение неисправимых элементов блока памяти.

Недостатком этого устройства является то, что оно не обеспечивает контроль блока памяти во время работы, кошролируя его только в режиме Проверка и не обеспечивает статической обработки информации об ощибках, что приводит к низкой надежности устройства.

Целью изобретения является повышение надежности ЗУ за счет обеспечения анализа ошибок и сбоев в работе блока памяти.

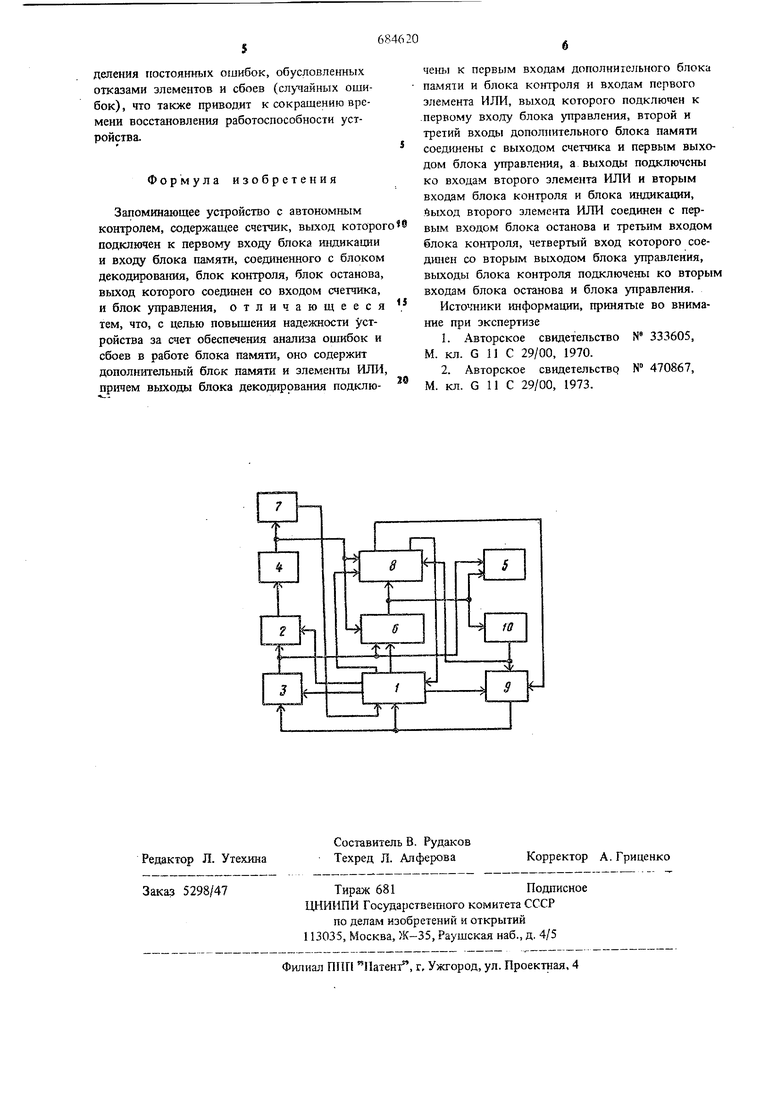

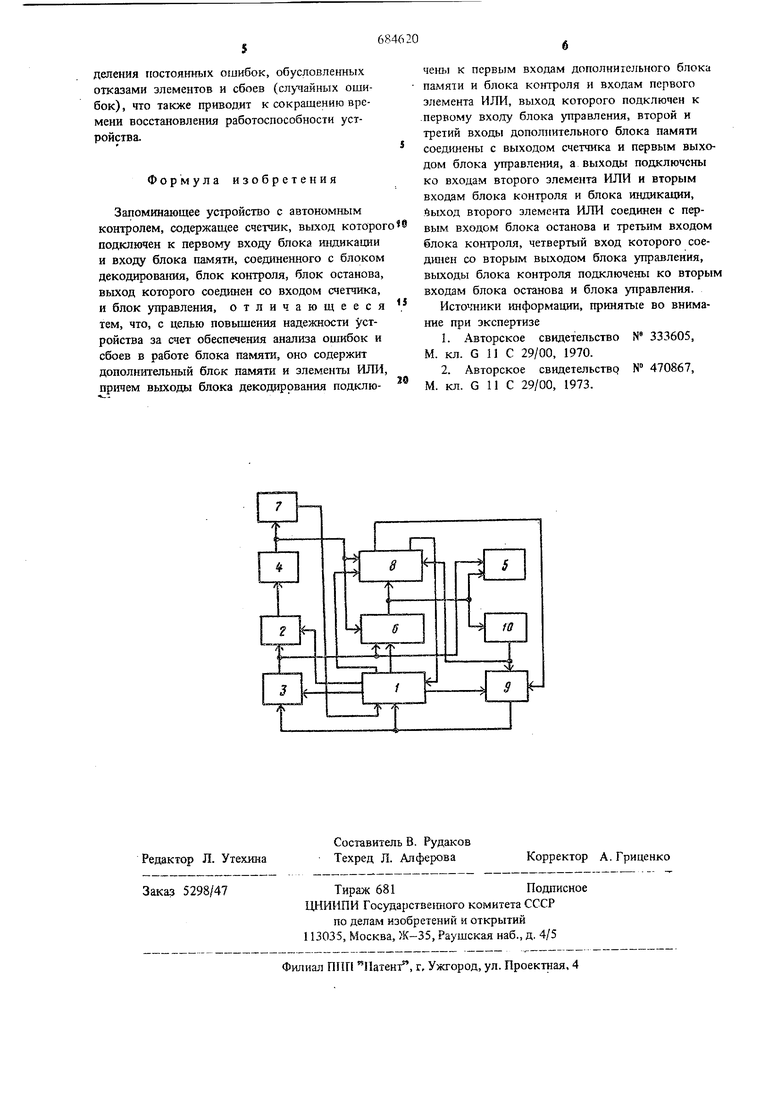

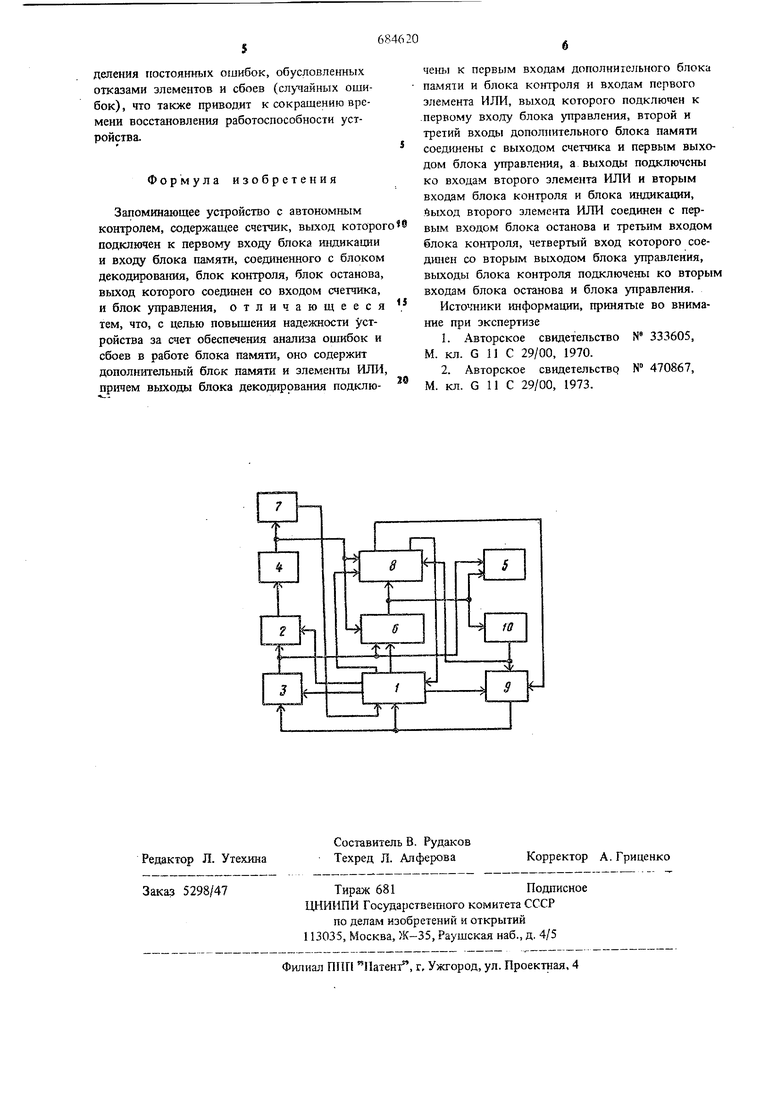

Поставленная цель достигается тем, что предложеьшое ЗУ содержит дополнительный блок памяти и злеметы RTIIi. Выходы блока де сорлровання подключены к первым входам дополнительного блока памяти и блока контроля и входам первого элемента ИЛИ, выход которого подключен к первому входу блока управления. Второй и третий входы дополнительного блока памяти соед}шеШ)1 с выходом счетчика и первым выходом блока управления, а выходы подключены ко входам второго элемента ИЛИ и вторым входам блока контроля и блока индика1ши. Выход второго элемента ИЛИ соедлнен с первым входом блока останова и третьим входом блока контроля, четвертый вход которого соедШ1ен со вторым выходом блока управления. Выходы блока контроля подключены ко вторым входам блока останова и блока управления. Па чертеже представлена структурная схема ЗУ с автономным контролем. ЗУ содержит блок управления 1, блок памя ти 2, счетч}1к 3, блок декодирования 4, блок индикации 5, дополнительный блок памяти 6, IIqpвый элемент ИЛИ 7, блок контроля 8, бло останова 9 и второй элемент ИЛИ 10. Выходы блока 4 подключены к первым вхо дам блоков 6 и 8 и входам элемента ИЛИ 7, выход которого подключен к первому входу блока 1. Второй и третий входы блока 6 соединены с выходом счетчика 3 и первым выходом блока 1, а выходы подключены ко входам элемента ИЛИ 10 и вторым входам блоков 8 и 5. Выход элемента ИЛИ 10 соединен с первым входом блока останова 9 и третьим входом блока 8, четвертый вход которого сое динен со вторым выходом блока 1. Выходы блока 8 подключены ко вторым входам блоков 1 и 9. В устройстве предусмотрено 3 режима работы. В первом (рабочем) режиме осуществляется исправление одиночной, обнаружение даойной ошибки и запись кода одиночной ошибки в блок 6. При этом блок управления 1 формирует сигналы запрета по заправляющему входу блока 9 и по четвертому входу блока 8, управляющие сигналы считывания, поступающие в блок 2, и управляющие сигналы приема адреса из ЦВМ в счетчик ащзеса 3 (цепи адреса из ЦВМ на чертеже не показаны). Считанны из блока 2 информационный код по соответствующему адресу поступает в блок 4, где осу ществляется исправление одиночной и обнаруж ние двойной ощибок. Код одиночной ощибки с выхода блока 4 подается на первый вход блока 6 и на входы элемента ИЛИ 7. При ненулевом коде ощибки элемент ИЛИ 7 разрещает блоку управления I формирование управ ляющего сигнала записи кода ощибки в блок по соответствующему адресу. Во втором режиме (режиме контроля блока памяти 3) осзтцествляется фиксащш адресов сбоев и ощибок, обнаруженных в рабочем режиме. При этом блок управления 1 формируе сигнал запрета по четвертому входу блока 8, сигнал разрещения по управляющему входу блока 9, осуществляет пуск счетчика 3 и форм рование управляющего сигнала считывания, поступающего в блок 6. При пуске счетчика 3 обеспечивается перебор всех адресов блока 6. При этом считанный по соответствующему адресу код ощибки поступает на входы блока индикации 5 и элемента ИЛИ 10. При ненулевом коде ощибки элемент ИЛИ 10 вырабатывает разрешение по первому входу блока 9, с выхода которого вырабатывается сигнал останова на управляющие входы счетчика 3 и блока управления 1 и осуществляется индикация кода и адреса одиночной ошибки. В третьем режиме (режиме статического контроля) осуществляется статистический анализ ощибок, записанных в блок 6 в первом режиме, с целью выделения случайных и постоян1Пэ1Х ошибок в блоке 2. При этом блок управления 1 формирует сигнал запрета по управляющему входу блока 9, сигнал разрешения по четвертому входу блока 8, осуществляет пуск счетчика 3 и формирует управляющие сигналы считывания, поступающие в блоки 2 и 6. При пуске счетчика 3 обеспечивается перебор всех адресов блоков 2 и 6. Считанный по каждому адресу из блока 2 информационный код поступает в блок 4, па выходе которого при наличии ощибки получается ненулевой код. Код ошибки с блока 4 и код считанный из блока 6, поступают в блок 8, который осуществляет статистический анализ ошибок с целью выделения постоянных ошибок в блоке 2. Анализ кодов осуществляется по сигналу разрещения, который вырабатывается элементом ИЛИ 10 при ненулевых кодах ошибки, считанных из блока 6. При совпадении кодов блок 8 выдает управляющий сигнал на блок управления 1, который производит повторный опрос блоков 2 и 6 по соответствующему адресу. При повторном совпадении кодов блок 8 вырабатывает управляющий сигнал на блок 9, с выхода которого вырабатывается сигнал останова устройства. При этом блок шодикации 5 фиксирует адрес. и код постоятшой ощибки, возникшей в блоке 2. Анализируя результаты второго и третьего режима, можно получить данные о случайных ощибках блока 2, так как во втором режиме фиксируются все ощибки, а результатом третьего режима является обнаружение только постоянных ощибок. Описанное ЗУ с автономным контролем отличается от прототипа тем, что оно не только исправляет одиночные ощибки, но одновременно фиксирует в рабочем режиме все. неисправные элементы памяти, что приводит к значительному ускорению процесса восстановления работоспособности устройства, повышает точность контроля и в конечном итоге надежность ЗУ в целом. Кроме того, описанное устройство позволяет анализировать ощибки, с целью определения постоянных ошибок, обусловленных отказами элементов и сбоев (случайных ошибок), что также приводлт к сокращению времени восстановления работоспособности устройства. Формула изобретения Запоминающее устройство с автономным контролем, содержащее счетчик, выход которог подключен к первому входу блока индикации и входу блока памяти, соед1шенного с блоком декодирования, блок контроля, блок останова, выход которого соед1шен со входом счетчика, и блок управления, отличающееся тем, что, с целью повышения надежности устройства за счет обеспечения анализа ошибок и сбоев в работе блока памяти, оно содержит дополнительный блок памяти и элементы ИЛИ, протем выходы блока декощфрвания подключены к первым входам дополнигельного блока памяти и блока контроля н входам первого элемента ИЛИ, выход которого подключен к .первому входу блока управления, второй и третий входы дополнительного блока памяти соеди ены с выходом счетчика и первым выходом блока управления, а выходы подключены ко входам второго элемента ИЛИ н вторым входам блока контроля и блока индикации, Аыход второго элемента ИЛИ соединен с первым входом блока останова и третыгм входом блока контроля, четвертый вход которого соедш1ен со вторым выходом блока управления, выходы блока контроля подключены ко вторым входам блока останова и блока управления. Источники информации, принятые во внимаirae при экспертизе 1.Авторское свидетельство N 333605, М. кл. G 11 С 29/00, 1970. 2.Авторское свидетельствр № 470867, М. кл. G 11 С 29/00, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С БЛОКОМ КОНТРОЛЯ | 1966 |

|

SU189621A1 |

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1317484A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Устройство для контроля памяти | 1978 |

|

SU743039A1 |

| Устройство для контроля памяти | 1980 |

|

SU926724A2 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1081669A1 |

| Устройство для контроля блоков постоянной памяти | 1975 |

|

SU668008A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Запоминающее устройство с диагностированием ошибок | 1987 |

|

SU1644231A1 |

Авторы

Даты

1979-09-05—Публикация

1977-05-16—Подача