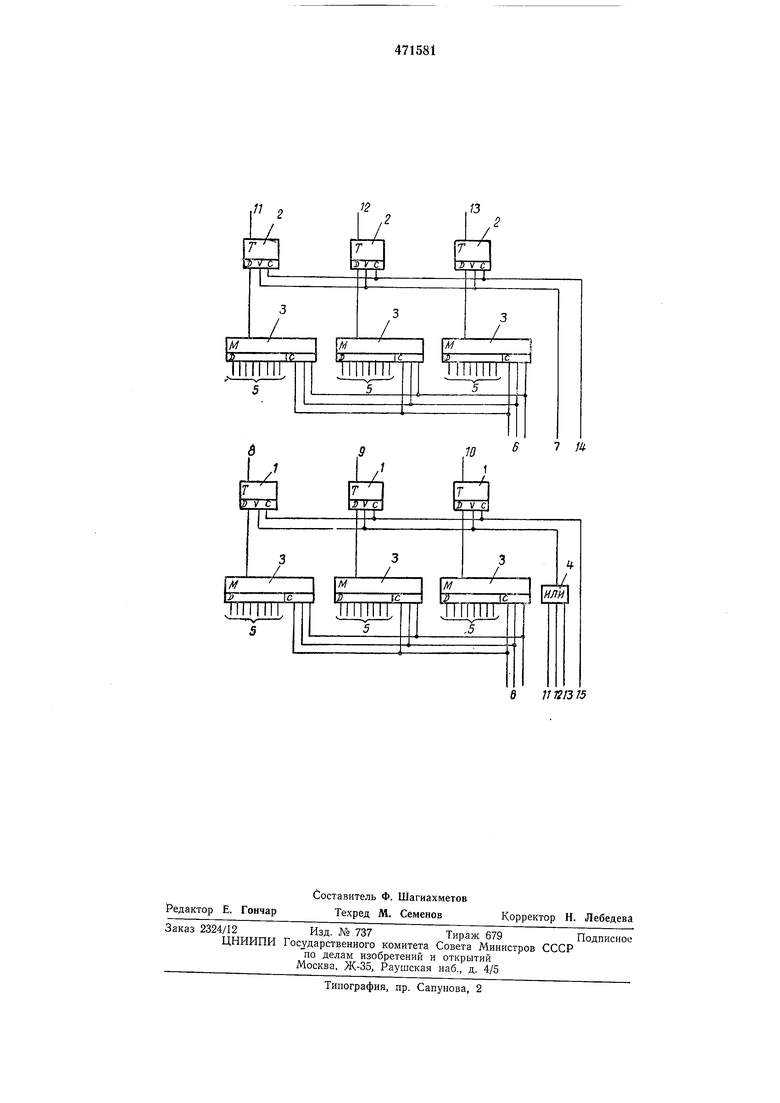

дом регистре. Соответственно с изменением числа триггеров будет меняться и число схем коммутации 3, и число входов в первой и второй группах входов этих схем коммутации.

Число входов во второй группе 6 входов каждой схемы коммутации 3 может быть любым, например п, тогда число входов в первой группе входов 5 у данной схемы коммутации 3 будет 2. Окончательная конфигурация устройства синхронизации определяется при конкретном задании, причем режимы ожидания можно реализовать как на первом, так и на втором регистрах. Если режим ожидания реализуется и на втором регистре, то в устройство нужно ввести вторую схему ИЛИ и выход ее подключить к входной шине 7. Благодаря описанным связям осуществляется такой принцип работы устройства, что код, например, на выходных шинах ll-f-13 триггеров 2 второго регистра, характеризуюш,ий состояние устройства синхронизации в данный момент времени, подается одновременно на вторую группу входов 6 всех схем коммутации 3 первого регистра. При этом, сигналы на входах второй группы входов 6 схем коммутации 3 в зависимости от подаваемого на них кода пропускают на выход каждой схемы код одного из логических условий, подаваемых на первую группу входов 5.

На выходах схем коммутации 3 первого регистра в соответствии с логическими условиями вырабатывается код следующего состояния устройства синхронизации, который, запоминается в первом регистре в момент прихода сигнала синхронизации по шине 15. В свою очередь код с выходных шин триггеров 1 первого регистра одновременпо подается на вторую группу входов 6 всех схем коммутации 3 второго регистра. На выходах этих схем коммутации в соответствии с сигналами на входах первой группы входов 5 вырабатывается код следующего состояния устройства, который запоминается во втором регистре в момент прихода сигнала синхронизации по шине 14. Если же на первую группу входов 5 схем коммутации 3 второго регистра не поступили логические условия, которые определяют следующее состояние устройства синхронизации, то на выходах этих схем коммутации 3 вырабатываются нулевые сигналы, которые в момент поступлепия сигпала по

шине 14 записывают в триггеры 2 второго регистра нули. Полностью нулевой код иа выходах второго регистра является нерабочим для этого регистра и используется для 5 выработки схемой ИЛИ 4 сигнала, запрещающего изменение состояния первого регистра. Таким образом код, установленный в момент поступления сигнала по шине 15 в первом регистре, будет храниться сколько угодно до

0 тех пор, пока не поступят на первую группу 5 входов схем коммутации 3 второго регистра логические условия, необходимые для перевода устройства синхронизации в следующее состояние. Любой ненулевой код на выходах

5 второго регистра, поступая на схему ИЛИ 4, вырабатывает сигнал, разрешающий изменение состояния первого регистра.

Такой способ организации режима ожидания требует всего лишь одного нерабочего состояния устройства синхронизации для реализации любого числа состояний, в которых необходим режим ожиданий.

Описанная структура и принцип действия устройства синхронизации позволяют кодировать состояние устройства любым типом кода: неизбыточным, кодом с постоянными весами, составным кодом и т. д., а также позволяет уменьшить аппаратурные затраты на построение устройства синхронизации.

Предмет изобретения

Устройство синхронизации, содержащее регистры на /ЗУ-триггерах по числу фаз синхронизации и шины фазовой синхронизации, отличающееся тем, что, с целью сокращения оборудования устройства при работе в режиме ожидания, оно содержит схемы коммутации и схему ИЛИ, выход которой соединен с входами 1/-триггеров первого регистра,

0 входы /-триггеров второго регистра соединены с входами устройства, входы схемы ИЛИ соединены с выходами триггеров второго регистра, входы С-триггеров первого и второго регистров соединены с шинами второй и первой фазы синхронизации соответственно, входы D-триггеров соединены с выходами схем коммутации, первые группы входов которых соединены с группами входов устройства, а вторые группы входов схем коммутации одного регистра соединены с выходами триггеров другого регистра.

В7/4

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации | 1981 |

|

SU1015366A1 |

| Устройство для поиска информации на перфокартах | 1974 |

|

SU555398A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для управления энергопитанием микропроцессорной системы | 1983 |

|

SU1201829A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1989 |

|

SU1667090A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Тестер для контроля цифровых блоков | 1986 |

|

SU1555704A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

в 171213 5

Авторы

Даты

1975-05-25—Публикация

1973-02-02—Подача