1

Изобретение относится к вычислительной технике и может быть использовано для синхронизации сигналов одного устройства ЭВМ с тактовыми сигналами (синхросигналами) другого устройства и для синхронизации сигнала запуска от кнопки с синхросигналом устройства.

Известно устройство для синхронизации импульсов, содержащее входной, основной и вспомогательный триггеры, формирователь, инвертор, схемы И, причем шина «СБРОС соединена с первым входом первой схемы И, выход которой соединен с входом «О входного триггера; выход второй схемы И соединен с входом «1 входного триггера, выход «1 которого соединен с первым входом третьей схемы М; выходы третьей и четвертой схем И соединены соответственно с входами «1 и «О основного триггера, выходы «1 и «О которого соединены соответственно с первыми входами нятой и шестой схем И, выходы которых присоединены соответственно к входам «1 и «О вспомогательного триггера; шина «Синхронизация присоединена к первому и второму входам соответственно четвертой и третьей схем И, шина «Блокировка присоединена ко вторым входам пятой и шестой схем И.

Известное устройство для синхронизации позволяет выделить одиночный сигнал синхронно с сигналом тактовой серии, но не позволяет синхронизировать сигналы при иередаче их от одного устройства к другому. Кроме того из-за иснользования двух независимых тактовых серий при частичном совпадеНИИ синхросигналов обеих серий возможно возникновение помех на выходе устройства.

Цель изобретения - упрош,ение известного устройства и повышение надежности работы. Суш,ность изобретения заключается в том,

что шина «вход соединена с входом формирователя, выход которого соединен с первым входом второй схемы И н входом инвертора, выход которого соединен с третьим входом шестой схемы И, «выход «1 вспомогательного триггера соединен со вторыми входами первой и четвертой схем И; выход «О вспомогательного триггера соединен с вторым входом второй схемы И; выход «1 основного триггера соединен с шиной «Сигнал.

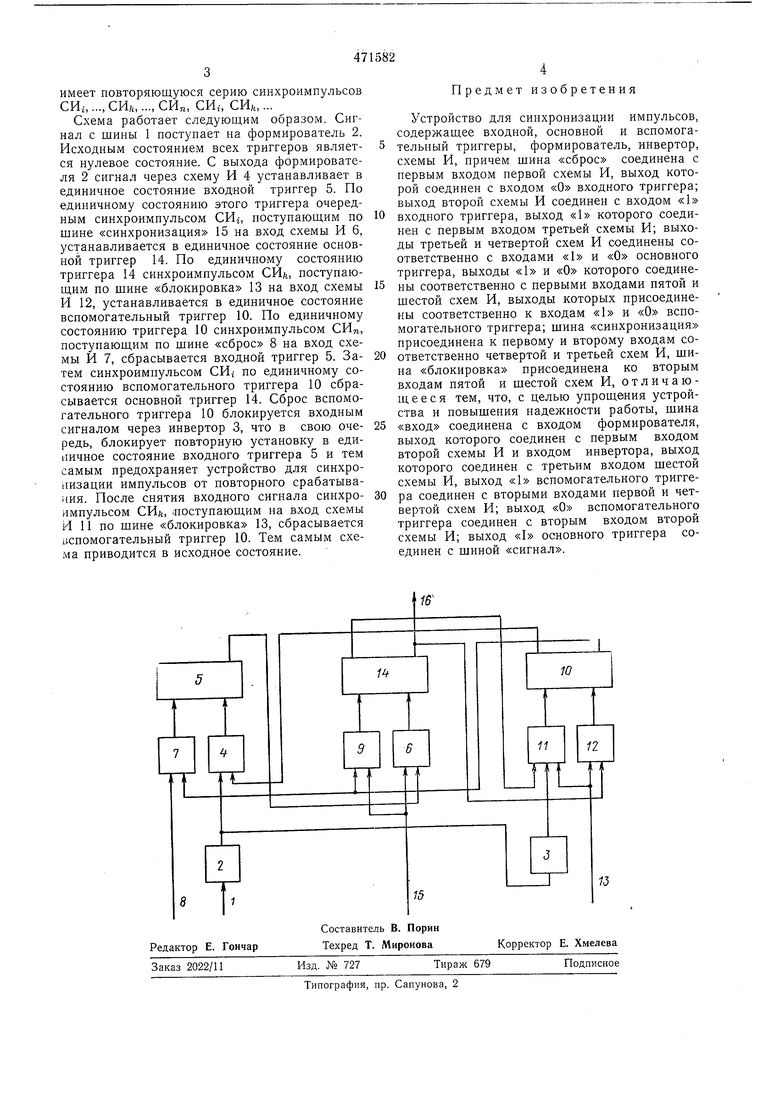

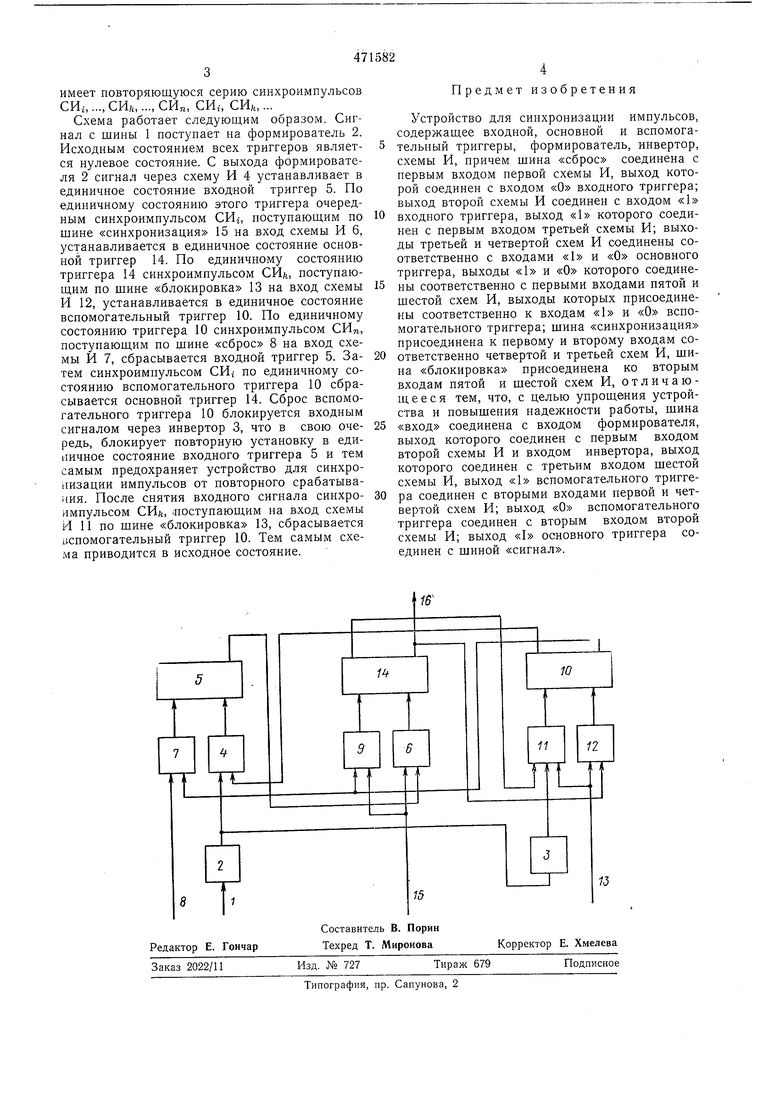

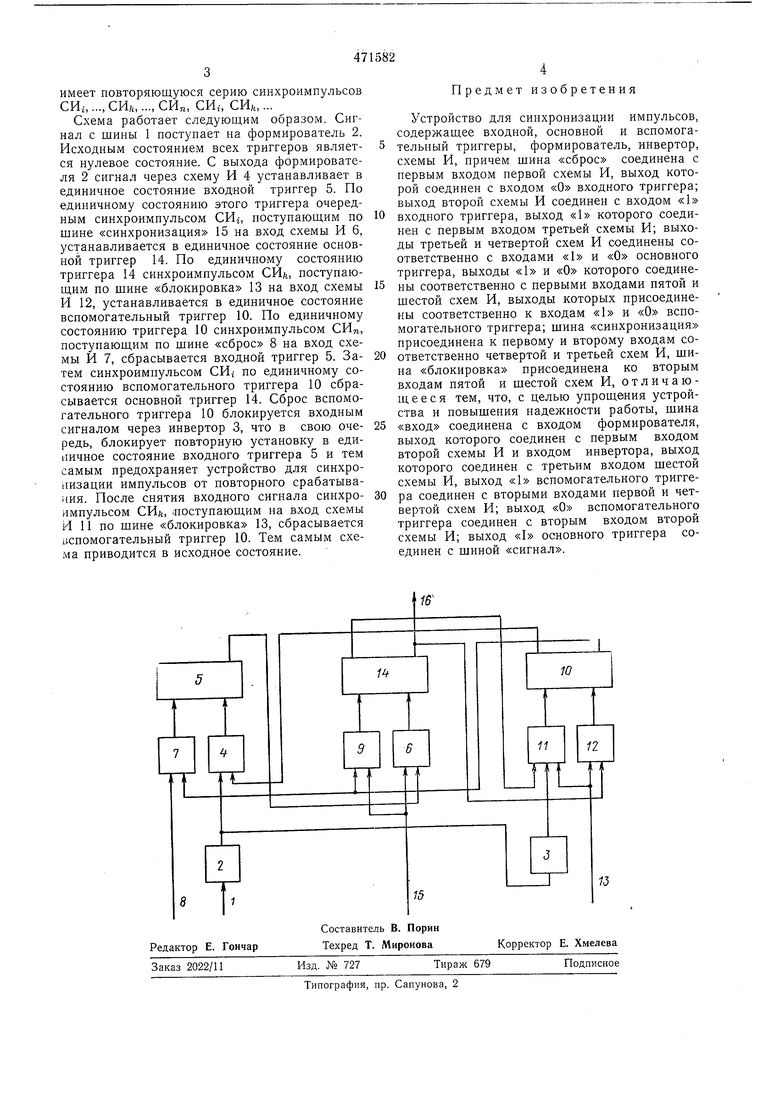

На чертеже приведена схема устройства.

Устройство для синхронизации импульсов содержит шину 1 (вход), формирователь 2, инвертор 3, схему И 4, входной триггер 5, схему И 6 и 7, шину «сброс 8, схему И 9,

вспомогательный триггер 10, схему И 11 и 12, шину «блокировка 13, основной триггер 14, шину «синхронизации 15 и шину «сигнал 16. Рассмотрим один из вариантов использования схемы синхронизации. При этом варианте

любая ЭВМ, содержашая рассматриваемое устройство для синхронизации импульсов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации каналов | 1985 |

|

SU1262471A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1136175A2 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПИТАНИЕМ РАДИОЛОКАЦИОННЫХ СИСТЕМ | 2011 |

|

RU2449343C1 |

| Устройство управления загрузкой микропрограмм | 1982 |

|

SU1042025A1 |

| Устройство для синхронизации с контролем | 1983 |

|

SU1161933A1 |

| Устройство контроля электропитания процессора | 1983 |

|

SU1096649A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

Авторы

Даты

1975-05-25—Публикация

1973-05-29—Подача