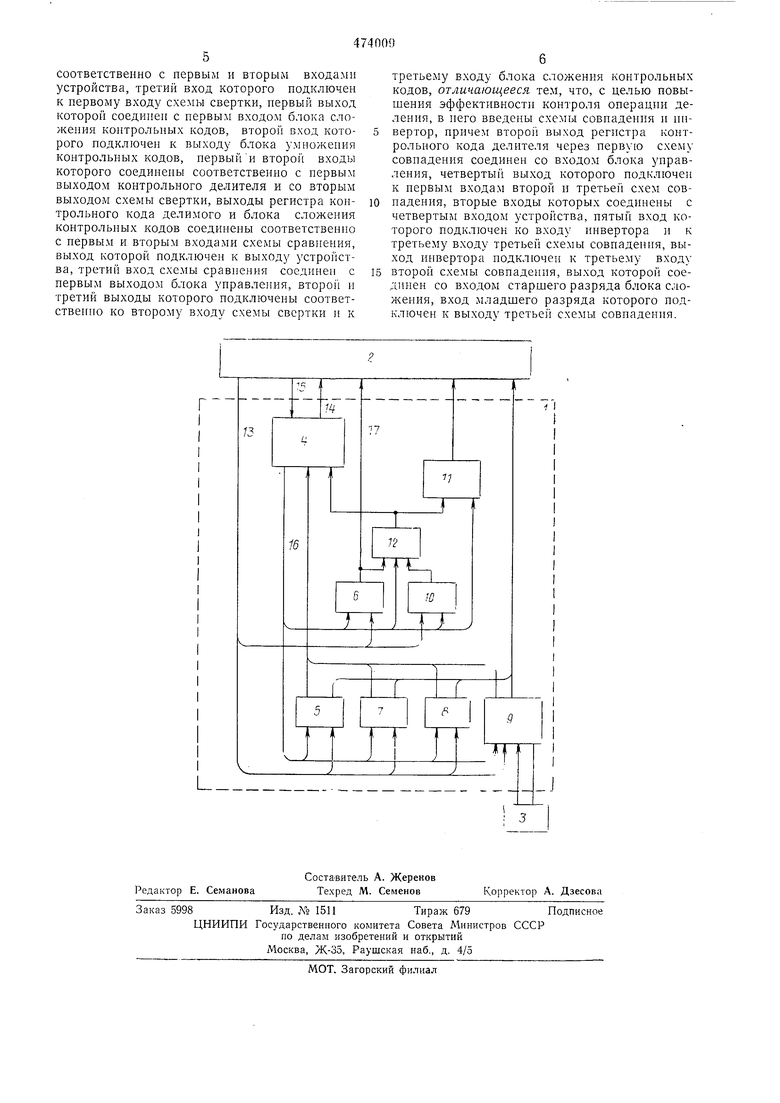

3

рольных кодов 7, схему сравнения 8, вход 9 устройства, блок умножения контрольных кодов 10, выход 11 устройства, схемы 12-14 совпадення, входы 15 н 16 устройства н ннвертор 17.

Контрольные коды онерандов, над ко1орыми производится арифметическая операция, записываются в регистры 1 и 2. При контроле операции деления контрольный код делимого проходит через вход 3 устройства на вход регистра 1, а контрольный код делителя через вход 4 устройства - на вход регистра 2. Если контрольный код делителя не равен модулю три, то блок управления 5 после окончания операции делення выдает ряд сигналов управления на схему свертки 6, блок сложения контрольных кодов 7 и схему сравнения 8. В соответствии с этими сигналами нервоначально схема свертки 6 определяет код остатка от кода частного, ностунающего на ее вход с входа 9 устройства, передает эгог код остатка на вход блока умножения контрольных кодов 10.

Блок умножения контрольных кодов 10 образует код произведения контрольного кода частного и делителя и передает его в предварительно установленный в исходное состояние блок сложения контрольных кодов 7. Затем схема свертки 6 по сигналу из блока управления 5 определяет контрольный код от кода остатка, образующегося в арифметическом устройстве в результате выиолнения операции деления. Этот контрольный код с выхода схемы свертки 6 поступает в блок сложения контрольных кодов 7. Образовавшаяся сумма контрольных кодов сравнивается схемой сравнения 8 с контрольным кодом делнмого, постунающи.м с выхода регистра 1. В случае неравенства схема сравнения выдает на выход 11 сигнал «сбой. Если контрольный код делителя равен .модулю три, то схема совпадения 12 формирует сигнал на входе блока управления 5, который выдает иа первые входы схем 13 и 14 сигнал разрешения переписи в блок сложения р онтрольных кодов 7 сигналов переноса, поступающих па вторые входы схем 13 и 14 со входа 15 устройства в течение всей операцни. Тактовые сигналы сдвигов частного, поступающие на вход 16 устройства, проходит через инвертор 17 на третий вход схемы 13 и непосредственно на третий вход схемы 14. В результате этого при тактовых сигналах, соответствующих формированию в арифметическом устройстве значения нечетного разряда частного, открывается схема 13, а нрп тактовом сигнале, соответствующем формированию четного разряда частного, - схема 14.

Таким образо.м, в ходе выполнения отдельных тактов операции деления поочередно открываются схемы 13 н 14, и сигналы переноса нроходят либо через схему 13 на вход старшего разряда блока сложения контрольных кодов 7, либо через схему 14 на вход .младшего разряда этого блока. После окончания

4

онерации деления блок унравления 5 закрывает схемы 13 и 14 и выдает ряд сигналов управления. По этим сигналам первоначально схема свертки 6 образует контрольный код от

кода частного, поступающего нз арифметического ycTpoiicTBa, и осуществляется передача кода с выхода схемы свертки 6 в блок сложения контрольных кодов 7. Зате.м схема свертки формирует контрольный код от кода

остатка, образовавшегося в результате операции деления. Этот контрольный код также нередается в блок сложения контрольных кодов 7. Образовавшаяся сумма контрольных кодов сравнивается схемой сравнения В с

контрольным кодом делимого, поступающим с выхода регистра 1 контрольного кода.

Пример: X 0.010111 (делнмое), /, Юг (двоичная система); У 0.110011 (делитель). /, 1 Ь;

0.11011 0.0000001011

- 0.011 100 -г

7 654321 - разряды ; J U i .

Z 0.011100 (частное)/, 0,l2

Г 0.0000001011 (остаток) R,, Ю,

При осуществлении ко1ггроля операции делепия приведенных выше чисел возникает ситуация, когда контрольный код делителя Ру равен модулю ко ггроля три.

В ходе вынолнения онерации деления снгнал нереноса из старшего разряда сум.матора арифметического устройства (АУ) в соответствии с известны.ми алгоритмами выполнения данной операцнн должны ноявляться на входе 15 -стройства при определении значений третьего, четвертого и иятого разрядов частного.

В результате этого нри тактовых сигналах, соотвсгствующих формированию в ЛУ значений нечетных разрядов частного (третьего и пятого), открывается схема 13, и на вход блока сложения контрольных кодов 7 дважды

подается код 102, а нри тактово.м сигиале, соотвествующе.м фор.мированию в АУ значения четного разряда частного (второго), открывается схема 14, и на вход блока сложения ко1ггрольных кодов 7 подается код ОЬ.

Таким образом, носле окончания операции деления в блоке сложения контрольных кодов 7 формируется ко.а (10 + + 01 + 10) mod, З Юг, т. е. R, lOj. При правильном выполнении операции делеиия вынолпяется контрольное соотношение

R , (R,+ R,+ R,) mods, так как 10 (0,1 + 10 -f 10) mod3.

Предмет изобретения

Устройство для контроля арифметических операций по модулю три, содержащее регистры контрольного кода делителя и контрольноге кода делимого, входы которых соединены

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления чисел в интервально-модулярном коде | 1984 |

|

SU1241240A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ С АППАРАТНЫМ КОНТРОЛЕМ | 1969 |

|

SU243964A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1971 |

|

SU302002A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления чисел в системе остаточных классов | 1985 |

|

SU1287152A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1973 |

|

SU385273A1 |

Авторы

Даты

1975-06-15—Публикация

1970-03-02—Подача