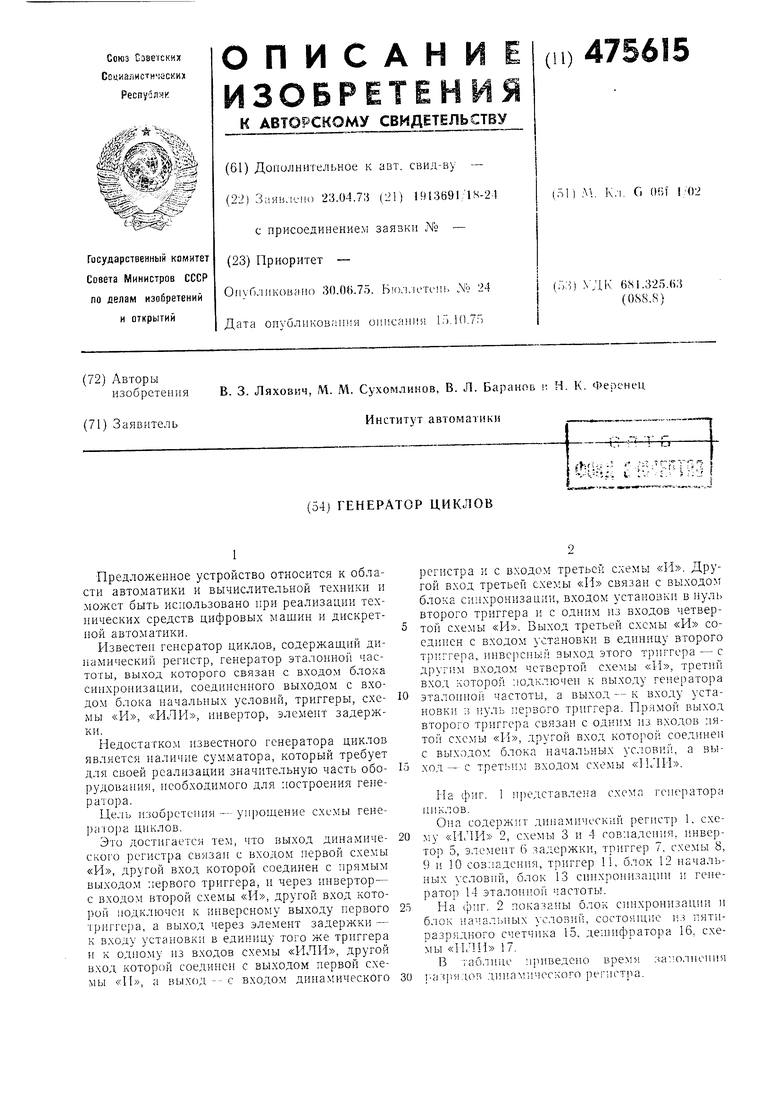

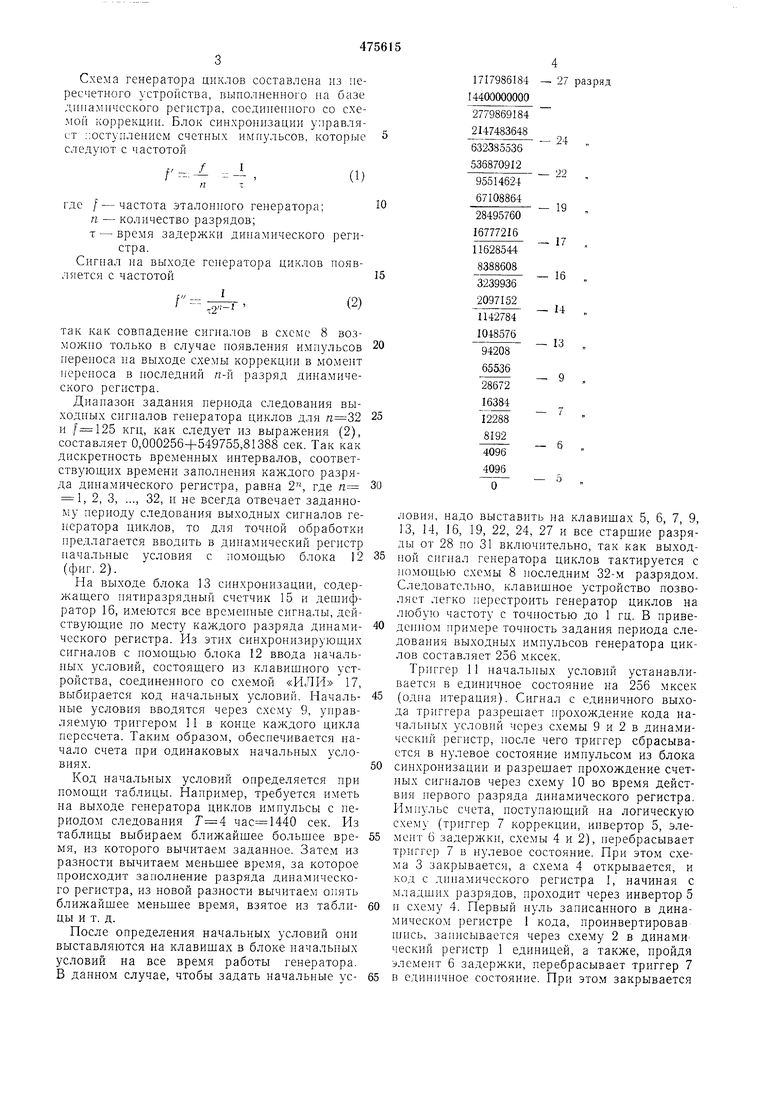

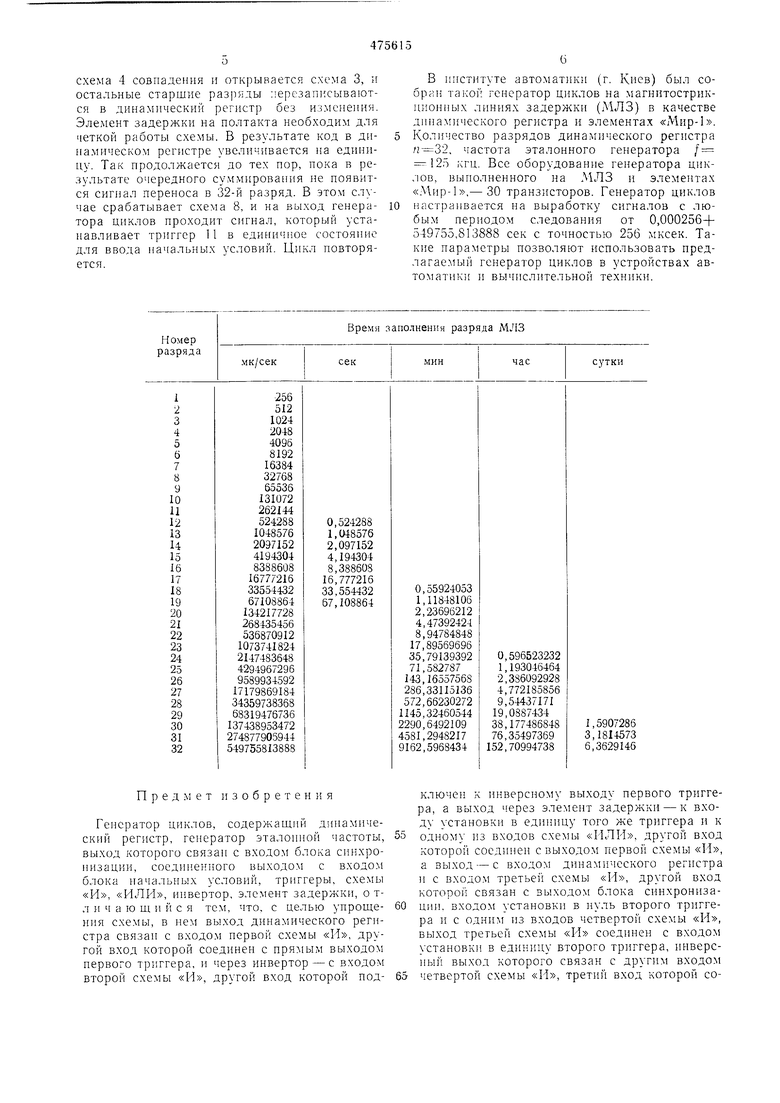

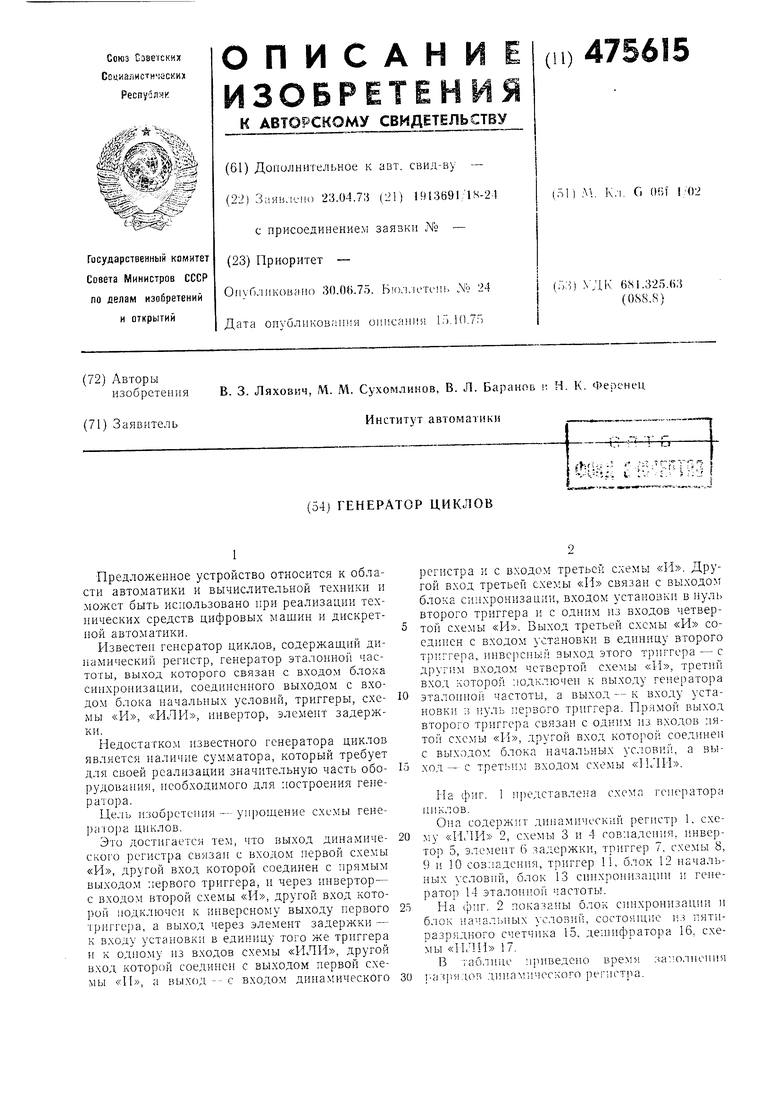

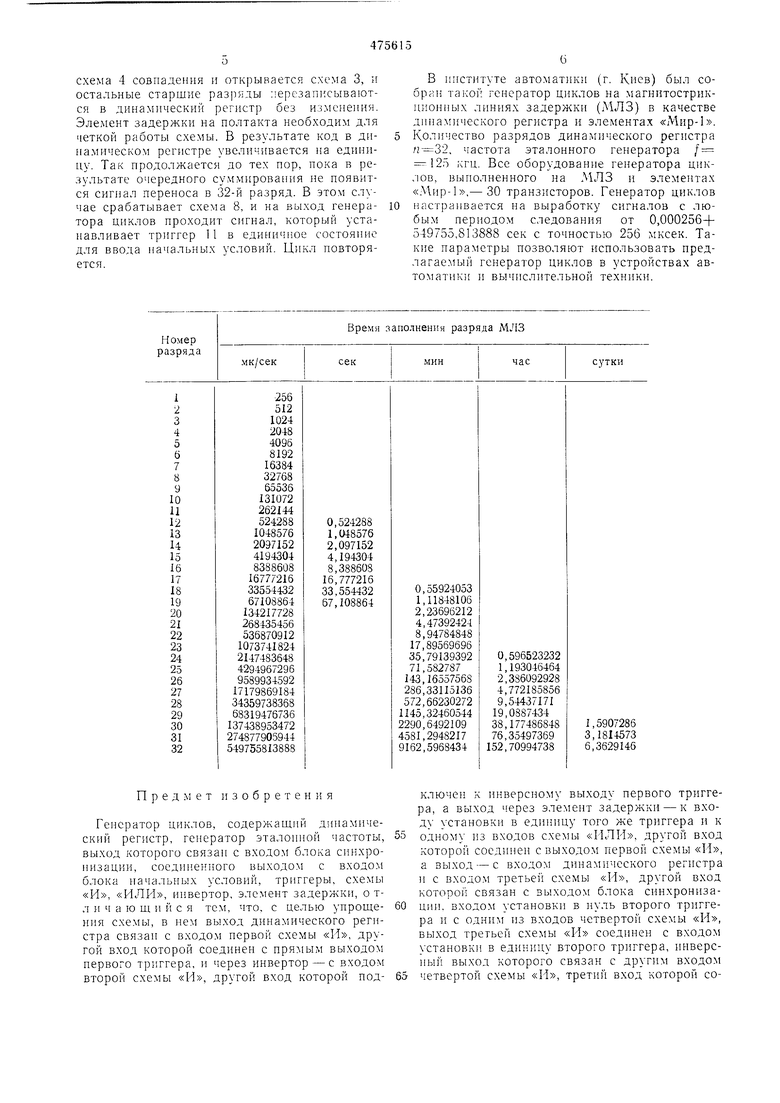

Схема генератора циклов составлена из иересчетного устройства, выполненного на базе динамического регистра, соединенного со схемой коррекции. Блок синхронизации управляет ;:оступлением счетных импульсов, которые следуют с частотой Р / 1 / --; - - - , где /-частота эталонного генератора; п - количество разрядов; т - время задержки динамического регистра. Сигнал на выходе генератора циклов появляется с частотой так как совпадение сигналоЕ5 в схеме 8 возможно только в случае нояв.тения имнульсов переноса на выходе схемы коррекции в момент иерепоса в последний п-й разряд динамического регистра. Диапазон задания периода следования выходных сигналов генератора циклов для и КГЦ, как следует из выражения (2), составляет 0,000256+549755,81388 сек. Так как дискретность временных интервалов, соответствующих времени заполнения каждого разряда динамического регистра, равна 2, где п 1, 2, 3, ..., 32, и не всегда отвечает заданному периоду следования выходных сигналов генератора циклов, то для точной обработки нредлагается вводить в динамический регистр начальные условия с помощью блока 12 (фиг. 2). На выходе блока 13 синхронизации, содержащего пятиразрядный счетчик 15 и дешифратор 16, имеются все времеиные сигналы, действующие по месту каждого разряда динамического регистра. Из этих синхронизирующих сигналов с помощью блока 12 ввода начальных условий, состоящего из клавищного устройства, соединенного со схемой «ИЛИ 17, выбирается код начальных условий. Начальные условия вводятся через схему 9, управляемую триггером 11 в коице каждого цикла пересчета. Таким образом, обеспечивается начало счета при одинаковых начальных условиях. Код начальных условий определяется при помощи таблицы. Например, требуется иметь иа выходе генератора циклов имиульсы с периодом следования сек. Из таблицы выбираем ближайщее больщее время, из которого вычитаем заданное. Затем из разности вычитаем меньшее время, за которое происходит заполнение разряда динамического регистра, из новой разности вычитаем опять ближайщее меньшее время, взятое из таблицы и т. д. После определения начальных условий они выставляются на клавищах в блоке начальных условий на все время работы генератора. В данном случае, чтобы задать начальные ус17I7986I84- 27 разряд 14400000000 2779869184 2147483648 632385536 536870912 95514624 67108864 28495760 16777216 11628544 ловия, надо выставить на клавищах 5, 6, 7, 9, 13, 14, 16, 19, 22, 24, 27 и все старщие разряды от 28 по 31 включительно, так как выходной сигнал генератора циклов тактируется с помопияо схемы 8 последним 32-м разрядом. Следовательно, клавищное устройство позволяет легко перестроить генератор циклов на любую частоту с точностью до 1 гц. В приведенном примере точность задания нериода следования выходных импульсов генератора циклов составляет 256 мксек. Триггер 11 начальных условий устанавливается в единичное состояние на 256 мксек (одна итерация). Сигнал с единичного выхода триггера разрешает прохождение кода начальных условпй через схемы 9 и 2 в динамический регистр, после чего триггер сбрасывается в нулевое состояние импульсом из блока синхронизации и разрешает прохождение счет)ых сигналов через схему 10 во время действия первого разряда динамического регистра. Импульс счета, поступающий на логическую схему (триггер 7 коррекции, инвертор 5, элемент 6 задержки, схемы 4 и 2), перебрасывает триггер 7 в нулевое состояние. Ири этом схема 3 закрывается, а схема 4 открывается, и код с динамического регистра 1, начиная с младших разрядов, проходит через инвертор 5 и схему 4. Нервый нуль записанного в динамическом регистре 1 кода, проинвертировав , записывается через схему 2 в динамический регистр 1 единицей, а также, пройдя элемент 6 задержки, перебрасывает триггер 7 в единичное состояние. При этом закрывается

схема 4 совпадения н открывается схема 3, и остальные старшие разряды : ерезап1 сываются в динамический регистр без изменения. Элемент задержки на полтакта необходим для четкой работы схемы. В результате код в динамическом регистре увеличивается на единицу. Так продолжается до тех пор, пока в результате очередного суммирования не появится сигнал переноса в 32-й разряд. В этом случае срабатывает схема 8, и на выход генератора циклов проходит сигнал, который устанавливает триггер 11 в единичное состояние для ввода начальных условий. Цикл иовторяется.

В институте автоматики (г. Киев) был собран такой генератор циклов на магнитострнкционных линиях задержки (МЛЗ) в качестве динамического регистра и элементах «Мир-1. Количество разрядов динамического регистра 32, частота эталонного генератора / 125 КГЦ. Все оборудование генератора циклов, выполненного на МЛЗ и элементах «Мир-1,- 30 транзисторов. Генератор циклов настраивается на выработку сигналов с любым периодом следования от 0,000256+ 549755,813888 сек с точностью 256 мкеек. Такие параметры позволяют использовать предлагае.мый генератор циклов в устройствах автоматики и вычислительной техники.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1973 |

|

SU485437A1 |

| УСТРОЙСТВО для ЗАДАНИЯ ГРАНИЧНЫХ УСЛОВИЙ | 1971 |

|

SU304603A1 |

| ГЕНЕРАТОР ЦИКЛОВ | 1971 |

|

SU291198A1 |

| Генератор циклов | 1977 |

|

SU693359A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Генератор циклов | 1976 |

|

SU647680A1 |

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для ввода информации | 1983 |

|

SU1091147A1 |

| Генератор циклов | 1981 |

|

SU995289A1 |

Предмет изобретения

Генератор циклов, содержащий динамический регистр, генератор эталониой частоты, выход которого связан с входом блока синхронизации, соединенного выходом с входом блока начальных условий, триггеры, схемы «И, «ИЛИ, инвертор, элемент задержки, о тл и ч а ю щ и и с я тем, что, с целью упрощения схемы, в нe выход динамического регистра связаи с входом иервой схемы «И, другой вход которой соединен с прямым выходом иервого триггера, и через инвертор - с входом второй схемы «И, другой вход которой подключен к инверсному выходу первого триггера, а выход через элемент задержки - к входу установки в единицу того же триггера и к одному 3 входов схемы «ИЛИ, другой вход которой соединен с выходом первой схемы «И, а выход - с входом динамического регистра и с входом третьей схемы «И, другой вход которой связан с выходом блока синхронизации, входом установки в нуль второго триггера и с одним из входов четвертой схемы «И, выход третьей схемы «И соединен с входом установки в единицу второго триггера, инверсиый выход которого связан с другим входом четвертой схемы «И, третий вход которой соединен с выходом генератора /lajioiuiOH ч ютоты, а выход--с входом установки ъ нуль нсрвого триггера, прямой выход второго григгера связан с одним ii3 входов нятой схимы -П,

t/

i

другой нход которой соединен с выходом бдока начадьных усдовий, а выход - с третьи%г 1. X о д о м схемы ; 11ЛI I ,-.

1

/7

Г

/J

г

13

риг.2

Авторы

Даты

1975-06-30—Публикация

1973-04-23—Подача