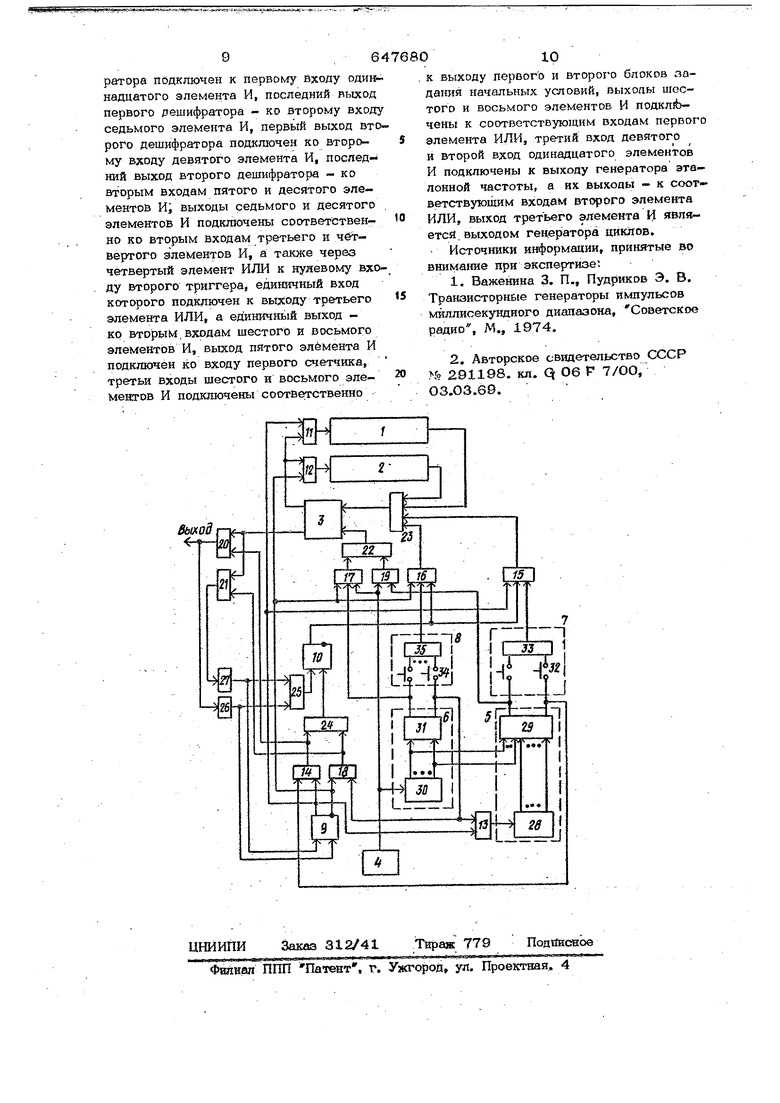

(54) ГЕНЕРАТОР ЦИКЛОВ чика подключены к соответствующим входам первого и второго дешифраторов, выходы второго дешифратора подключены к соответствующим входам -второго блок задаьгая начальных условий, выходы младших разрядов первого и второго ре гйстров сдвига подключены к cooTBetcri вующим входам первого элемента ИЛИ, выход которого подключен к первому входу сумматора, второй вход которого подключен к Выходувторого элемента ИЛИ, выход суммы сумматора подключен к первым входам первого и второго элементов И, выход переноса - к первым входам третьего и четвертого элементов И, выходы первого и второго элемен тов И подключены ко входам старших разрядов соответственно первого и второго регистров сдвига. Выходы третьего и четвертого элементов И подключены соответственно через первый элемент йадержки к первому входу третьего элемента ИЛИ и нулевому входу первого триггера и через второй элемент задёржки ко Второму входу третьего элемента ИЛИ и единичному входу первого триггера, единичный выгсод первого триг гера подключен ко второму входу первого элемента .И и первым вхо-; дом.пятого, шестого и седьмого элемен.тов И, нулевой выхрд первого триггера подключен ко второму входу второго элемента И и первым входам Восьмого, девятого, десятого элементов И, первый выход первого дешифратора подключен к первому входу одиннадцатого элемента И, последний выход первого дешифратора - ко второму входу седьмого элемен. та И, первьгй выход второго дешифратора подклк)чен ко второму входу девятого элемента И, последний выход второго дешифратора - ко вторым входам пятого и десятого элементов И, выходы сед мого и десятого элементов И подключены соответственно ко вторым входам третьего и четвёртйгб элементов Й а также через четвертый элемент ИЛИ к нулевому входу второго триггера, единичный вход которого) подключен к выходу третьего элемента ИЛИ, а единичный выход - ко вторым входам шестого ивосьмого элемент;ов И, выход пятого элемента И подключен ко входу первого счетчика, третьи входы шестого и восьмого элементов И подключены соответ ственйо k выходу первого и второго6лЫ ков задания начальных условий, выходы шестого и восьмого элементов И подключены к соответствующим входам первого Элемента ИЛИ, третий вход девятого и Второй вход одиннадцатого элементов И подключены к Выходу генератора Эталонной частоты, а их выходы - к соответствующим входам второго элемента ИЛИ, выход третьего эле-. мента И является выходом генератора циклов. Структурная схема генератора циклов представлена на чертеже. Генератор циклов первь,1й и второй регистры сдвига 1 и 2, сумматор 3, генератор 4 эталонной час- тоты, первый и второй блоки синхронивации 5 и 6, первый и второй блоки йадания начальных условий 7 и 8, пер-; вый и второй.триггеры 9 и 10, одиннадцать элементов И 11-21, четыре элемента ИЛИ 22-25, два элемента задержки 2 6-и 27. : Блок синхронизации 5 состоит из счетчика 28 и дешифратора 29. БлоК синхронизации 6 - из двоичного счетчика ЗО и дешифратора 31. Блок задания начальньтх условий 7 состоит из клавишного устройства 32 и элемента ИЛИ 33. Блок 8 задания начальных УСЛОВИЙ состоит из ютавишноГо устройства 34 и элемента ИЛИ 35, Генератор циклов работает следующи образом. .. : ,. Генератор эталонной частоты 4 вырабатывает импульсные сигналы с часто- . той , которые поступают на вход блока синхронизации 6- Счетчик 30 блока синхронизации 6 обеспечивает, деление .Эталонной частоты f в п раз. . . Дешифратор 31 вырабатывает на П выходах П последовательностей, синхронизирующих импульсов, сдвинутых друг относительно друга на ойин период эталонной частоты 1 . Таким образом, блок синхронизации 6 вырабатывает синхронизирующие им-. пульсы с частотой. i.i. п Число разрядов регистра сдвига 2 выбирается равным 7 . . Импульсы с последнего выхода блока,, синхронизации 6, действуюише с чао тотой i , поступают через элемент И 13 в счетчик 28 блока синхронизации 5.

Счетчик 28 собран на Kg триггерах и рсушествляет деление частоты i j в

24 раз.

Дешифратор 29 блока синхронизации 5 вырабатывает на УП выходах in последовательностей синхронизирующих Hf4пульсов, имеющих частоту i 2 сдвинутых друг относительно друга на один период эталонной частоты

:.(i na,i2 t/m).

Число разрядов регистра сдвига 1 выбирается равным Iri

Пусть в начальный момент триггер 9 находится в нулевом, триггер 10 в единичном состоянии и действует сигнал иа первом (слева) выходе блока синхронизации 6.

Импульсы с выхода генератора эталонной частоты 4 во время действия импульсов на первом выходе: блока синхронизации 6 начнут поступать через элементы И 17, ИЛИ 22 на первый вход сумматора 3..

Через элементы И 16 и ИЛИ 23 аа второй вход сумматора 3 с выхода блока начальных условий 8 начнет поступать, начиная с младших разрядов, последовательный -разрядный двоичный код начальных условий для регистра 2.

Последовательный .двоичный сумматор 3 вьшолняет cyMMHpoBaime кода начальных условий с импульсом, поступающим с выхода элемента ИЛИ 22, результат суммирования с выхода сумматора 3 через элемент; И 12 записывается в динамический регистр 2, после чего триггер 10 сбрасывается в нулевое состояние сигналом, поступающим с последнего выхода блока синхронизации 6 на инверсный вход триггера 10 через элементы И 18, ИЛИ 24.

После установки в нулевое состояние триггер 10 закрывает элемент И 16, запрещая дальнейшее поступление сигналов с выхода блока начальных условий 8 на второй вход сумматора 3.

Сумматор 3 вьшолняет суммирование последовательного Двоичного кодй поступающего с }выхода регистра 2, с импульсами первого выхода блока синхронизации 6, поступающими через элементы И 17, ИЛИ 22, до тех лор, пока во время действия сигнала на последнем вь1ходе блока синхроямзации 6 и на втором выходе сумматора 3 появится сигнал переноса, свидетельствующий о переполнении регистра 2. При этом ре-

гистр 2 устанавливается в начальное состояние.

Далее сигнал с последнего выхода

блока синхронизации 6 через элемент И 18, открытый сигналом с инверсного выхода триггера 9, и элемент И 21 поступит на вход элемента задержки 27. Элемент задержки 27 выполняет функцию задержки на полпериода эталонной час10тоты, после чего импульс с выхода элемента задержки 27 пройдет через элемент ИЛИ 25 на прямой вход триггера Ю, устанавливая его в единичное состояние, а на прямой вход тригг.

5 ра .9, переводя его в единичное состояние. Происходит переключение входов и выходов сумматора 3 на регистр 1, блока синхронизации 5 и блок начальных условий. 7.

о

Сигналы с последнего выхода блока синхронизации 6 начинают поступать чорез элемент И 13 на первый вход блока синхронизации 5. Счетчик 28 осуществляет деление частоты i в 2 раз.

25 На первом выходе блока синхроннзаиии . 5 сигналы начнут действовать с частотой f 2, , обеспечивая поступление с этой же частотой импульсов с выхода генератора эталонной частоты 4 через

0 элементы И 19, ИЛИ 22 на первый вход сумматора 3, на второй вход которого поступает через элементы И 15, ИЛИ 23, начиная с младщих разрядов, последовательный дво1гчный код, считы3Sваемый с Выхода блока начальных условий 7.

Сумматор 3 выполнит суммирование Ш -разрядного кода начальных условий блока 7 с импульсом первого выхода блока 5 синхронизации и результат суммирования запищется через элемент И 11 в. регистр 1, после чего триггер 1О установится в нулевое состояние сигналом, поступающим с последнего выхода блока синхроютзации 5 через элементы И 14, ИЛИ 24 на инверс1Пз1Й вход триггера 10.

СуМмЕггор 3 выполняет суммирование импульсов, поступающих с частотой i 2 с первого выхода блока синхрониfiзации 5 через элементы И 19, ИЛИ 22 на его первъй вход, с .т - разрядным йвоичкым кодом регистра 1 до тех пор,, пока на втором выходе сумматора 3 появится сигнал переноса во время дейстВ11Я сигнала на п.оследнем выходе блока синхронизашщ 5. Это произойдет, когда регистр 2 переполнится, в результате чего сработает элемент И 20, на который поступает сигнал с последне™ го выхода блока синхронизации 5 через элемент И 14.

Импульс с выхода элемента И 20 поступает на выход генератора циклов и па вход элемента задержки 26. Эле меит задеряжи 26 задерживает импульс на полпериода эталонной частоты, посл чего выходной сигнал элемента задерж ки 26 переводит триггер 9 в нулевое состояние и триггер 10 в единичное со стояшю,

Таким образом, все элементы схемы вep Iyлиcь в состояние, с которого начиналось описание работы устройства. В следующем периоде элементы генератора циклов работают- аналогично,. и на его выходе вырабатываются сигналы с эаданн;ь1М периодом следования.

Диапазон задания периода- следования Т выходных сигналов составляет

()n/ 6Ti2 %/i..

Задание периода соТедовапия выход-ных сигналов генератодД пиклов выполмется установкой начальных условий для регистра 1 с помошью клавишного устройства 32 блока начальных условий 7 и установкой начальных условий для регистра 2 с помощью клавишного устройства 34 блока начальных услови г 8.

Введение второго регистра 2, второго блока сиюсронизации 6 и второго блока начальных условий 8 существенно улучшает точности отработки заданного периодаследования.выходных сигналов. .

/Действительно, точность задания пе риода следования выходных сигналовв прёдло менном устройстве определяется временем задержки второго регистра 2 которое равно П/i .

В известном устройстве, точность задания периода след 1&ания выходных сигналов определяется, временем задер кки регистра сдвига, которое свявано с временем задержки первого регистраи временем задержки второго регистра предложенного Генератора ЦИКЛОВ сосэтношением

J&{rm.n)/i

При имеем

()j

т«е, точность задания периода следования выходных сигналов повышена в (2 +1) раз.

Формула изобретения

Генератор циклов, содержащий первый регистр сдвига, сумматор, элементы аадернски, триггеры, элементы И, ИЛИ, генератор эталонной частоты, первый счетчик выходы которого подключены к соответствующим входам первого дешифратора, выхоДы которого подключены к соответствующим входам пе)вого блока задания начальных , отличающийся- тем, что, с целью повышения точности задания периода следования выходАых импульсов, он содержит второй регистр сдвига, второй счетчик. Второй дешифратор, второй блок задания; начальных условий, причем вход второго счетчика подключен к выходу генератора эталонной частоты, выходы второго счетчика подключены к соответствующим входам первого я второго дешифраторов, выходы второго, дешифратора подключены; к соответствующим входам Вт орого блока задания начальных условий, выходы младших разрядов первого и второго регистров сдвига подключены, к соответствующим входам первого элемента ИЛИ, выход которого подключен к первому входу сумматора, второй вход которого подключен к выходу второго элемента ИЛИ, выход суммы сумматора подключен к первым входам первого и второгоэлементов И, выход переноса - к первым входам третего и четвертого элементов И, выходы первого и второго элементов И подклю- 1ФЫ ко входам ст.арщих разрядов со ответственно первого и второго perHCTw ров сдвига, выходы третьего и четвертого элементов И. подключены соответственно через первый элемент задержки к первому входу третьего элемента ИЛИ к нулевому входу первого триггера и через второй элемент задер кки ко второму входу третьего элемента ИЛИ и единичному входу первого триггера, единичный выход первого триггера подключен ко второму входу первого элемента И и первым входам пятого, шестого и седьмого элементов И, нулевой выход первого триггера подключен ко второму входу второго элемента И и первым вхЬдам восьмого, девятого, десятого элементов И, первый выход первого дешиф

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Генератор циклов | 1981 |

|

SU995289A1 |

| Генератор циклов | 1977 |

|

SU693359A1 |

| Устройство для диагностирования цифровых блоков | 1988 |

|

SU1631546A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

Авторы

Даты

1979-02-15—Публикация

1976-08-01—Подача