(54) ГЕНЕРАТОР ЦИКЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1977 |

|

SU693359A1 |

| Генератор циклов | 1978 |

|

SU744531A1 |

| Генератор циклов | 1976 |

|

SU647680A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Генератор циклов | 1981 |

|

SU995289A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1642585A1 |

| Многоканальное устройство для до-пуСКОВОгО КОНТРОля пАРАМЕТРОВ | 1979 |

|

SU840819A1 |

1

Изобретение относится к автоматике и вычислительной технике и предназначено для одновременного генерирования по не« скольким каналам импульсных сигналов с заданными периодами следования.

Известен генератор циклов, содержащий динамический регистр, выход которого связан с одним из входов последовательного двоичного сумматора, другие входы которого соединены с выходами блока синхронизации, связанного входом с выходом генератора эталонной частоты, и блока ввода начальных условий соответственно, причем выходы блока синхронизации связаны с входами блока ввода начальных условий, а

выход последовательного двоичного сумматора соединен с входом динамического регистра. При этом отсутствует возможность генерирования выходных сигналов с заданной частотой следования импульсов по нескольким каналам одновременно.

Цель изобретения - расширение класса решаемых задач таким образом, чтобы один генератор циклов позволял получить по нескольким каналам независимые выходные сигналы с заданной частотой следования импульсов.

Достигается это тем, что в генератор циклов введен блок многоканального вывода, каждый канал которого состоит из схемы И и триггера, причем один из входов первой схемы И каждого канала подключен к выходу второй схемы И, один из входов которой связан с выходом последовательного двоично1Х сумматора, а другой - с шиной установки-в нуль триггеров каждого канала, второй вход первой схемы И каждого канала связан с соответству ющим выходом блока синхронизации, а ее выход - с входом установки в единицу триггера, прямой выход которого соединен с соответствующим входом блока ввода начальных условий.

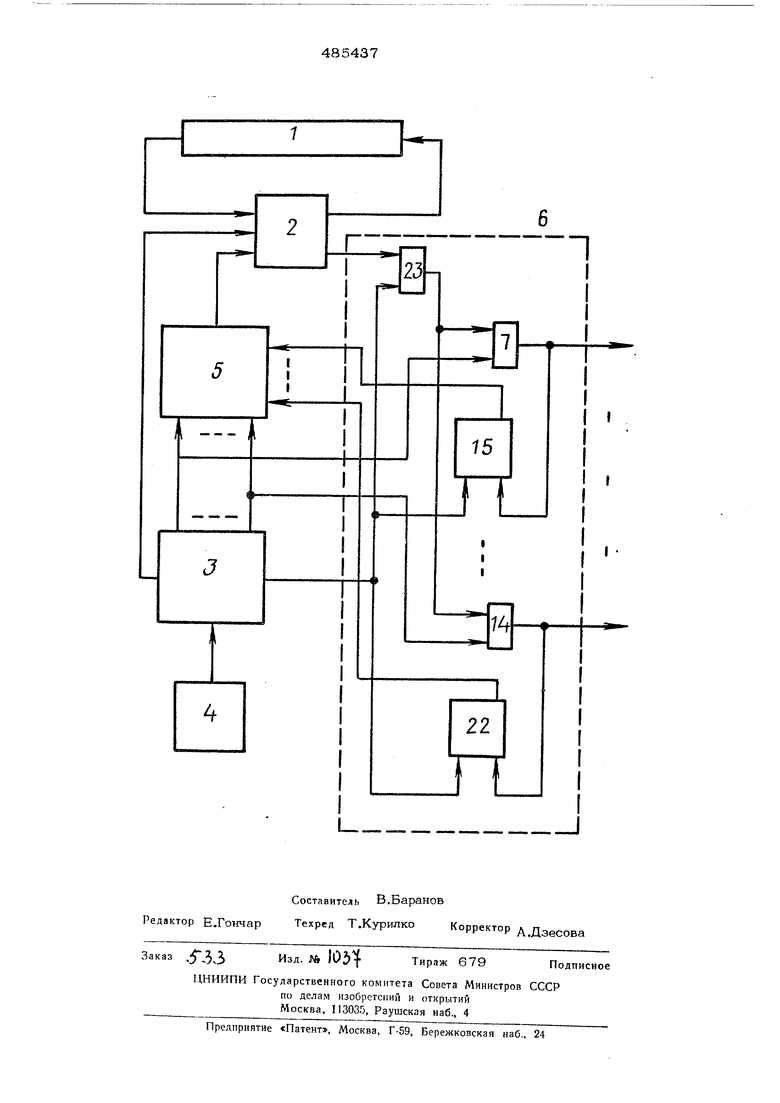

На чертеже изображен генератор циклов.

Устройство состоит из динамического регистра 1, последовательного двоичного сумматора 2, блока синхронизации 3, генератора 4 эталонной частоты, блока 5 ввода начальных условий, блока 6 многоканального вывода, состоящего из схем 1-1

и триггеров. Количество схем И и триггеров определяется числом Ш независимых выходных каналов генератора циклов. На чертеже для случая т -& изображены первые схемы И 7-14, триггеры 15-22 и вторая схема И 23.

Блок синхронизации 3 обеспечивает по ступление от генератора 4 эталонной частоты Б сумматор 2 счетных импульсов с частотойя f{i)

ti

1

f - эталонная частота генератора,

ГЦё П - количество разрядов динамиIческого регистра, необходимое для генерирования сигналов по одному выходу.

Максимальная частота импульсных сиг iianoB на каждом из выходов генератора циклов определяется временем задержкиtT импульсного сигнала в динамическом регистре 1f f

(2)

2-7Гт- Т

1-де т - количество выходов генератора циклов.

-- Величина П-ТП равна полному кода- честву двоичных разрядов динамического регистра 1. Поэтому в динамическом регистре 1 могут храниться Ш j№OH4Hbix кодов, каждый из которых представляется I М двоичными разрядами.

Соединение динамического регистра с последовательным двоичным сумматором 2 образует счетчик импульсов, поступающих от блока синхронизации 3 с частотой f . Счетные импульсы поступают во

все первые (младшие) разряды двоичных кодов динамического регистра,

Блок синхронизащш 3 вырабатывает также другие синхронизирующие сигналы с частотой f , которые поступают на

вход второй схемы И 23 и шину установки в нуль триггеров 15-22 каждого канала. Эти синхронизирующие сигналы I сов)адс1ют по времени с моментом прохождения1 -ых разрядов динамического регистра 1 через умматор 2,

. Л

С-шлалы на выходах генератора циклов

вырабатываются в моменты появления импульс ов переноса на выходе сумматора 2 в каждыйfl -ый разряд динамического

регистра 1, Сигналы переносов в tl -ый разряд 11 л ходят через схему И 23 и одну из первых схем И 7-14 каждого канала, управляемых сигналами блока синхронизации 3 следующими с частотой f- ,

Нсли начальные условия, вырабатывае Мые блоком 5, будут нулевыми, то сигнал

на каждом из fn выходов генератора циклов появляется с частотой

(3)

1

. 2 Диапазон задания периода следования

сигналов на каждом из , tn выходов генератора циклов для , П -32 и / 500 КГЦ, как следует из (2) и (3) составляет О,ООО512-1099511,627776 сек,

, Так как дискретность временных интервалов соответствующих времени залолне(ния каждого разряда динамического регистра 1 равна 2, где П 1, 2, 3, „,, и не всегда отвечает заданному периоду следования выходньрс сигналов генератора циклов, то дан точной обработки в динамический регистр 1 вводятся начальные условия с помощью блока 5, Блок 5 позволяет набирать начальные условия на Ш клавишных устройствах в виде П разрядных двоичных чисел.

Двоичные коды начальных условий формируются блоком 5 из импульсов блока синхрнизации 3,. :

Частота cneflOBaiiuja импг/льсных сигнало на каждом из /Ч выходов не зависит от друга и полйостью- определяется Д разрядным дэоичньгм кодом, выставле1шым на соответствующем клавищном устройстве (блока ввода начальных условий 5.

Начальные условия вводятся через сумматор 2 в динамический регистр 1 при запуске генератора циклов и в конце каждого цикла пересчета в момент генерирования выходного сигнала из Щ выходов,

В момент запуска генератора циклов триггеры 15-22 блока многоканального вывода 6 устанавливаются в единичное состояние.

Сигнал от единичного выхода триггера 15 разрешает прохождение кода начальных условий из блока 5 на вход сумматора 2, Как только последний разряд кода начальны условий, составленного для первого выхода генератора циклов, пройдет на вход сумматора 2, триггер 15 сбросится в кулевое состояние сигналом, поступающим из блока синхронизации 3.

Аналогинным образом записываются в динамический регистр 1 через сумматор 2 коды начальных условий, составленные дня всех вькодов генератора циклов. Например, код начальных условий для последаего выхода генератора циклов пройдет на вход сумматора 2 по сигналу с еданичного выхода триггера 22, который возвращается в нулевое состояние после записи начальных условий в динамический регистр 1, .

В рассматриваемом примфе все восемь тридцатидвухразрядных кодов начальных условий запшиутся в динамический регистр 1 в течение 512 мк сек. Коды начальных условий суммируются со счетными импуль сами, посоупакацими из блока синхронизаци 3, во время прохождения млада1его разряд каждого кода через сумматор 2. В результате суммированнг все восемь кодов начальных условий увеличиваются на единипу младшего разряда. Новые коды, полученные в результате суммирования, записываются в динамический регистр 1, откуда через интервал времени ,Т 5Г2 мк сек они вновь поступают на вход сумматора 2 и суммируются со счетными CHI {налами и т. д. Так продолжается до тех пор, пока в результате очередного суммирования на выходе сумматора 2 не появится сигнал переноса в 32-й разряд. В этом случае срабатывает схема И 23 и на одном из выходов генератора циклов по синхронизирующему сигналу появится импульсный сигнал. Допустим, например, что заданная частота по первому выходу генератора цик;юв больше, чем заданная частота по дру гим выходам. Тогда срабатывает схема И 7, которая пропустит сигнал от схемы И 23 на первый выход генератора цикI лов. Этим же выходным сигналом устанав|ливается в единичное состояние триггер 15, который восстановит код начальных условий только для первого выхода генератора циклов. Цикл генерирования импульс ;Ных сигналов по первому выходу генератоjpa циклов повторяется. I Аналогичным образом осуществляется генерирование импульсных сигналов по все остальным выходам генератора циклов. Например, если сигнал переноса в 32-й разряд появится во время действия синхро/ визирующего сигнала на шине второго вхо да схемы И 14, то этот сигнал переноса с выхода сумматора 2 через схемы И |j23 и И 14 поступит на восьмой выход генератора циклов и установит триггер 22 в единичное состояние для ввода начальных условий, выставленных на клавищном устройстве блока 5 для восьмого выхода генератора циклов. Цикл генерирования импульсных Сигналов по восьмок1у выходу повторяется, В рассмотренном примере блок многоканального вывода 6 совместно с блоком ввода начальных условий 5 позволяет по каждому из (Ц 8 выходов генератора циклов получить независимо fjpyr от друга любую частоту следования импульсных си1 налов с точностью Г 512 мк сек. Предмет изобретения | Генератор циклов, содержащий динамический регистр, выход которого связан с одним из входов последовательного двоичного сумматора, другие входы которого соединены с выходами блока синхронизации, связанного входом с выходом генератора эталойной частоты , и блока ввода начальных условий соответственно, причем выходы блока синхронизации связаны с входами блока ввода начальных условий, а выход последовательного двоичного сумматора соединен с входом динамических) регистра, отли чающийся тем, что, с целью расширен|1Я класса решоемых задач, в него введен блок многоканального вывода, каждый канал которого состоит из схемы И и триггера, причем один из входов первой схемы И каждого качана подключен к выходу второй схемы И, один из входов которой связан с выходом последовательного двоичного сумматора, а другой - с шиной установки в нуль три1 геров каждого канала, второй вход первой схемы И каждого канала связан с соответствующим выходом блока снлхропнзишш, а ее выход - с входом установки в единицу триггера, прямой выход которо1-х) соединен с соответствующим входом блока ввода начальных условий.

Авторы

Даты

1975-09-25—Публикация

1973-04-23—Подача