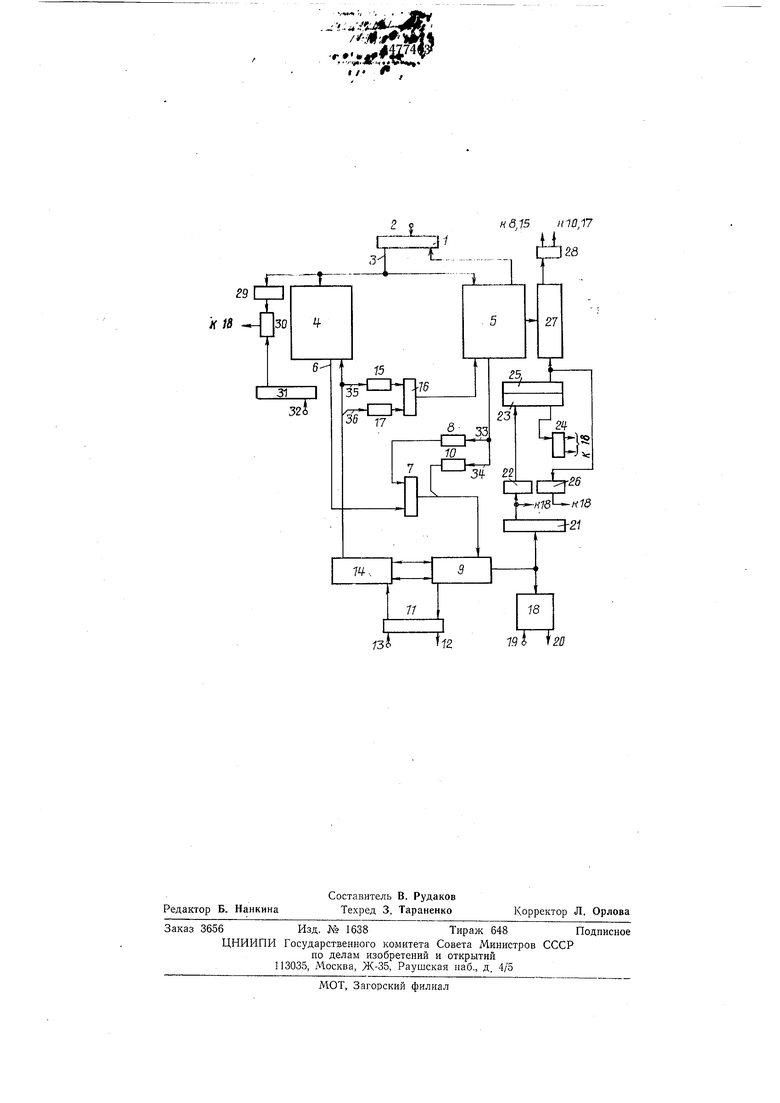

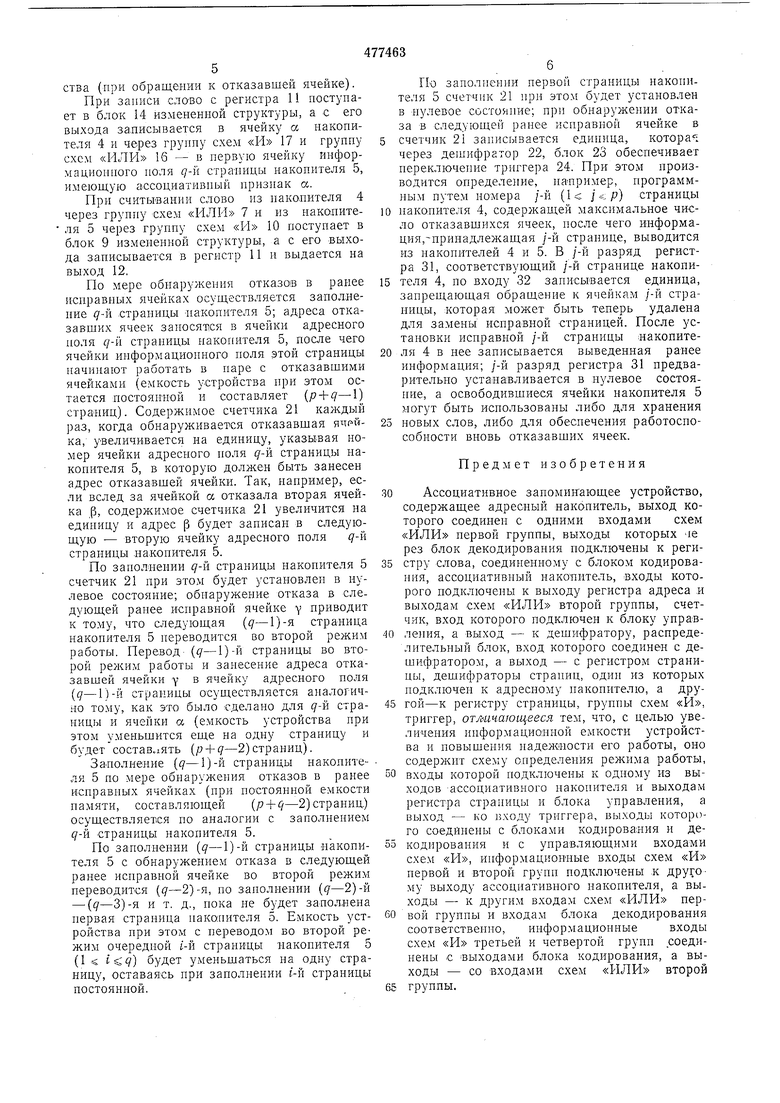

пы, с другими входами которых через первую группу схем «И 8 связан выход накопителя 5, а выходы схем «ИЛИ 7 соединены со входом блока декодирования 9. Выход иакоиителя 5 через вторую группу схем «И 10 связан со входом блока 9. Выход блока 9 соединеи с одним входом регистра слова И, имеющим выход 12 и другой вход 13. Другой выход регистра И связан со входом блока кодирования 14. Выход блока 14 соедииен со входом накоиителя 4 и через третью группу схем «И 15 - iC одними входами схем «ИЛИ 16 второй группы, с другими входами которых связаны через четвертую группу схем «И 17 выходы блока 14, а выходы схем «ИЛИ 16 соединеиы со входом накоиителя 5.

Управляющий выход блока 9 связан с блоком уиравления 18, имеющим вход 19 и выход 20, и со входом счетчика 21. Выход счетчика 21 соединен с блоком 18 и через дешифратор 22-со входом распределительиого блока 23. Выход блока 23 связан со входо.м триггера переполиения 24, выходы которого соедииены с блоком 18. Блок 23 связан с регистром страницы 25, содержащим р разрядов (но числу страниц накопителя 5). Выход регистра 25 соединен через ден1ифратор страницы 26 с блоком 18 и неиосредственно- с одним входом схемы 27 определения режима работы. Другой вход схемы 27 связан с выходом накопителя 5, а выход соединен со. входом триггера 28. Один выход триггера 28 овязаи с управляющими входами схем «И 8, 15, а другой - с управляющими входами схем «И 10, 17; кроме того, оба выхода триггера 28 соединены со входами блоков 9 и 14.

Выход регистра 1 связан через дешифратор страницы 29 с однимн входами .схем «И 30 пятой грунны. Другие входы схем «И 30 соединены с выходом регистра 31 разрешения обращения к странице, содержащего р разрядов (по числу страниц в накопителе 4), а выходы схем «И 30 связанны с блоком 18. Регистр 31 имеет вход 32.

Входы 33 и 34 схем «И 8 и 10, а также входы 35 и 36 схем «И 15 и 17, нодключенные соответственно к выходам накопителя 5 и блока 14, являются информационными.

Устройство работает следующим образом.

В исходном состоянии, когда в устройстве отсутст1вуют отказавшие ячейки, счетчик 21, регистр 25, триггеры 24 и 28 и регистр 31 находятся в нулевом состоянии, по мере появления ячеек с отказами содержимое счетчика 21 и регистра 25 будет изменяться, соответственно будет меняться режим работы накопителя 5.

28 задает один из двух возможных режимов работы устройства в зависимости от того, к исправной или отказавшей ячейке происходит обращение.

Допустим, до данного момента в устройстве отсутствовали отказавшие ячейки. При

этом все страницы накоиителя 5 работают в первом релсиме.

При обращении к ячейке а (l a-C/V+.K) адрес ее записывается на регистр 1. Триггер 28 остается в исходном положепии (даже если ячейка находится к накопителе 5 (N+{ а N+ 1 и из него в схему 27 ноступает сигиал наличия адреса).

При записи слово с регистра 11 ностунает в блок 14 и занисывается в накопитель (прн 1 а Л ) или через грунну схем «PI 15 и грунну схем «ИЛИ 16 - в накопитель 5 (ЛН-1-а N+.).

При считывании слово из накоиителя 4

через группу схем «ИЛИ 7 либо пз накопителя 5 через группу схем «И 8 и группу схем «ИЛИ 7 поступает в блок 9, а с его выхода записывается в регистр 11. Блок 9 оиределяет иаличие отказа в ячейке и, если

ячейка исправна, слово с регистра 11 выдается ia выход 12.

В случае обнаружения отказа в ячейке а правильное слово получают, папример, путем считывания из впеишей памятн, (на чертеже

не показана), затем, например, последняя (-я) страница накопителя 5 переводится во второй режим работы, при KOTOipOM ячейки ее будут использоваться для обеспечения работоснособности отказавших ячеек устройства,

в частности, ячейки ос (емкость устройства нри этом уменьшнтся на одну страницу и будет составлять (p + q-1) страниц). Перевод (7-й страницы накопителя 5 во второй режим работы осуществляется следующим образом. Прн обнаружении отказа в счетчик 21 заиисывается единица, которая через дешифратор 22, блок 23 постуиает, иаиример, в (7-й разряд регистра 25, соответствующий странице накопителя 5. После дешифрации

на выходе дешифратора 26 появляется сигнал на освобождение -й страницы иакоиителя 5, по которому ппформация из этой страницы выводится в другое запоминающее устройство. Затем, напрнмер, в нервую ячейку адресного поля q-ii страницы накоиителя 5, нереведенной во второй режим работы, заносится адрес отказавшей ячейки о;, предварительно записанный в регистр 1.

Прн обращении к отказавшей ячейке а после записи ее адреса в регистр 1 из накопителя 5 в схему 27 поступает сигпал наличия адреса и происходит переключение триггера 28 (так как в q-w. разряд регистра 25,

соответствующий q-к странице накопителя 5, содержащей ячейку а, занисаиа единица). Триггер 28, нереключаясь, осуществляет изменение структуры блоков 9 и 14 таким образо.м, что, если раньще они иснользовали,

иапример, групповой код (П, /о), то после изменения их структуры оин используют групповой код («2, /г), где HZ 1п. В этом случае устройство переводится во второй режим работы.

Рассмотрим второй режим работы устройства (при обращении к отказавшей ячейке).

При записи слово с регистра 11 иоступает в блок 14 измененной структуры, а с его выхода записывается в ячейку ос накопителя 4 и через группу схем «PI 17 и грунну схем «ИЛИ 16 - в первую ячейку ипформациоииого поля -й страницы накопителя 5, имеющую ассоциативный признак ее.

При считывании слово из наколителя 4 через группу схем «ИЛИ 7 н из накопителя 5 через группу схем «И 10 поступает в блок 9 измененной структуры, а с его выхода записывается в регистр 11 н выдается на выход 12.

По мере обнаружения отказов в ранее иснравных ячейках осуществляется занолиение -й страницы накопителя 5; адреса отказавших ячеек заносят1ся в ячейки адресного ноля С/-Й страницы накопителя 5, носле чего ячейки ииформационного поля этой страницы начинают работать в паре с отказавшими ячейками (емкость устройства при этом остается ностояииой и составляет (p + q-1) страниц). Содержимое счетчика 21 каждый раз, когда обнаруживается отказавшая ячрйка, увеличивается на единицу, указывая номер ячейки адресного ноля q- страницы накопителя 5, в которую должен быть занесен адрес отказавшей ячейки. Так, например, если вслед за ячейкой а отказала вторая ячейка р, содержимое счетчика 21 увеличится на единицу и адрес (3 будет записан в следующую - вторую ячейку адресного ноля q-ii страницы .накопителя 5.

По занол«ении страницы накопителя 5 счетчик 21 при этом будет установлен в нулевое состояние; обнаружение отказа в следующей ранее иснравной ячейке у нрнводит к тому, что следующая (q-1)-я страница паконителя 5 переводится во второй режим работы. Перевод (q-1)-й страницы во второй режим работы и заиесение адреса отказавшей ячейки Y в ячейку адресного поля (q-1)-й страницы осуществляется аналогично тому, как это было сделано для (/-и страницы и ячейки а (емкость устройства при этом уменьшится еще на одну страницу и будет состав.1ять (p + q-2)страниц).

Заполнение (q-1)-й страницы наконителя 5 но мере обнаружения отказов в ранее иснравных ячейках (при постоянной емкости памяти, составляющей (p + q-2) страниц) осуществляется но аналогии с заполнением страницы накопителя 5.

По заполнении (q-1)-й страницы накопителя 5 с обнаружением отказа в следующей ранее иснравной ячейке во второй режим переводится (q-2)-я, по заполнении (17-2)-и - (q-3)-я и т. д., пока не будет заполлена нервая страница иако:нителя 5. Емкость устройства при этом с переводом во второй режим очередной t-й страницы наконителя 5 (I tc) будет уменьшаться на одну страницу, оставаясь при заполнении t-й страницы ностоянной.

По заполнении первой страницы накопителя 5 счетчик 21 при этом будет установлен в нулевое состояние; при обнаружении отказа в следующей ранее иснравной ячейке в

счетчик 21 записывается единица, котора; через дешифратор 22, блок 23 обеспечивает нереключение трнггера 24. При этом производится определенне, например, программным путем номера /-и (1 I р) страницы

накопнтеля 4, содержащей максимальное число отказавшихся ячеек, после чего информация,-принадлежащая /-Й странице, выводится нз накопителей 4 и 5. В /-и разряд регистра 31, соответствующий /-и странице наконителя 4, по входу 32 записывается единица, запрещающая обращение к ячейкам /-и страницы, :которая может быть теперь удалена для замены исправной страницей. После установки иснравной /-Й страницы «аконителя 4 в нее записывается выведенная ранее информация; /-и разряд регистра 31 предварительно устанавливается в нулевое состояние, а освободившиеся ячейки накопителя 5 могут быть иснользованы либо для хранения

новых слов, либо для обеснечения работоспособности вновь отказавших ячеек.

Предмет изобретения

Ассоциативное запоминающее устройство, содержащее адресный наконитель, выход которого соединен с одними входами схем «ИЛИ иервой группы, выходы которых -le рез блок декодироваиия подключены к регистру слова, соединенному с блоком кодирования, ассоциативный накопнтель, входы которого нодключены к выходу регистра адреса ,и выходам схем «ИЛИ второй группы, счетчик, вход которого подключен к блоку унравлеиия, а выход - к дешифратору, раснределительиый блок, вход которого соединен с дешифратором, а выход - с регистром странины, дешифраторы страниц, один из которых подключен к адресному накопителю, а другой-к регистру страннцы, группы схем «И, триггер, отличающееся тем, что, с целью увеличения информационной емкости устройства и повышения надежности его работы, оно содержит схему определения режима работы,

входы которой нодключены к одному из выходов ассоциативного иаконителя и выходам регистра страницы и блока управления, а выход - ко входу триггера, выходы которого соединены с блокамн кодирования и декодирования и с управляющими входами схем «И, ииформациоиные входы схем «И нервой и второй груин нодключены к другому выходу ассоциативного наконителя, а выходы - к другим входам схем «ИЛИ первой группы и входам блока декодирования соответственно, ииформациониые входы схем «И третьей и четвертой групп соединены с выходами блока кодирования, а выходы - со входами схем «Р1ЛИ второй

группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1972 |

|

SU437127A1 |

| Запоминающее устройство | 1972 |

|

SU448480A1 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU595795A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU720516A1 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU600618A1 |

| Запоминающее устройство | 1973 |

|

SU450231A1 |

| Запоминающее устройство | 1975 |

|

SU529481A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1974 |

|

SU492000A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

75 121}

1зГtf2

Авторы

Даты

1975-07-15—Публикация

1972-11-13—Подача