(54) Зу ПОМ-1НАЮШЕЕ УСТРОЙСТВО

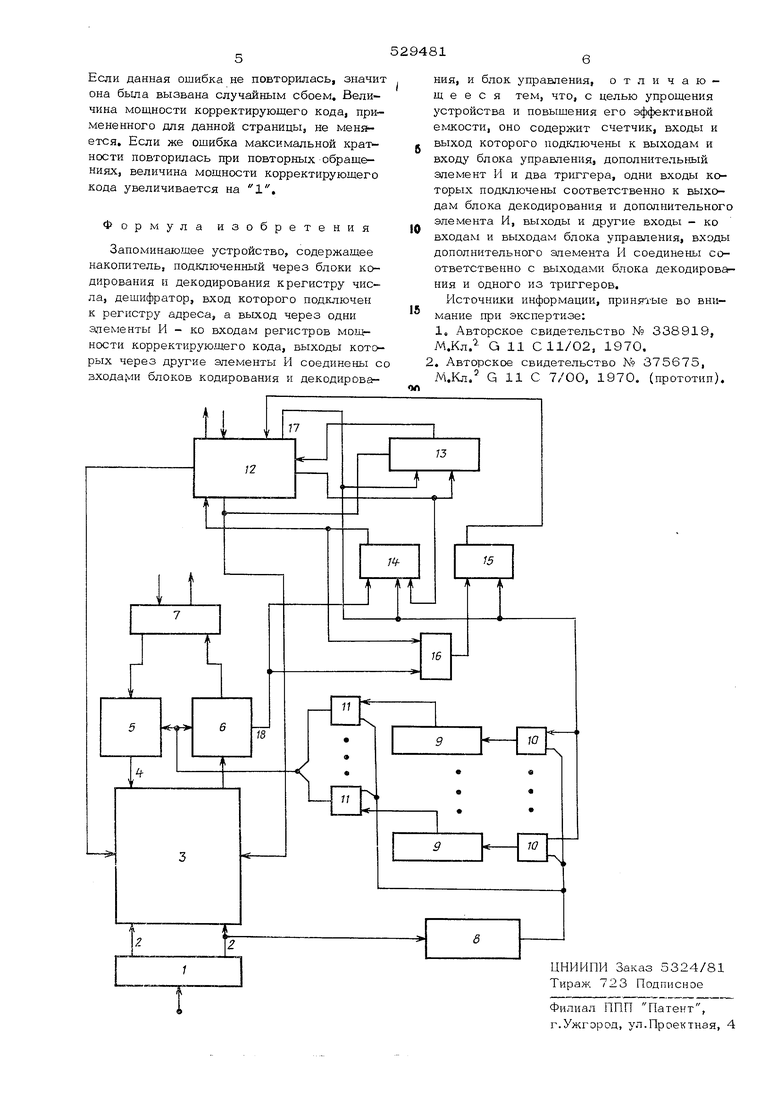

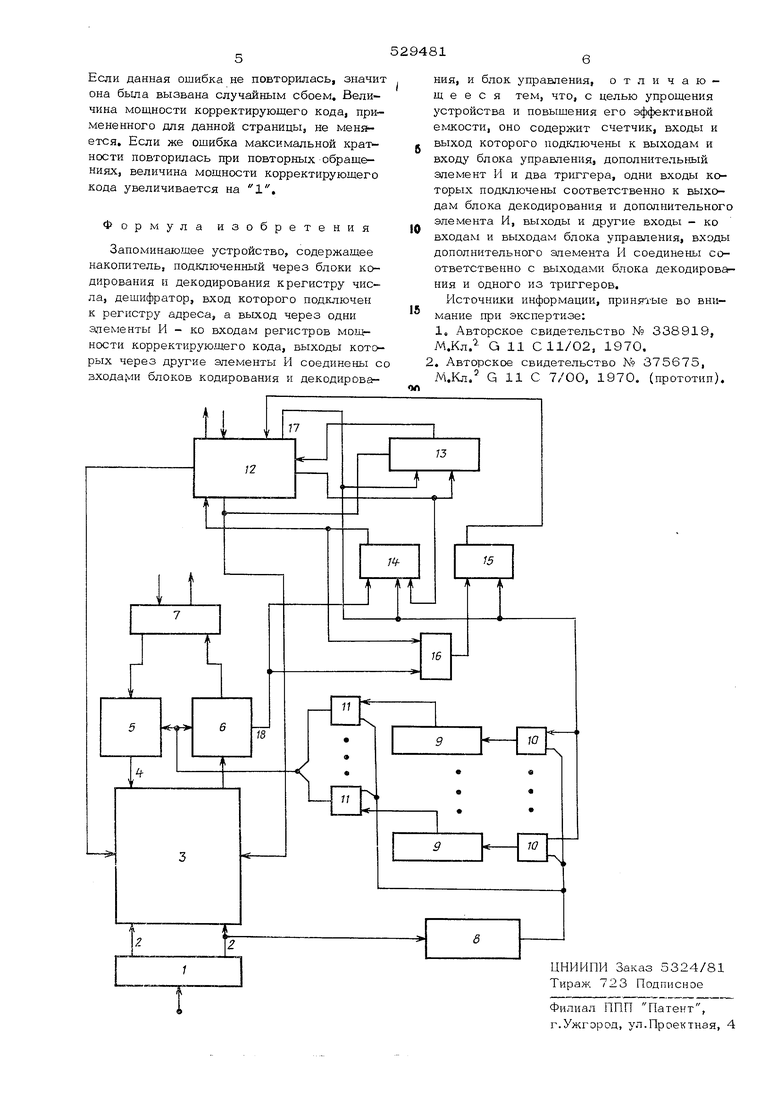

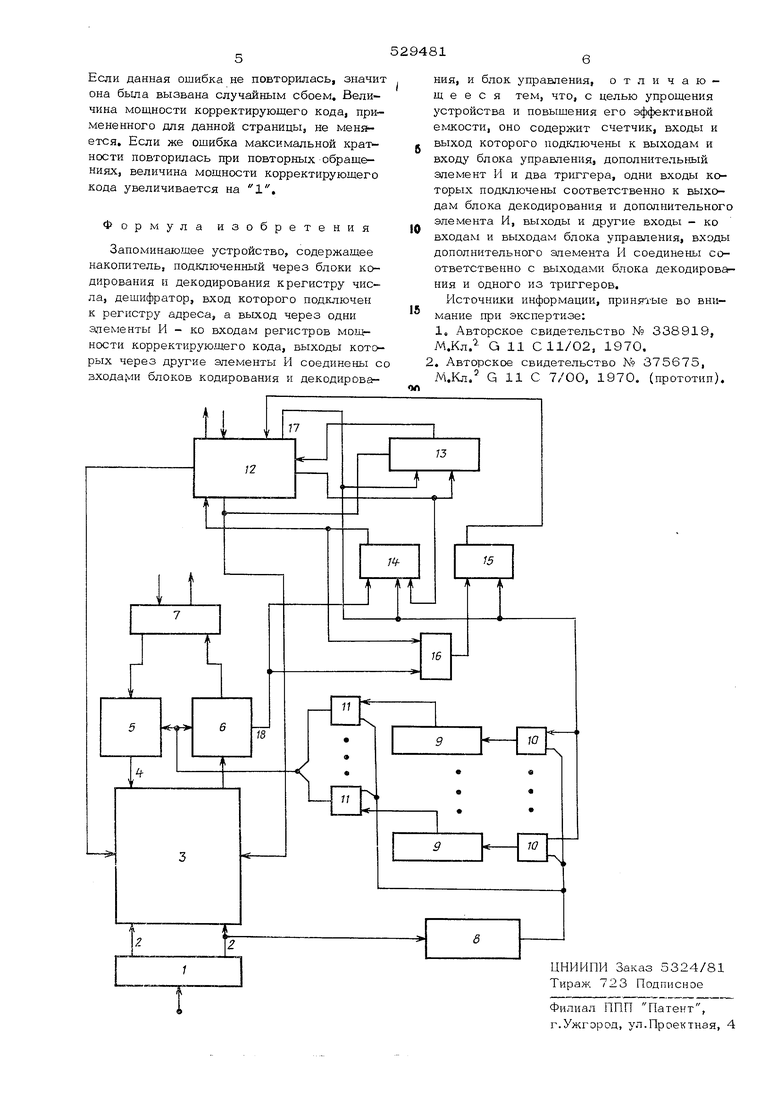

На чертеже изображена структурная электрическая схема предл-агаемого запоминающего устройства.

Устройство содержит регистр адреса 1 выходы 2 которого соединены с накопителем, 3, вход 4 которого соединен с выходом блока кодирования 5, блок декодирования 6, регистр числа 7, Выход старших разрядов регистра адреса 1 соединен со входом дешифратора 8, выход которого соединен с регистрами мощности корректирующего кода 9 через элементы И 10, Выходы регистров мощности корректирующего кода 9 соединены с одними входами элементов И 11, выходы которых подключены к, управляющим входам блоков кодирования 5 и декодирования 6, Другие входы апементов И 11 соединены с выходом дешифратора -8, Кроме того, устройство содержит блок управления 12, счетчик 13, два триггера 14 и 15 и дополнительный элемент И 16 Выход 17 блока управления 12 соединен со входами апементов И 10 и со входами установки в О счетчика 13 к триггеров 14 и 15, Вход установки в 1 триггера 14 соединен со входом дополнительного элемента И 16 с выходом 18 блока декодирования 6« Выход триггера 14 соединен со входами блока упраааения 12 и дополнительного элемента И 16, выход которого подключен ко входу установки в триггера 15, Вьгход последнего связан с блоком управления 12s соединенным с выходом счетчика 13, с накопителем 3, со счетным входом счетчика 13, со входами установки в О счетчика 13 и триггера 14.

Запоминающее устройство работает следующим образом.

Код адреса ячейки, к которой производится обращение, поступает на регистр адреса 1, Код старших разрядов регистра адреса 1 поступает на дешифратор 8, который открывает один из элементов И 11, Блоки кодирования 5 и декодирования 6 настраиваются на обработку корректируюего кода, мощность которого равна чису, записанному в выбранном регистре мощности корректирующего кода Запись числа выбранную ячейку происходит обычным образом. Число из регистра числа 7 потупает на боток кодирования 5 и записыается в выбранную ячейку накопителя 3«

В режиме чтения число из выбранной чейки накопителя 3 поступает на блок екодирования 6 и записывается на реистр числа 7„

При работе блока декодирования 6 в ежиме чтения возможны два случая.

В первом случае блок декодирования 6 при обращении к L -ой ячейке исправил (tTi-i- 1) ошибку, где (гл т 1) число, записанное в соответствующем регистре мощности корректирующего кода 9, а m - максимальное число отказов в одной из ячеек данной страницы. Информация при этом не теряется. Выбранное слово из регистра числа 7 выдается в вычислительную машину. На выходе 18 блока декодирования 6 вырабатывается сигнал о максимальном использовании мoщ iocти корректирующего кода. По этому сигналу триггер 14 устанавливается Б единичное состояние, по которому блок управления 12 выдает сигналы на повторное обращение к I -ой ячейке накопителя Одновременно с каждым обращением к накопителю подается сигнал -T-l в счетчик 13, Если при N повторНЬ1Х обращениях к i -ой ячейке сигнал о максимальном использовании мощности корректирующего кода не повторио/ся, т,е при первом обращении к i ой ячейке имел место случайный сбой, к содержи;-юму регисстра мощности корректирующего кода 1 не Г рибавляется, По сигналу N счетчика 13 блок управ,аепия 12 устанааливает

в О счетчик 13

1

триггер .14 и выдает

в устройство управлеп;1я Еычислительной машины сигнаЛ) разрешающий обращение к заломинающел у устройству

Если при одном из повтор1Ш1х обращений к I -ой ячейке сигнал о максимальном использовании мощности корректирующего кода повторяется; значит, данный отказ вызван увеличением числа отказавших элементов памяти Соответствующий сигнал поступает через дог.олнптельный элемент И 16 на вход установки в 1 триггера 15. По единичному состоянию триггера 15 блок упрааления 12 выдает сигнал установки в О счетчика 13, триггеров 14 и 15, а таклсе сигнал 1. на один из регистров мощности корректирующего кода 9, Информация данной страницы перекодируется более мощным корректирующим кодом

Во втором случае блок декодировапия 6 при обращении к i ой ячейке исправил число ошибок меньше (гп +1). При этом повторное обраш.екие к I -ой ячейке пе пролзводится. Обращение к запоминающему устройству идет обычным способом.

Таким образом, в предлагаемом запоминающем устройстве устраняется ачпяние случайных сбоев на величину мощности корректирующего кода Это достигается путем анализа причин, вызвавших кгаксимальную кратность ощибки. При появлении ошибки максимальной кратности производится несколько повторных обращений к выбранной ячейке

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1975 |

|

SU560255A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU477463A1 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Логическое запоминающее устройство | 1981 |

|

SU972589A1 |

| Динамическое запоминающее устройство | 1982 |

|

SU1065886A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

Авторы

Даты

1976-09-25—Публикация

1975-04-10—Подача