1

Известно запоминаюш,ее устройство с блокировкой неисправных ячеек, содержащее внешний накопитель, постоянный накопитель, входы которого подключены к дешифратору адреса, а выходы - к первым входам регистра, вторые входы которого соединены с выходами первого дополнительного накопителя, а выходы - с блоком обнаружения ошибки, регистр адреса, подсоединенный к дешифратору адреса, блоку сравнения, и второй дополнительный накопитель.

Недостатком известного запоминающего устройства является то, что оно не способно автоматически восстанавливать свою работоспособность при случайных сбоях и отказах элементов памяти, возникающих в ходе работы устройства.

Описываемое устройство отличается от известного тем, что оно содержит преобразователь кода адреса, входы которого подключены к выходу регистра адреса, выходы - ко входам внешнего накопителя, выходы которого соединены с третьими входами регистра и входами первого дополнительного накопителя, входы второго дополнительного накопителя соединены с одними из выходов регистра адреса.

Указанные отличия позволяют повысить надежность работы устройства.

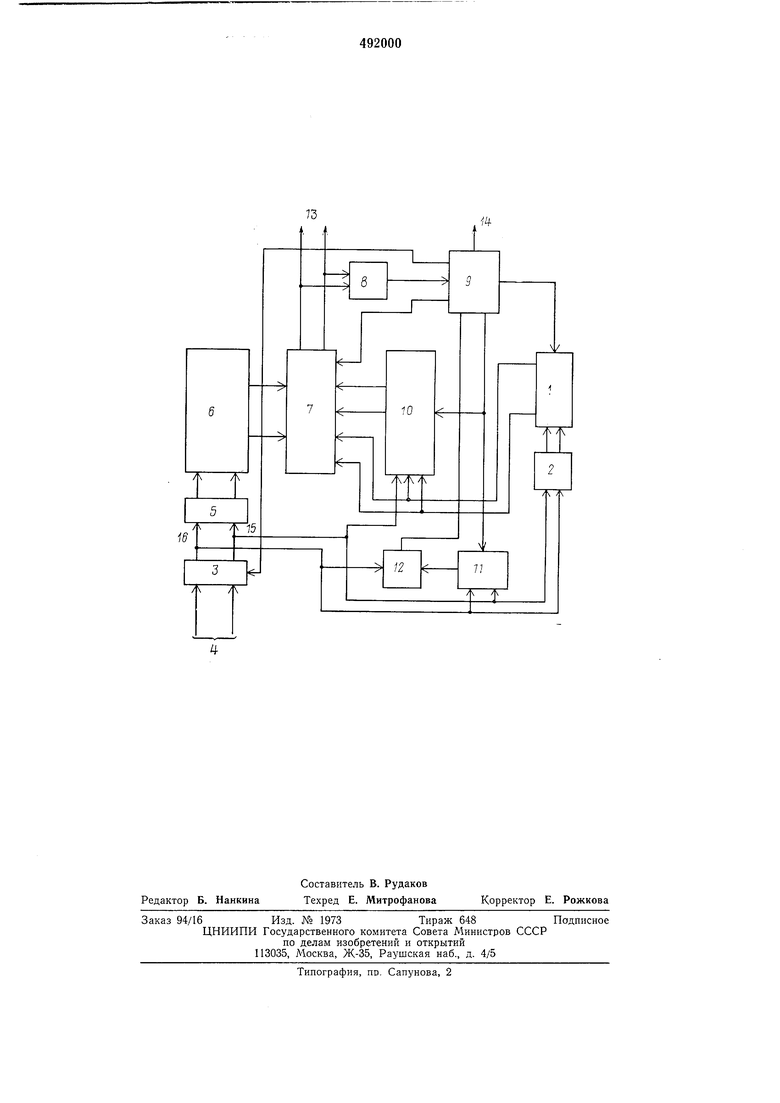

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит внешний накопитель 1, преобразователь 2 кода адреса, регистр 3

адреса со входами 4, дешифратор 5 адреса, постоянный накопитель 6, регистр 7, блок 8 обнаружения ошибки, блок 9 управления, первый дополнительный накопитель 10, второй дополнительный накопитель 11, служащий

для хранения кода неисправного адреса, блок 12 сравнения.

Выходы дешифратора 5 соединены со входами накопителя 6, выходы которого подключены к первым входам регистра 7. Выходы регистра 7 соединены с внешними информационными шинами 13 и входами блока 8, выход которого нодключен к входу блока 9 управления. Выходы накопителя 10 подключены ко вторым входам регистра 7. Выходы накопителя 11 соединены с входами блока 12, выход которого соединен с входом блока 9; выход блока 9 подключен к входу накопителя 1, выходы которого подключены к третьим входам регистра 7 и информационным входам накопителя 10. Выходы преобразователя 2 соединены с адресными входами накопителя 1. Выходы блока 9 управления подключены к входам регистров 3, 7 и накопителей 10, 11 а также к внешней шине 14. Выходы 15 первой

группы разрядов регистра 3, определяющей

группу слов накопителя 6, соединены с входами преобразователя 2, дешифратора 5 и адресными входами накопителей 10 и И. Выходы 16 второй группы разрядов регистра 3, определяюпдей слово в группе слов, соединены с входами преобразователя 2, дешифратора 5, блока 12 и ипформациоппыми входами накопителя 11.

Работа устройства происходит следующим образом.

Согласно поступившему на регистр 3 коду адреса дешифратор 5 выбирает из накопителя 6 соответствуюш,ую группу слов и определенное слово в ней, которое по команде от блока 9 поступает на регистр 7. Одновременно с этим, согласно коду первой группы разрядов кода адреса, в накопителях 10 и И выбираются по одному слову, которые соответствуют выбранной в накопителе 6 группе слов.

Если при считывании блок 8 обнаружения ошибки не выдал сигнала ошибки, то считана правильная информация, и она поступает на внешние шины 13.

Если же блок 8 выдает сигнал ошибки в блок 9 управления, то последний задает режим повторного считывания из накопителя 6. Если теперь блок 8 не обнаруживает ошибки, то считывается, что при первом считывании был сбой, и информация выдается на внешние шины 13.

Однако, если при повторном считывании блок 8 снова выдает сигнал ошибки, то блок 9 управления осуществляет следующую программу: посылает сигнал обращения к накопителю 1, по которому, согласно коду адреса на регистре 3, прошедшему через преобразователь 2 кода, накопитель 1 выдает исправную информацию для отказавшей в основном накопителе 6 ячейки. Эта информация поступает на пегистр 3 и но сигналу от блока 9 записывается в соответствующую ячейку накопителя 10. Одновремеино с этим в накопитель 11 заносится код второй группы разрядов 16 регистра адреса 7.

Так происходит автоматическое занесение кодов неисправных адресов в накопитель 11 и соответствующей им исправной информации в накопитель 10.

Если теперь обращение к накопителю 6 произойдет по неисправному адресу, то блок

12сравнения выдает сигнал об этом в блок 9, который блокирует прием информации из основного накопителя 6 и разрешает - из накопителя 10.

При выдаче информации на внешние шины

13блок 9 посылает на шину 14 сигнал конца обращения.

Формула изобретения

Запоминающее устройство с блокировкой неисправных ячеек, содержащее внешний наконнтель, постоянный наконитель, входы которого подключены к дешифратору адреса, а

выходы - к первым входам регистра, вторые входы которого соединены с выходами первого дополнительного накопителя, а выходы - с блоком обнаружения ошибки, регистр адреса, подсоединенный к дешифратору адреса,

блоку сравнения, и второй дополнительный накопитель, отличающееся тем, что, с целью повышения надежности работы устройства, оно содержит преобразователь кода адреса, входы которого подключены к выходу

регистра адреса, выходы - ко входам внешнего наконителя, выходы которого соединены с третьими входами регистра и входами первого дополнительного наконителя, входы второго донолнительного накопителя соединены

с одними из выходов регистра адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

| Оперативное запоминающее устройство с самоконтролем | 1974 |

|

SU516101A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| ЗАПОМИНАНМЦЕЕ УСТРОЙСТВО С БЛОШРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ | 1979 |

|

SU826425A1 |

| Запоминающее устройство с блокировкой неисправных запоминающих ячеек | 1974 |

|

SU507900A1 |

| Постоянное запоминающее устройство | 1972 |

|

SU527742A1 |

| Запоминающее устройство | 1978 |

|

SU809394A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Оперативное запоминающее устройство с защитной информации | 1976 |

|

SU590833A1 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU600618A1 |

Авторы

Даты

1975-11-15—Публикация

1974-10-21—Подача