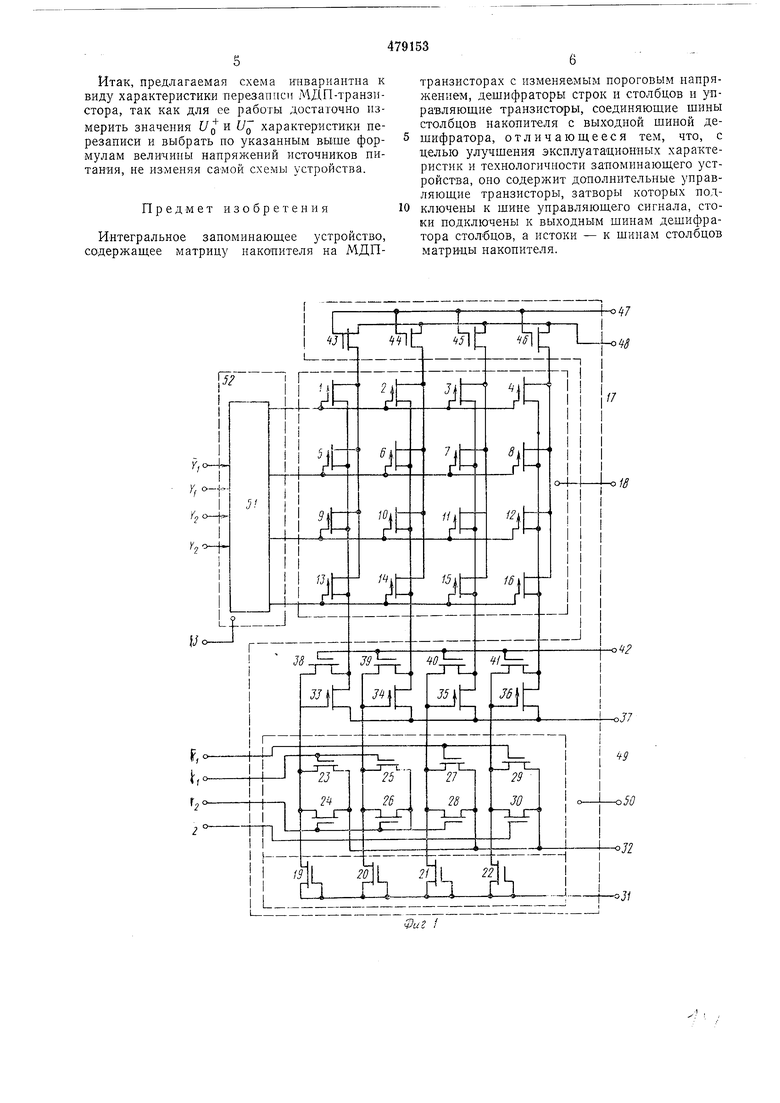

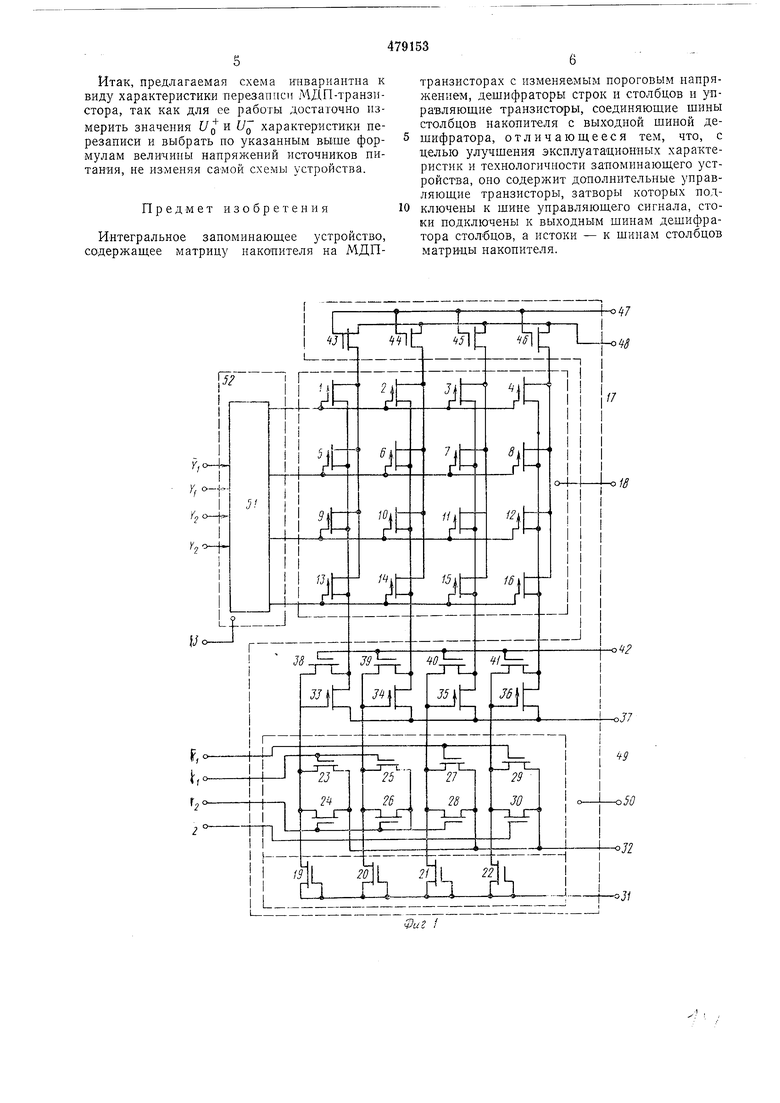

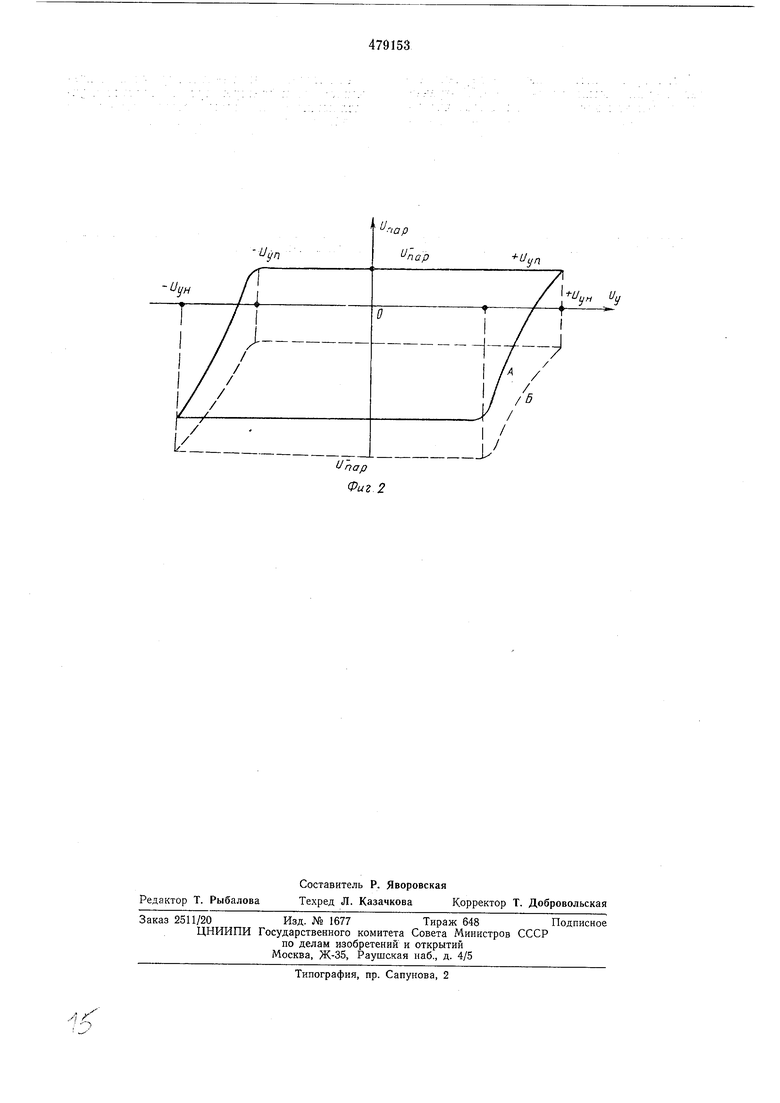

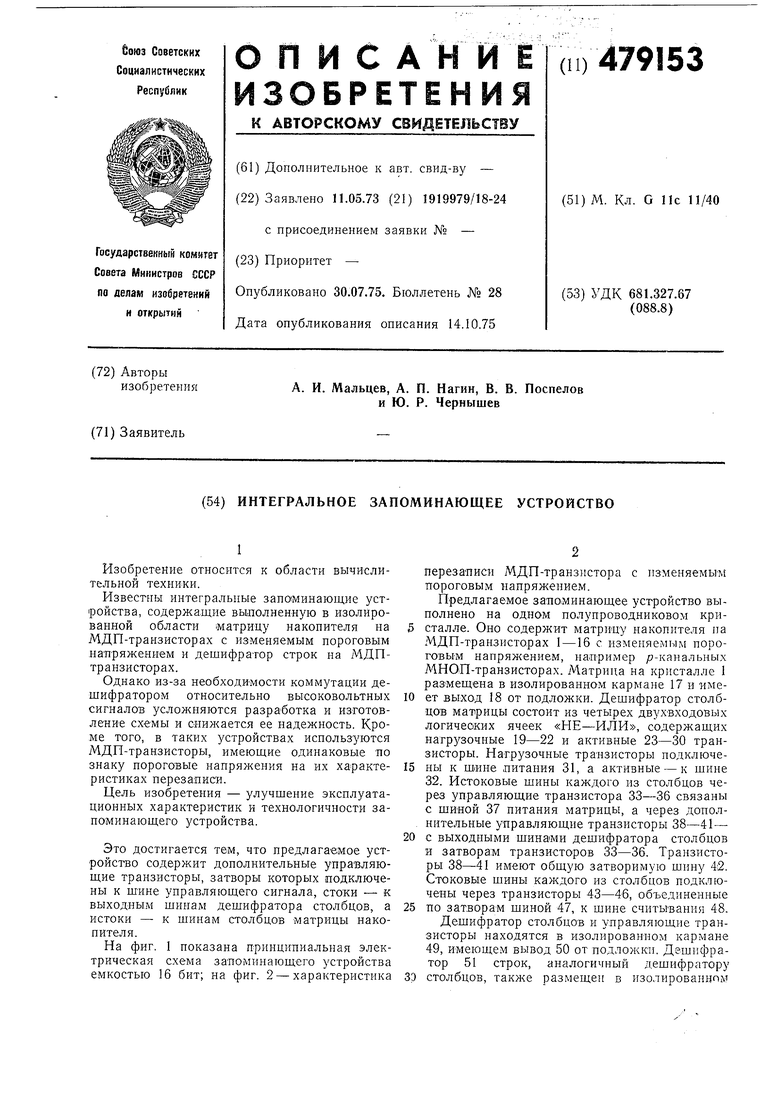

кармапе 52, имеющем вывод 53 от подложки. МДП-траизисторы дешифраторов и все управляющие транзисторы Имеют тот же тип проводимости, что и транзисторы накопителя т. е. р-:канальные Y,, УЬ УЗ, YZ и Xi, Х, Xz, Хг- адресные входы дещифраторов строк и столбцов соответственно. Устройство работает следующим образом. У МНОП-транзисторов с изменяемым пороговым напряжением характеристики перезалиси, представляющая собой зависимость величины порогового напряжения U от амплитуды напряжения на подзатворном диэлектрике при достаточно больщой его длительности (например, 10 мсек) имеет вид петли гистерезиса (фиг. 2). Значениям +t/yn и -f/yn соответствуют сохраняющиеся продолжительное время величины пороговых напряжений UQ иt/o.Величина и Q в зависимости от конструкции и технологии изготовления МНОП-транзистора может быть положительной (кривая Л) либо отрицательной (кривая Б}, но как правило,- отрицательная. Для нормальной работы необходимо, чтобы (+t/yn) () Y (+ t/ун) - Y (-t/y,,), что Oi6bi4HO имеет место при (7уп)30в (/у„)-50в. Стирание информации в матрице, как обычно, осуществляют подачей импзльса +t/yn на выходе 18 подложки после отключения источников питания. При этом пороговые напряжения Uo всех транзисторов матрицы становятся равными UQ,T. е. каждый транзистор матрицы переходит в логическое состояние «1. Выборочную запись, например, в транзистор 1 матрицы осуществляют следующим образом. Выводы 32, 48, 53 щин и подложки заземляют, на выходы 18 и 50 и шины 37, 47 и 31 подают положительное напряжение Va , на щину 42 - отрицательное напряжение, обеспечивающее отпирание транзисто ов 38-41. На входы Yi, YI, 2, YZ и Xi, Xz, Xz, Xi дещифраторов подают код адреса МДП-транзистора 1, так что в дешифраторе столбцов (в дешифраторе строк- аналогично) транзисторы 23 и 24 закрыты, а хотя бы один в каждой из пар транзисторов 25-26, 27-28, 29-30 открыт. Таким образом выбранный столбец матрицы, т. е. его истоковая и стоковая шины, оказываются изолированным от заземленного вывода шины 32, а истоковые щины всех остальных (невыбранных) столбцов заземлены через открытые транзисторы 25-30, 39-41. На щину пита-ния дещифратора 51 строк подают отрицательный импульс напряжения величиной около 1/2() в и длительностью 300-600 мсек. При этом на шине затворов выбранной строки появляется отрицательный импульс с амплитудой около 1/2 уп, а на шинах затворов остальных (невыбранных) строк - около О в. Во время действия этого отрицательного импу. под затворами транзисторов 1-4 образуются /7-капалы. При этом /7-каналы транзисторов 3-4 оказываются заземленными по истоковым щинам, а р-канал транзистора 1 изолирован от заземленной гпины. Поэтому во время действия импзльса к подзатворному диэлектрику транзистора 1 приложено напряжение величиной ( ун) + - (ун) - ун а к подзатворным диэлектрикам остальных тра-нзис1Х)ров матрицы - не более i/2 уп Это приводит к тому, что величина порогового напряжения транзистора 1 становится равной и, пороговые напряжения остальных транзисторов матрицы остаются прежними и равными f/o,T. е. только выбранный транзистор 1 переходит в логическое состояние «О. Выборочное считывание осуществляют следующим образом. Выводы шин 32, 42 и выводы подложек 50 и 53 заземляют. На выводы щины 37 и подложки 18 подают отрицательное напряжение - (0) + если , и заземляют их, если UQ.Q. Это обеспечивает смещение характеристики перезаписи в область отрицательных значений пороговых напряжений. На выводы шин 31 и 47 подают напряжение - 20 в, что обеспечивает отпирание транзисторов 19-22 и 43-46. На вывод шины 48 подают отрицательное напряжение -( в, вследствие чего разность потенциалов между выводами шин 37 и 48 равна - 4 в. При такой комбинации потенциалов дополнительные управляющие транзисторы 38-41 заперты. Напряжение питания дешифратора 51 строк должно составлять m(us) 1 ,, 2J Благодаря этому обеспечивается на затворной шине выбранной строки наличие отрицательного потенциала, приблизительно равного по величине среднему значению между UQ и (/. При наличии на входах дешифраторов кода адреса, например, транзистора 1, на затворной шине верхней строки потенциал равен (U)-(U$) ,2 а для остальных строк - около О в. При этом транзисторы 23 и 24 закрыты, а хотя бы один из транзисторов 25-30 открыт. Это значит, что транзистор 33 открыт, а транзисторы 34-36 закрыты, по цепи: вывод шины 37 - транзисторы 33, 1, 43 - вывод шины 48 проекает ток, если МДП-транзистор 1 находится в состоянии логической «1, и ток отсутствует, сли он находится в состоянии логического О. В цепях всех невыбранных столбцов ток е протекает, так как транзистопы 34-36 заперты.

Итак, предлагаемая схема инвариантна к виду характеристики нерезаппси МДП-транзистора, так как для ее работы достаточно измерить значения U и U характеристики нерезаписи и выбрать по указанным выше формулам величины напряжений источников питания, не изменяя самой схемы устройства.

Предмет изобретения

Интегральное запоминающее устройство, содержащее матрицу накопителя на МДПтранзисторах с изменяемым пороговым напряжением, дешифраторы строк и столбцов и управляющие транзисторы, соединяющие щины столбцов накопителя с выходной щиной дешифратора, отличающееся тем, что, с целью улучшения эксплуатационных характеристик и технологичности запоминающего устройства, оно содержит дополнительные управляющие транзисторы, затворы которых подключены к шине управляющего сигнала, стоки подключены к выходным щинам дешифратора столбцов, а истоки - к щинам столбцов матрицы накопителя.

;

/

/

/70/

пар

+U.

У

и Uy

-J

| название | год | авторы | номер документа |

|---|---|---|---|

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

| Интегральное запоминающее устройство на мдп транзисторах | 1973 |

|

SU458036A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

Авторы

Даты

1975-07-30—Публикация

1973-05-11—Подача