1

Изобретение относится к вычислительной Технике.

Известно интегральное запоминающее устройство (ЗУ) на МДП-транзисторах, содержащее матрицу накопителя, каждая ячейка которой состоит из МДП-транзистора с изменяемым пороговым напряжением, н дешифраторы строк и столбцов.

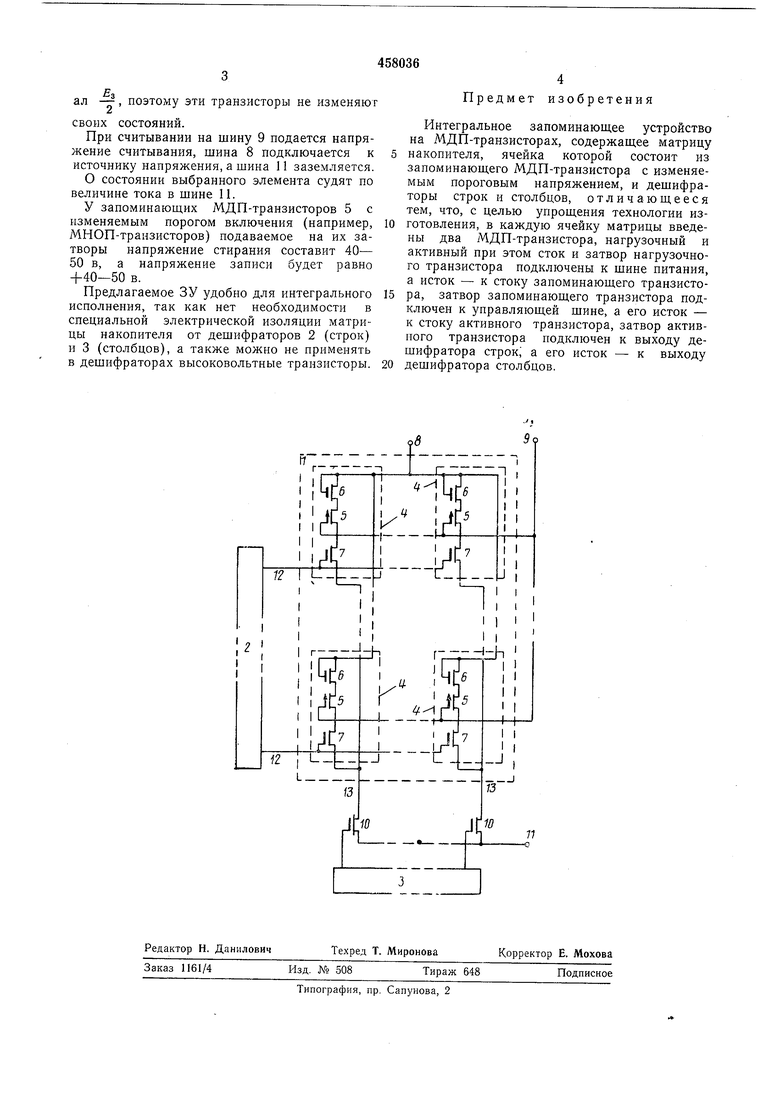

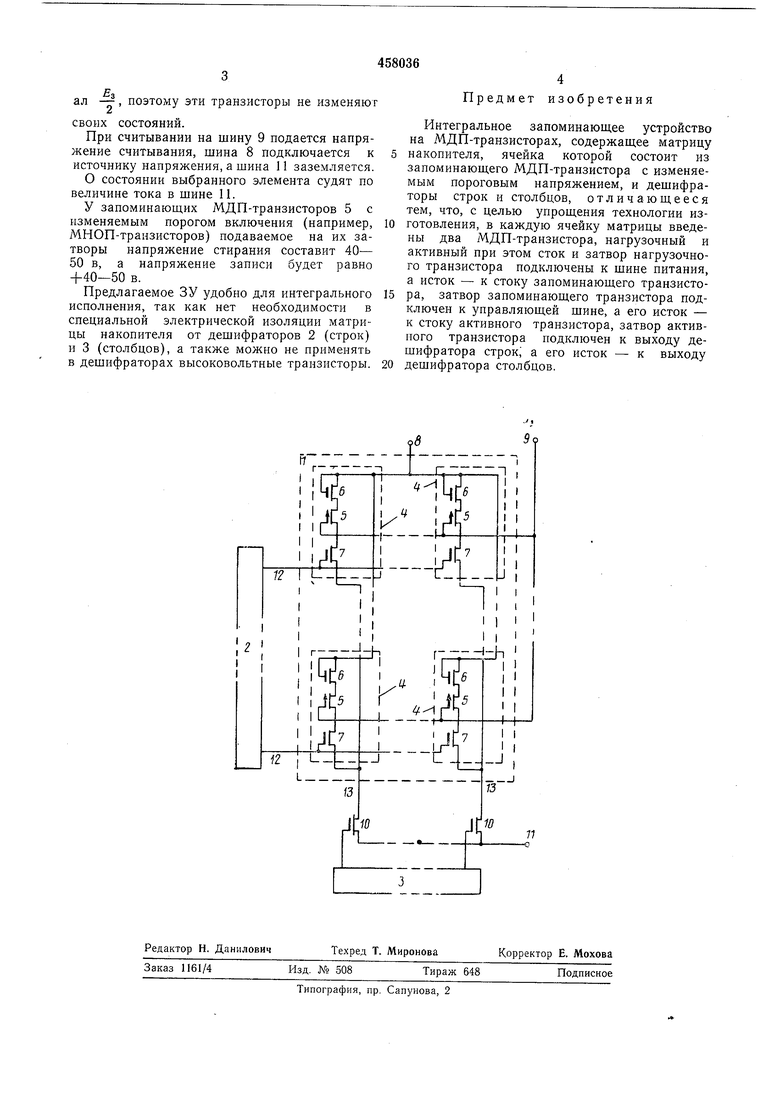

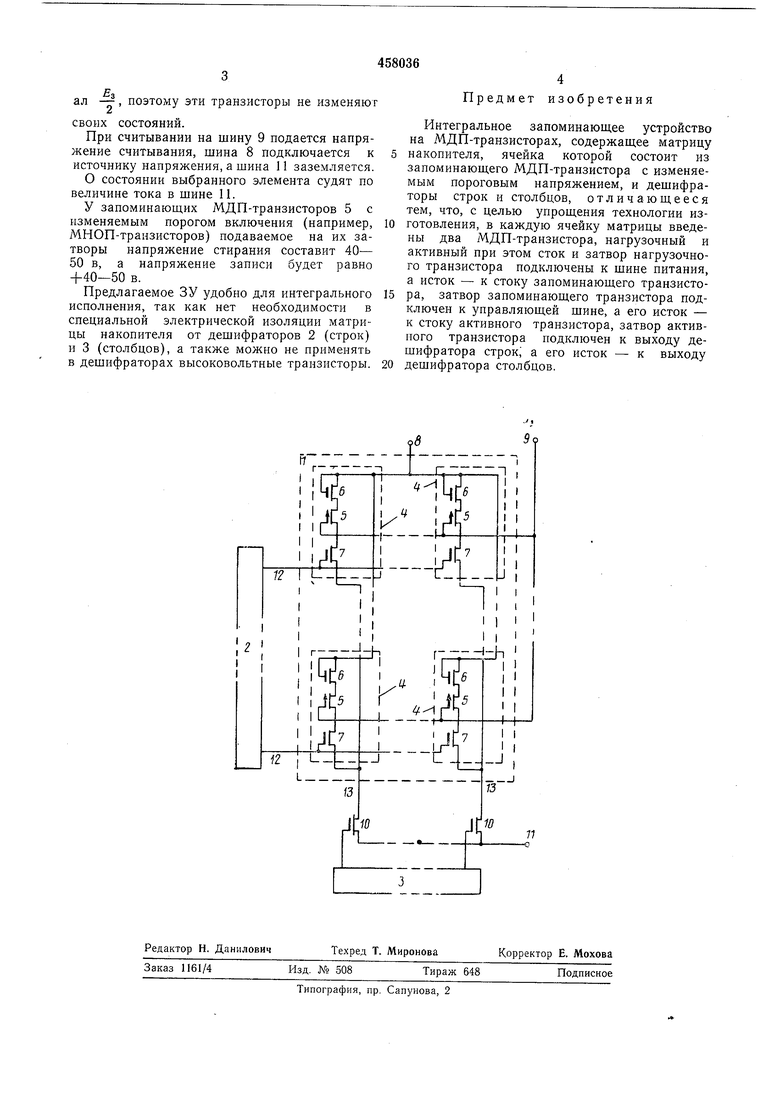

Предлагаемое ЗУ отличается тем, что в каждую ячейку матрицы введены два МДПтранзистора, нагрузочный и активный при этом сток и затвор нагрузочного транзистора подключены к шине питания, а исток - к стоку запоминающего транзистора, затвор запоминающего транзистора подключен к управляющей шине, а его исток - к стоку активного транзистора, затвор активного транзистора подключен к выходу дешифратора строк, а его исток - к выходу дешифратора столбцов.

На чертеже дана электрическая схема предлагаемого ЗУ.

Устройство состоит из матрицы накопителя 1, дешифратора строк 2, дешифратора столбцов 3, ячейки матрицы накопителя 4, запоминающего МДП-транзистора с изменяемым иороговым напряжением 5, нагрузочного МДП-транзистора 6, активного МДП-транзистора 7, шины питания 8, управляющих щин 9, МДП-транзистора 10, выходной шины ЗУ 11, выходной шины дешифратора строк 12 и выходной шины дешифратора столбцов 13.

Для записи необходимого массива информации все запоминающие МДП-транзисторы 5 с изменяемым пороговым напряжением предварительно переводят в одно состояние (стирание). Для этого на шину 9 подают напряжение стирания, а шины 8 и 11 заземляют. Затем избирательно МДП-транзисторы 5 переводят в другое состояние. Для этого на шину 9 подают напряжение записи ЕЗ, обеспечивающее отпирание запоминающего МДПтранзистора 5, а на шину 8 - напряжение,

17

равное ---j-t/o где f/o - пороговое на.t

пряжение нагрузочного МДП-транзпстора 6. Выходная шина 11 при этом заземлена.

Потенциал канала запоминающего транзистора в выбранной ячейке 4 будет близок иулю (это обеспечивается определенным соотношением сопротивлений каналов транзисторов 6, 7 н 10), поэтому состояние транзистора изменится.

У всех остальных запоминающих МДПтранзпсторов 5 каналы будут иметь потенципоэтому эти транзисторы не изменяют

ал

своих состояний.

При считывании на шину 9 подается напряжение считывания, шина 8 подключается к источнику напряжения, а шина 11 заземляется.

О состоянии выбранного элемента судят по величине тока в шине 11.

У запоминаюш,их МДП-транзисторов 5 с изменяемым порогом включения (например, МНОП-транзисторов) подаваемое на их затворы напряжение стирания составит 40- 50 в, а напряжение записи будет равно -f 40-50 в.

Предлагаемое ЗУ удобно для интегрального исполнения, так как нет необходимости в специальной электрической изоляции матрицы накопителя от дешифраторов 2 (строк) и 3 (столбцов), а также можно не применять в дешифраторах высоковольтные транзисторы.

Предмет изобретения

Интегральное запоминающее устройство на МДП-транзисторах, содержащее матрицу накопителя, ячейка которой состоит из запоминающего МДП-транзистора с изменяемым пороговым напряжением, и дешифраторы строк и столбцов, отличающееся тем, что, с целью упрощения технологии изготовления, в каждую ячейку матрицы введены два МДП-транзистора, нагрузочный и активный при этом сток и затвор нагрузочного транзистора подключены к шине питания, а исток - к стоку запоминающего транзистора, затвор запоминающего транзистора подключен к управляющей шине, а его исток - к стоку активного транзистора, затвор активного транзистора подключен к выходу дешифратора строк; а его исток - к выходу дешифратора столбцов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральное запоминающее устройство | 1974 |

|

SU523455A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Интегральное запоминающее устройство | 1973 |

|

SU479153A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

Авторы

Даты

1975-01-25—Публикация

1973-07-19—Подача