(54) СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1980 |

|

SU886251A1 |

| Синтезатор частот | 1973 |

|

SU479215A1 |

| Синтезатор частот | 1981 |

|

SU987818A1 |

| Цифровой синтезатор частоты | 1977 |

|

SU720667A1 |

| Цифровой синтезатор частот | 1981 |

|

SU1109913A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Цифровой синтезатор частот | 1991 |

|

SU1803977A1 |

| СИНТЕЗАТОР ЧАСТОТ С ПЕРЕМЕННЫМИ УСИЛЕНИЕМ И ПОЛОСОЙ ПРОПУСКАНИЯ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2003 |

|

RU2267860C2 |

| СИНТЕЗАТОР ЧАСТОТ С АСТАТИЧЕСКИМ КОЛЬЦОМ АДАПТИВНОЙ ЧАСТОТНО-ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2007 |

|

RU2329596C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

1

Изобретение относится к радиотехнигке и может использоваться в устройствах синтеза частот.

Известен синтезатор частот, содержащий последовательно соединенные опорный гене- 5 ратор, делитель частоты с постоянным коэффициентом деления, первый ключ, фазовый детектор, устройство памяти, фильтр нижних частот, управляемый генератор, делитель частоты с переменным коэффициентом деления Ю и второй ключ, выход которого подключен ко второму входу фазового детектора, а также различитель знака частотной ошибки, первый и второй входы которого соединены соответ ственно с выходами делителей частоты с пе-15 ременным и постоянным коэффициентом деления, первый и второй выходы различителя знака частотной ошибки подключены к соответствующим входам устройства управления, первый и второй выходы устройства управле-20 НИН соединены соответственно со вторым входом второго ключа и со вторым входом перового ключа, при этом первый инверсный выход устройства управления соединен со вторым входом устройства памяти ij .25

Однако известный синтезатор частот имеет недостаточное быстродействие.

Наиболее близким техническим решением является синтезатор частот, содержащий последовательно соединенные опорный генератор и делитель частот с постоянным коэффициентом деления, первый ключ, фазовый детектор, устройство памяти, фильтр нижних частот, управляемый генератор, делитель частоты с переменным коэффициентом деления и второй ключ, выход которого подключен к второму входу фазового детектора, а также различитель знака частотной ошибки, первый и второй входы которого соединены соответственно с выходами делителей частоты с переменным и постоянным коэффициентом деления, первый и второй выходы различителя знака частотной ошибки подключены к соответствующим входам устройства управления, первый и второй входы устройства управления соединены соответственно с вторым входом второго ключа и с вторым входом первого ключа, при этом первый инверсный выход устройства управления соединен со вторым входом устройства памяти и с первым

входом первого элемента совпадения импупьсов сброса, вь}ход которого подсоединен к установочному входу делителя частоты с пе ременным коэффициентом деления, а второй инверсный выход устройства управления подключен к первому входу второго элемента совпадения импульсов сброса ,

Однако известный синтезатор частот также имеет недостаточное быстродействие.

Цель изобретения - повышение быстродей ствия.

Поставленная цель достигается тем, что в синтезаторе частот, содержащем последовательно соединенные опорный генератор, делитель частоты с постоянным коэффициен- том деления, первый ключ, фазовый детектор устройство памяти, фильтр нижних частот, управляемый генератор, делитель частоты с переменным коэффициентом деления и второй ключ, выход которого подключен к ВТОрому входу фазового детектора, а также различитель знака частотной ошибки, первый и второй входы которого соединены соответственно с выходами делителей частоты с переменным и постоянным коэффициентом де- ления, первый и второй выходы различителя знака частотной ошибки подключены к соответствующим входам устройства управления, первый и второй выходы устройства управления соединены соответственно с вторым входом второго ключа и со вторым входом первого ключа, при этом первь{й инверсный выход устройства управления соединен со вторым входом устройства памяти и с первым входом первого элемента совпадения импульсов сброса, выход которого подсоединен к установочному входу делителя частоты с переменным коэффициентом деления, а второй инверсный выход устройства управления подключен к первому входу второго элемента совпадения импульсов сброса, выходы делителя частоты с переменным коэффициентом деления и делителя частоты с постоянным коэффициентом деления дополнительно соединены со вторыми входами соот- ветственно второго и первого элементов совпадения импульсов сброса, а выход второго элемента совпадения имиульсов сброса соединен с установочным входом делителя частоты с постоянным коэффициентом деления.

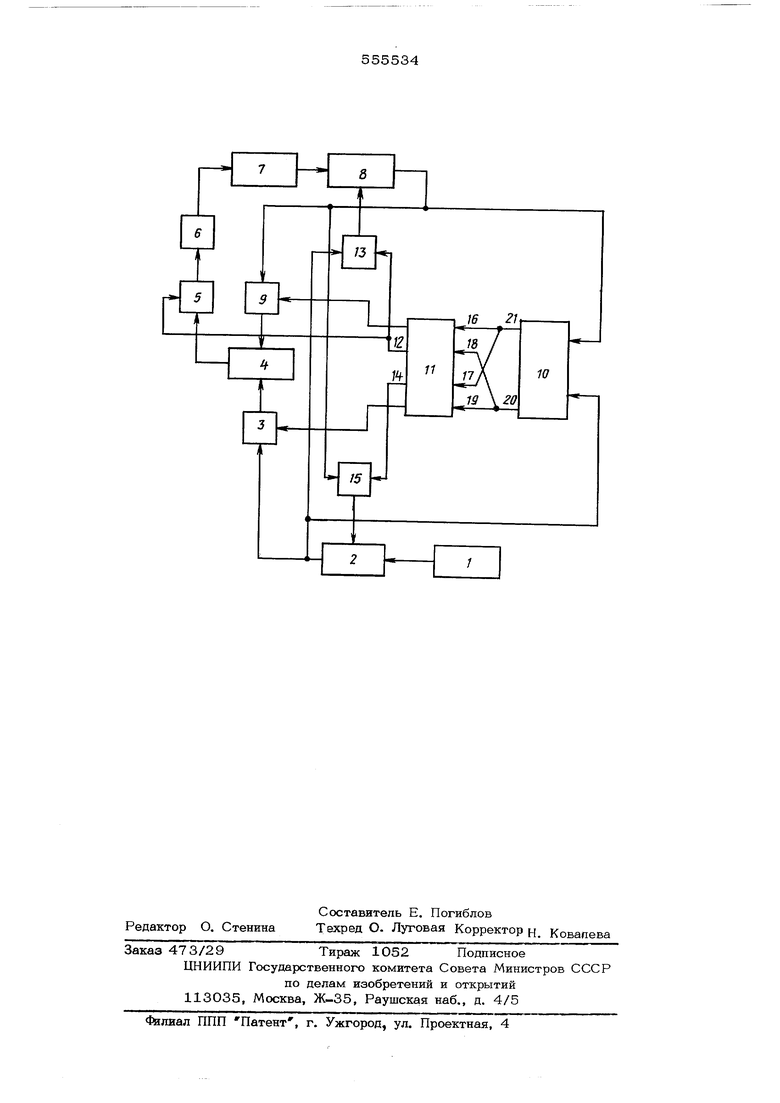

На чертеже изобршжена структурная электрическая схема предлагаемого синтезатора частот.

Синтезатор частот содержит последовательно соединенные опорный генератор 1, делитель частоты 2 с постоянным коэффициентом деления, первый ключ 3, фазовый детектор 4, устройство памяти 5, фипьтр чижних чястот ШЧ/6, управляемый гене-

ратор 7, делитель частоты 8 с переменным коэффициентом деления и второй ключ 9, выход которого подключен к второму входу фазового детектора 4, а также различитель 10 знака частотной ошибки, первый и второй входы которого соединены соответственно с выходами делителей частоты 2 и 8, первый и второй выходы различителя 10 знака подключены к соответствующим входам устройства управления 11, первый и второй выходы которого соединены соответственно с вторым входом первого ключа 3 и с вторым входом второго ключа 9. При этом первый инверсный выход 12 устройства управления 11 соединен с вторым входом устройства памяти 5 и с первым входом первого элемента совпадения 13 импульсов сброса, выход которого подсоединен к установочному входу делителя частоты 8, а второй инверсный выход 14 устройства управления 11 подключен к первому входу второго элемента совпадения 15 импульсов сброса, выходы делителей частоты 2 и 8 дополнительно соединены с вторыми входами соответственно второго 15 и первого 13 эл&ментов совпадения импульсов сброса, а выход второго элемента совпадения 15 соед&нен с установочным входом делителя частоты 2.

Синтезатор частот работает следующим образом.

Пусть, например, на первом и втором выходах устройства управления 11 действуют напряжения, следовательно, первый и второй ключи 3 и 9 включены, устройство памяти 5 разблокировано, а частота управляемого генератора 7, поделенная делителем частоты 8 с переменным коэффициентом деления, больше частоты опорного генератора 1, поделенной делителем частоты 2 с постоянным коэффициентом деления. При этом начальная расстройка больше полосы захвата, но меньше полосы удержания. В этом случае создаются такие ситуации, когда в промежутке времени между двумя импульсами с выхода делителя частоты 2 действуют два импульса с выхода делителя частоты 8, второй из этих импульсов приводит к срабатыванию различителя знака 10 и на его первом выходе появляется импульс, который действует на входы 16 и 17 устройства управления 11. В результате на первом выходе и первом инверсном выходе 12 устройства управления 11 устанавливается соответственно нулевое и некоторое конечное напряжение. При нулевом напряжении на первом выходе размыкается ключ 9, а появление напряжения на первом инверсном выходе 12 приводит к блокированию устройства памяти 5 и отпиранию первого элемента совпа-

дения 13 импульсов сброса по первому его входу. В результате напряжение на выходе устройства памяти 5 устанавливается равным нулю и напряжение на выходе фильтра нижних частот 6 быстро уменьшается, умень шая частоту управляемого генератора 7. Одновременно выходные импульсы делителя частоты 2 проходят через первый элемент совпадения 13 на установочный вход делителя частоты, вызывая сброс в исходное сое- тояние всех его ячеек счета. Таким образом на всем этапе быстрого уменьшения частоты управляемого генератора 7 происходит синхронизация работы делителя частоты 8 с переменным коэффициентом деления сигналом делителя частоты 2 с постоянным коэффициентом деления. При этом, поскольку цикл работы обоих делителей частоты начинается одновременно, разность фаз между их выходными импульсами становится пропорционапьной уменьшающейся разности час тот следования этих импульсов, В результате этого сразу после изменения знака частотной ошибки начальное рассогласование по фазе становится благоприятным для захвата желаемой частоты.

После того как частота управляемого генератора 7 становится даже незначитель- но меньше желаемого значения, импульсы на выходе делителя частоты 8 не появл5 ются, поскольку сброс ячеек счета этого делителя частоты продолжается, а период заполнения его ячеек счета больше периода следования импульсов с выхода делителя частоты 2 с постоянным коэффициентом деления. Поэтому на вход различителя 10 знака частотной ошибки поступают только импульсы делителя частоты 2 и на его втором выходе появляется импульс, который действует на первый вход включения 18 и второй вход выключения 19 устройства управления 11. При нулевом напряжении на первом выходе вход 19 заблокирован и разблокировка его происходит с запаздыванием на время, превышающее период повторения импульсов на выходе делителя частоты 2 с постоянным коэффициентом деления относи тельно момента времени установления некоторого конечного напряжения на первом выходе. Учитывая это, устройство управления 11 срабатывает только по первому входу включения 18 и напряжение появляется на его первом выходе, а на первом инверсном выходе 12 оно становится равным нулю. В результате второй ключ 9 включается, а первый, элемент совпадения закрывается, и, следовательно, восстанавливается поток импульсов выборок на втором входе фаэрвого детектора 4 и прекращается сброс 60

ячеек счета делителя частоты 8 с перемен- ным коэффициентом деления по установочному входу. При этом выборки осушествляют ся в начальном этапе формирования пилообразного напряжения фазового детектора 4, поскольку включению второго ключа 9 предшествовал сброс ячеек счета делителя частоты 8 и частота следования импульсов этого делителя частоты в рассматриваемый момен времени меньше частоты следования импульсов с выхода делителя частоты 2, Вследствие этого на выходе устройства памяти 5 устанавливается минимальное напряжение, а для компенсации большого превышения частоты управляемого генератора 7 над желаемой частотой необходимо малое управляюшее напряжениво Кроме того, при замыкании второго ключа 9 разность частот сигналов на входах фазового детектора 4 минимальна. Таким образом, к моменту времени замыкания контура регулирования быстро создаются благоприятные для захвата начальные условия.

Для поддержания этих начальных условий введено запаздывание в разбпокирование входов включения 16 и 19 устройства управления 11. Необходимость введения запаздывания обусловлена тем, что после изменения знака частотной ошибки на выходе различи- теля знака 10 появляется первый импульс и одновременно осуществляется сброс ячеек счета делителя частоты 8, а поскольку частота следования импульсов на выходе- делителя частоты 2 больше частоты следования импульсов на выходе делителя частоты 8, на выходе 20 различителя знака 10 появляется второй импульс, действие которого при отсутствии запаздывания в разблокировании входов 16 и 19 приводило бы к установке нулевого напрянгения на втором выходе устройства зтгравления 11 и, следовательно, к размыканию первого ключа 3, через который на вход фазового детектора 4 подается опорный сигнал.

Поскольку в предлагаемом синтезаторе частот создаются и поддерживаются благоприятные начальные условия, после включения второго ключа 9 наступает режим синхронизма.

В случае, если частота управляемого генератора 7 меньше желаемого значения, синтезатор частот работает аналогично, но импульс появляется на выходе 20 различи- теля знака 10, нулевое и некоторое конечное напряжение устанавливаются соответственно на втором и втором инверсном выходе 14 устройства управления 11,

При этом первый ключ 3 размыкается, генератор пилообразного напряжения фазового детектора 4 не запускается и выборки

производятся из максимального напряжения. В результате напряжение на выходе устройства памяти 5 устанавливается максимальным, напряжение на выходе фильтра нижних частот б быстро увеличивается и, следовательно, частота управляемого генератора 7 также быстро увеличивается. Одновременно импульсами с выхода делителя частоты 8 через второй элемент совпадения 15 проиэ- водится синхронизация работы делителя час- ю

тоты 2. Когда знак частотной ошибки изменяется на противоположный, появляется импульс на выходе 21 различителя знака 10, по второму входу включения 17 срабатывает устройство управления 11, на его выходе появляется напряжение, включается ключ 3 и начинается запуск генератора пилообразного напряжения фазового детектора 4. Поскольку осуществлялась синхронизация работы делителя частоты и часто та следования импульсов на выходе делителя частоты 8 стала несколько больше частоты следования импульсов с выхода делителя частоты 2, выборки осуществляются из конечного этапа формирования фазового детектора 4 и, следовательно, выходное напряжение устройства памяти 5 близко к максимальному, что и необходимо для увеличения частоты управляемого генератора 7 до желаемого значения.

Данный синтезатор частот к моменту времени включения устройством управления 11 первого или второго ключей 3 или 9 обеспечивает при любых расстройках перерегулирование приблизительно 5%. В резуль тате уменьшается время перестройки частоты на этапах быстрого изменения знака частотной ошибки и установления желаемой

частоты,

Формула изобретения

Синтезатор частот, содержащий ,последовательно соединенные опорный генератор,

делитель частоты с постоянным коэффициентом деления, первый ключ, фазовый детектор, устройство памяти, фильтр нижних частот, управляемый генератор, делитель частоты с переменным коэффициентом деления и второй ключ, выход которого подключен ко второму входу фазового детектора, а также различитель знака частотной ошибки, первый и второй входы которого

лителей частоты с переменным и постоянным коэффициентом деления, первый и второй выходы различителя знака частотной ошибки подключены к соответствующим входам yciw ройства управления, первый и второй выходы устройства управления соединены соответ ственно со вторым входом второго ключа и со вторым входом первого ключа, при этом первый инверсный выход устройства управления соединен со вторым входом устройства памяти и с первым входом первого элемента совпадения импульсов сброса, выход которого подсоединен к установочному входу делителя частоты с переменным коэффициентом деления, а второй инверсный выход устройства управления подключен к первому входу второго элемента совпадения импульсов сброса, отличающийся тем, что с целью повышения быстродействия, выходы делителя частоты с переменным коэ4нфициентом деления и делителя частоты с постоянным коэффициентом деления дополнительно соединены со вторыми входами соответственно второго и первого элементов совпадения импульсов сброса, а выход второго элемента совпадения импульсов сброса соединен с установочным входом делителя частоты с постоянным коэффициентом деления.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1977-04-25—Публикация

1974-02-01—Подача