1

Изобретение относится к области вычислительной техники.

Известны устройства для сложения чисел в системе остаточных классов, содержащие четыре десятичных матрицы сложения, блок элементов «И, блоки элементов «ИЛИ, выходы которых соединены с соответствующими входами первой и второй десятичных матриц сложения, блок управления, входы которого соединены соответственно с выходами первой и Второй десятичных матриц сложения, входы первого слагаемого третьей и четвертой десятичных матриц сложения соединены соответственно с выходами первой и второй десятичных матриц сложения, входы блоков элементов «ИЛИ подключены к информационным входам устройства, выход блока элементов «И соединен с выходом устройства.

Известные устройства содержат также комбинационные схемы, которые их усложняют.

В предложенном устройстве выход блока управления соединен со входами второго слагаемого третьей и четвертой десятичных матриц сложения, выходы суммы которых подключены соответственно к первому и второму входам блока элементов «И. Это позволяет исключить из известного устройства комбинационные схемы, соединенные с выходами третьей и четвертой матрицы сложения.

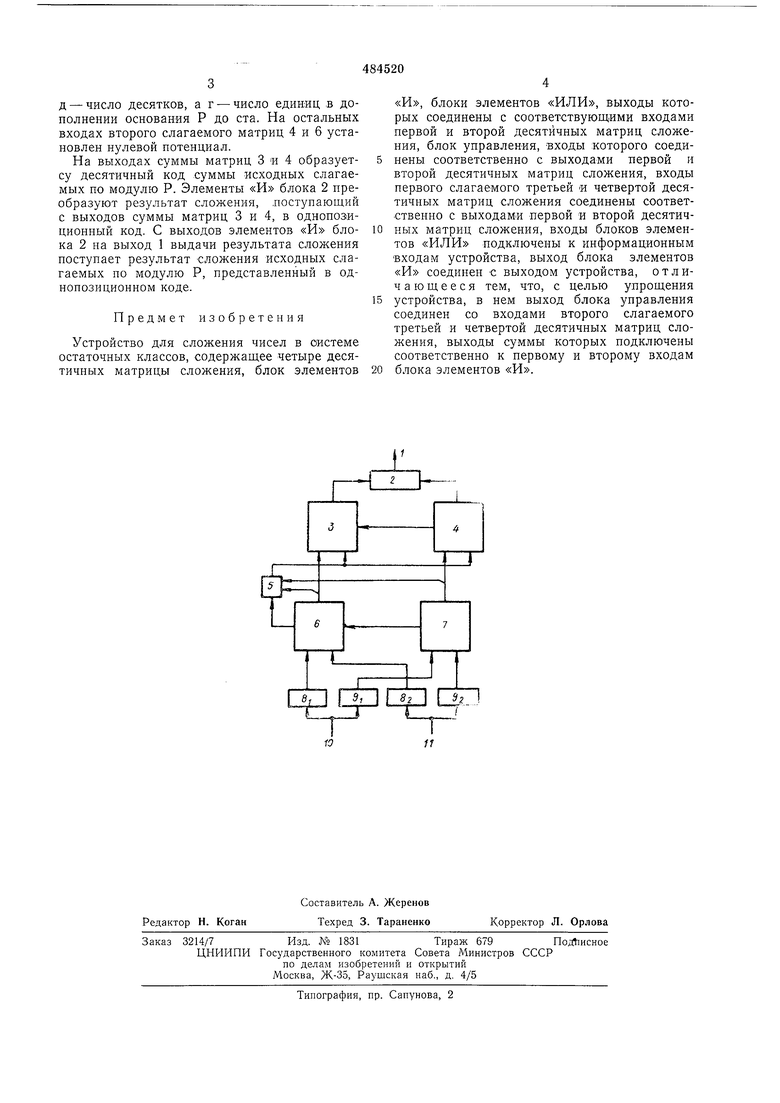

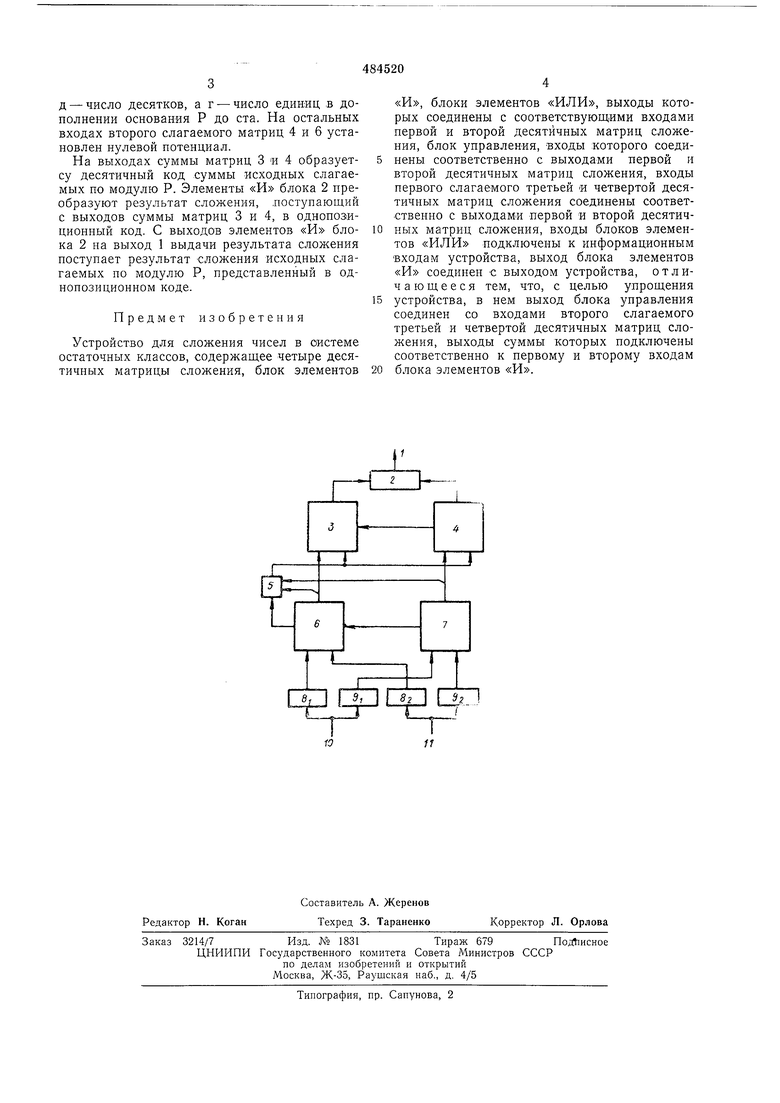

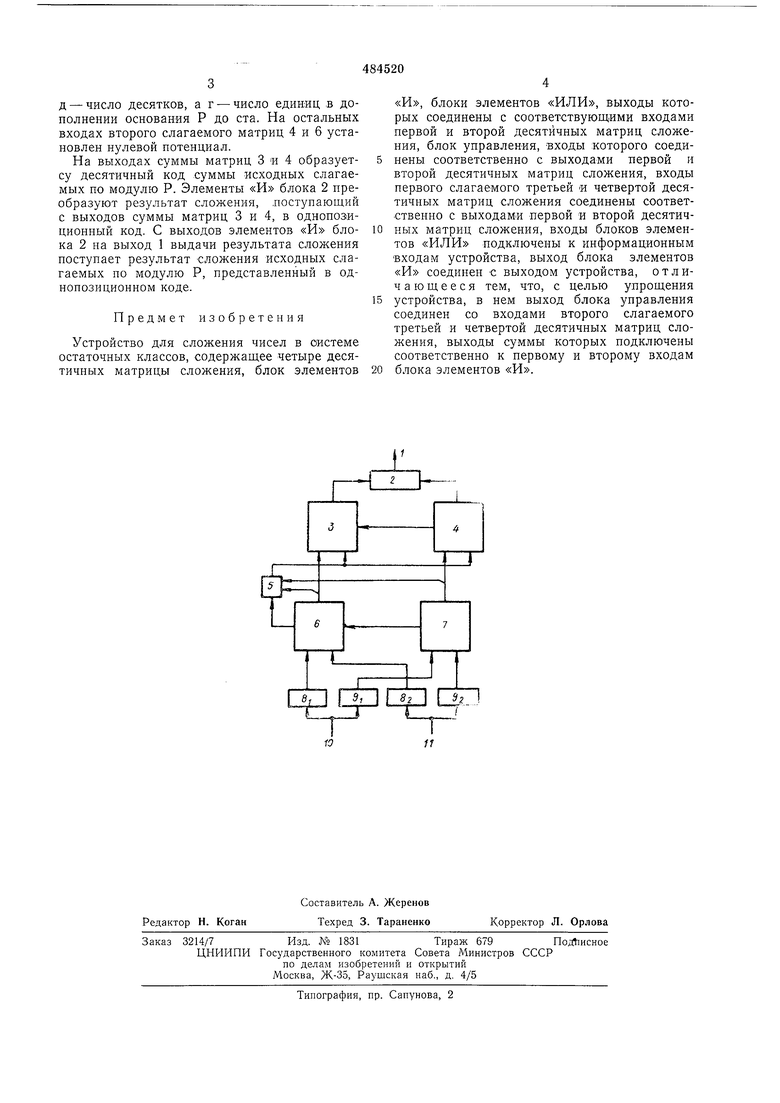

Схема устройства представлена на чертеже.

В схеме входят; выход 1 устройства, блок 2 элементов «И, десятичные матрицы сложения 3, 4, блок 5 управления, десятичные матрицы сложения 6, 7, блоки элементов «ИЛИ

8i, 82, 9i, 92, информационные входы 10, И устройства.

Устройство работает следующим образом. На входы 10 и И подаются складываемые числа, представленные в однопозиционном коде. На выходах элементов «ИЛИ блока 8 и 9 образуются соответственно однопозиционные коды числа десятков и единиц в соответствующих слагаемых.

С помощью десятичных матриц сложения 6

и 7 производится суммирование складываемых чисел, преобразованных группами элементов «ИЛИ 8 и 9. С выходов суммы матриц 6 и 7 результат сложения поступает на входы первого слагаемого десятичных матриц

3 и 4 и на блок 5 управления. Последний анализирует результат сложения, образовавшийся на выходах суммы матриц 6 и 7: если этот результат меньше величины основания Р, то управляющий сигнал на выходе блока 5 принимает нулевое значение; в противном случае управляющий сигнал принимает единичное значение.

Выход блока 5 управления соединен с д-ым входом второго слагаемого матрицы 3 и г-ым

входом второго слагаемого матрицы 4, где

д - число десятков, а г - число единиц в дополнении основания Р до ста. На остальных входах второго слагаемого матриц 4 и 6 установлен нулевой потенциал.

На выходах суммы матриц 3 и 4 образуетсу десятичный код суммы исходных слагаемых по модулю Р. Элементы «И блока 2 преобразуют результат сложения, .поступающий с выходов суммы матриц 3 и 4, в однопозиционный код. С выходов элементов «И блока 2 на выход 1 выдачи результата сложения поступает результат сложения исходных слагаемых по модулю Р, представленный в однопозиционном коде.

Предмет изобретения

Устройство для сложения чисел в системе остаточных классов, содержащее четыре десятичных матрицы сложения, блок элементов

«И, блоки элементов «ИЛИ, выходы которых соединены с соответствующими входами первой и второй десятичных матриц сложения, блок управления, входы которого соединены соответственно с выходами первой и второй десятичных матриц сложения, входы первого слагаемого третьей и четвертой десятичных матриц сложения соединены соответственно с выходами первой и второй десятичных матриц сложения, входы блоков элементов «ИЛИ подключены к информационным входам устройства, выход блока элементов «И соединен с выходом устройства, отличающееся тем, что, с целью упрощения

устройства, в нем выход блока управления соединен со входами второго слагаемого третьей и четвертой десятичных матриц сложения, выходы суммы которых подключены соответственно к первому и второму входам

блока элементов «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения чисел в системе остаточных классов | 1972 |

|

SU454550A1 |

| Преобразователь двоичного кода в десятичный | 1979 |

|

SU868747A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для сложения - вычитания | 1985 |

|

SU1273918A1 |

| Устройство для сложения и вычитания чисел в фазо-импульсной форме | 1976 |

|

SU595732A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

Авторы

Даты

1975-09-15—Публикация

1973-09-03—Подача