Изобретение может быть использовано в вычислительной технике при построении цифровых вычислительнык машин, реализующих операции в двоичной и в десятичной арифметике.

Цель изобретения - упрощение устройства.

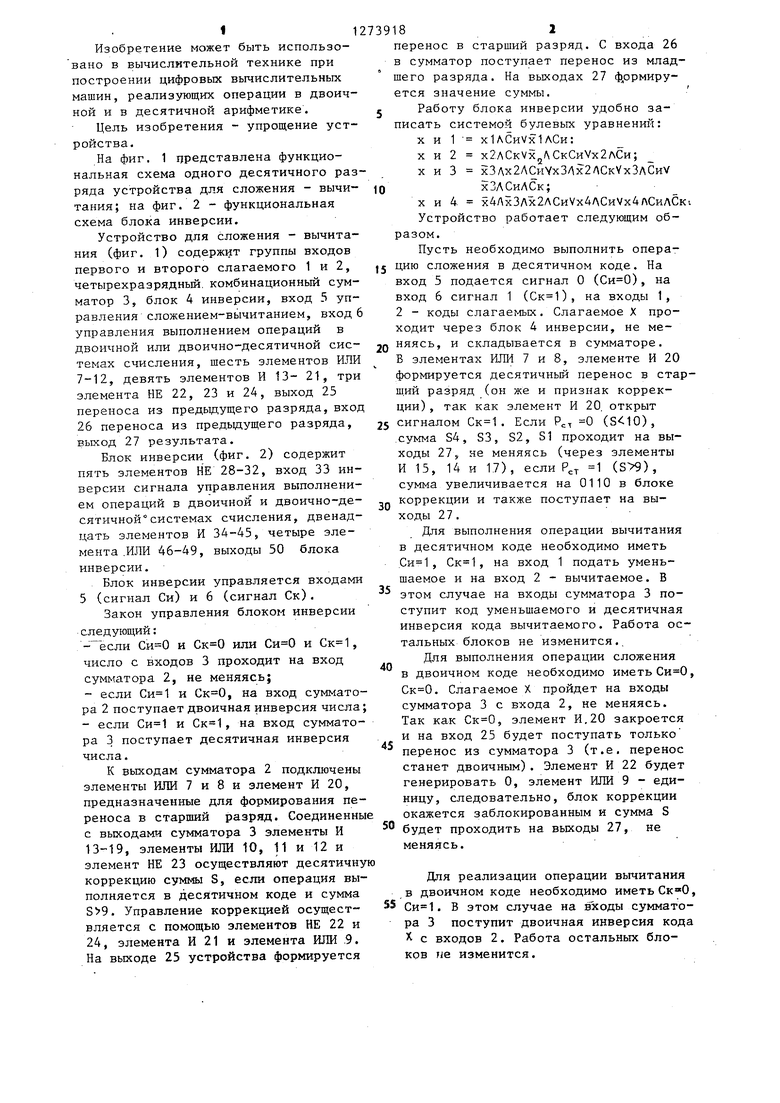

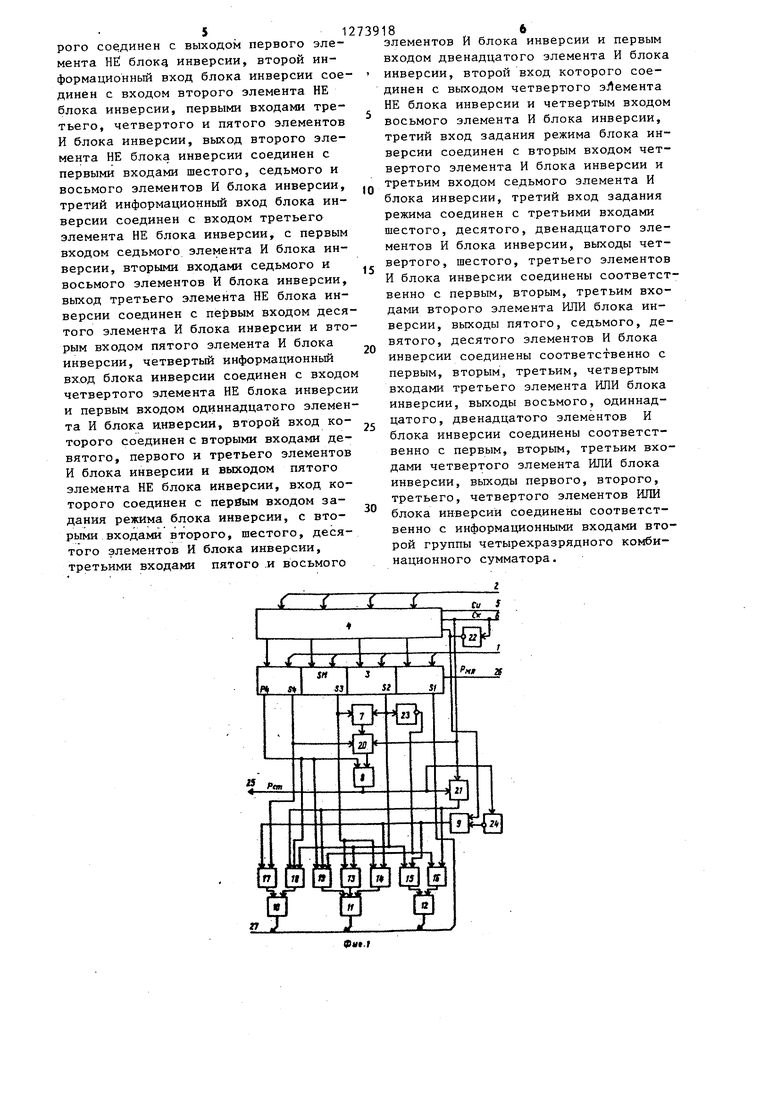

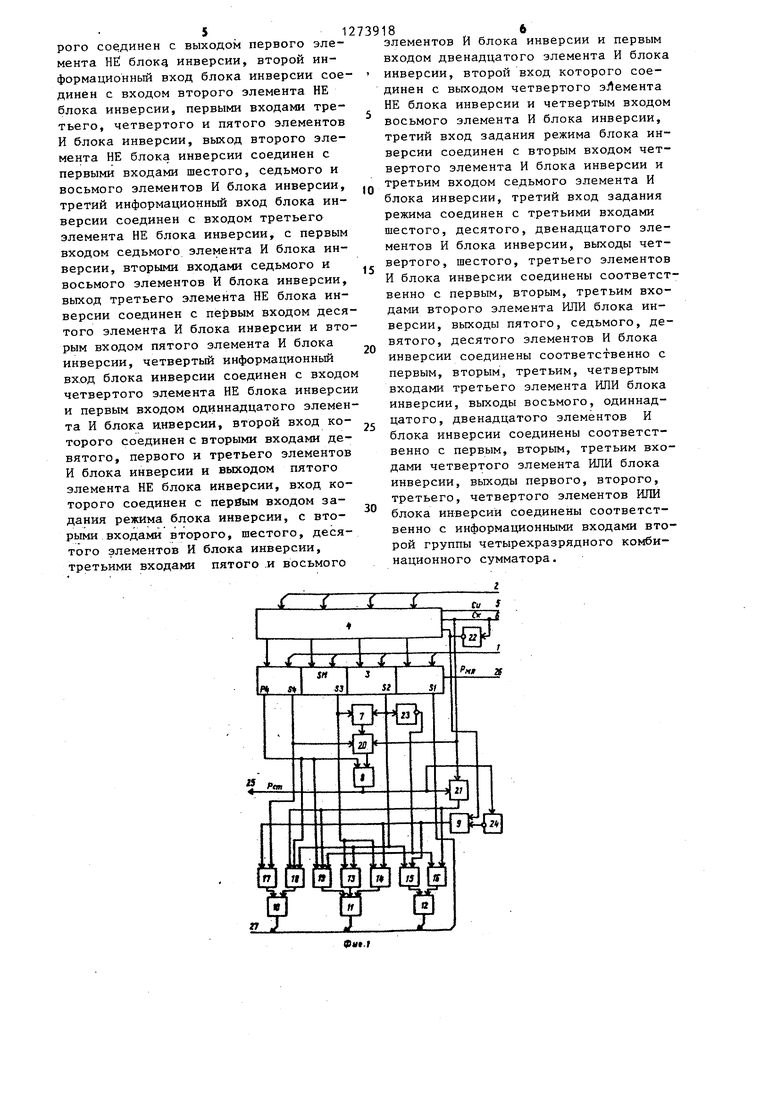

На фиг. 1 17редставлена функциональная схема одного десятичного разряда устройства для сложения - вычитания; на фиг. 2 - функциональная схема блока инверсии.

Устройство для сложения - вычитания (фиг. 1) содержит группы входов первого и второго слагаемого 1 и 2, четырехразрядный, комбинационный сумматор 3, блок 4 инверсии, вход 5 управления сложением-вычитанием, вход 6 управления выполнением операций в двоичной или двоично-десятичной системах счисления, шесть элементов ИЛИ 7-12, девять элементов И 13- 21, три элемента НЕ 22, 23 и 24, выход 25 переноса из предыдущего разряда, вход 26 переноса из предыдущего разряда, выход 27 результата.

Блок инверсии (фиг. 2) содержит пять элементов НЕ 28-32, вход 33 инверсии сигнала управления выполнением операций в двоичной и двоично-десятичной системах счисления, двенадцать элементов И 34-45, четыре элемента .ИЛИ 46-49, выходы 50 блока инверсии.

Блок инверсии управляется входами 5 (сигнал Си) и 6 (сигнал Ск).

Закон управления блоком инверсии следующий:

и или и , число с входов 3 проходит на вход сумматора 2, не меняясь;

-если и , на вход сумматора 2 поступает двоичная инверсия числа

-если и , на вход сумматора 3 поступает десятичная инверсия числа.

К выходам сумматора 2 подключены элементы ИЛИ 7 и 8 и элемент И 20, предназначенные для формирования переноса в старший разряд. Соединенны с выходами сумматора 3 элементы И 13-19, элементы ИЛИ 10, 11 и 12 и элемент НЕ 23 осуществляют десятичну коррекцию суммы S, если операция выполняется в десятичном коде и сумма . Управление коррекцией осуществляется с помощью элементов НЕ 22 и 24, элемента И 21 и элемента ИЛИ .9. На выходе 25 устройства формируется

перенос в старший разряд. С входа 26 в сумматор поступает перенос из младшего разряда. На выходах 27 фррмируется значение суммы.

Работу блока инверсии удобно записать системой булевых уравнений:

1 х1ЛСиУх1лСи:

2 х2лСкУх,ЛСкСиУх2лСи;

3 хЗлх2ЛСиУхЗЛх2ЛСкУхЗлСиУ

хЗЛСиЛСк;

4 х4ЛхЗЛх2лСиУх4ЛСиУх4лСиЛСк1

X и Устройство работает следующим образом.

Пусть необходимо выполнить операцию сложения в десятичном коде. На вход 5 подается сигнал О (), на вход 6 сигнал 1 (), на входы 1, 2 - коды слагаемых. Слагаемое X проходит через блок 4 инверсии, не меняясь, и складывается в сумматоре. В элементах ИЛИ 7 и 8, элементе И 20 формируется десятичный перенос в старш.ий разряд (он же и признак коррекции) , так как элемент И 20. открыт сигналом Ск 1 . Если Р.т 0 (), сумма S4, S3, S2, S1 проходит на выходы 27, не меняясь (через элементы И 15, 14 и 17), если . 1 (), сумма увеличивается на 0110 в блоке коррекции и также поступает на выходы 27.

Для выполнения операции вычитания в десятичном коде необходимо иметь , , на вход 1 подать уменьшаемое и на вход 2 - вычитаемое. В этом случае на входы сумматора 3 поступит код уменьшаемого и десятичная инверсия кода вычитаемого. Работа остальных блоков не изменится..

Для выполнения операции сложения в двоичном коде необходимо иметь , . Слагаемое X пройдет на входы сумматора 3 с входа 2, не меняясь. Так как , элемент И,20 закроется и на вход 25 будет поступать только перенос из сумматора 3 (т.е. перенос станет двоичным). Элемент И 22 будет генерировать О, элемент ИЛИ 9 - единицу, следовательно, блок коррекции окажется заблокированным и сумма S будет проходить на выходы 27, не меняясь.

Для реализации операции вычитания в двоичном коде необходимо иметь , 55 . В этом случае на входы сумматора 3 поступит двоичная инверсия кода с входов 2. Работа остальных блоков Tie изменится. Формула изобретения Устройство для сложения - вычитания, содержащее в каждой тетраде бло 1нверсии, четырехразрядный комбинационный сумматор, первьш, второй, третий элементы ИЛИ, первый элемент И, причем первая группа информационных входов четырехразрядного комбинационного сумматора соединена соответственно с группой входов первого слагаемого устройства, вход переноса четырехразрядного комбинационного сум матора соединен с входом переноса из младшего устройства, выход переноса четырехразрядного комбинационного сумматора соединен с первы входом первого элемента ИЛИ, второй вход которого соединен с выходом пер вого элемента И, первый вход которог соединен с четвертым разрядом выхода суммы четырехразрядного комбинационного сумматора, второй и третий разряды выхода суммы которого соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, входы разрядов второго операнда устройства соединены соответственно с первым, вторым, третьим, четвертым информационными входами блока инверсии, отличающееся тем, что, с целью упрощени устройства, в каждую тетраду введены первьш, второй, третий элементы НЕ, четвертый, пятый, шестой элементы ИЛИ, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый элементы И, причем второй разряд выхода суммы четырехразрядного комби национного сумматора соединен с первыми входами второго, третьего, четвертого элементов И и входом первого элемента НЕ,выход которого соединен с первыми входами пятого и шестого элементов И, выход первого элемента ИЛИ соединен с выходом переноса в следующий разряд устройства, с первым входом седьмого элементй И и вхо дом второго элемента НЕ, выход которого соединен с первым входом третье го элемента ИЛИ, выход которого соединен с первыми входами восьмого и девятого элементов И и с вторым входом второго элемента И, выход переноса четырехразрядного комбинационкого сумматора соединен с вторыми входами четвертого и шестого элементов И, первый разряд выхода суммы четырехразрядного комбинационного сумма тора соединен,с выходом первого разряда результата устройства, третий разряд выхода суммы четырехразрядного комбинационного сумматора соединен с вторыми входами третьего и девятого элементов И, четверть разряд выхода суммы четырехразрядного комбинационного сумматора соединен с вторым входом восьмого элемента И, выход седьмого элемента И соединен с третьими входами четвертого и шестого элементов И и вторым входом пятого элемента И, выходы пятого и второго элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен с выходом второго разряда результата устройства, выходы шестого, третьего, девятого элементов И соединены соответственно с первым, вторым, третьим входами пятого элемента ИЛИ, выход которого соединен с выходом третьего разряда результата устройства, выходы восьмого и четвертого элементов И соединены соответственно с первым и вторым входами шестого элемента ИЛИ, выход которого соединен с выходом четвертого разряда результата устройства, первьй вход задания режима блока инверсии соединен с входом управления сложением - вычитанием устройства, вход управления выполнением операций в двоичной или двоично-десятичной системах счисления устройства соединен с третьим входом первого элемента И, с вторым входом седьмого элемента И, с вторым входом задания режима блока инверсии и с входом третьего элемента НЕ, выход которого соединен с третьим входом задания режима блока инверсии и с вторым входом третьего элемента ИЛИ, причем блок инверсии содержит первый, второй, третий, четвертый, пятьм элементы НЕ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатьш, двенадцатый элементы И, первый, второй, третий, четвертьм элементы ИЛИ, причем первый информационньп вход блока инверсии соединен с входом первого элемента НЕ блока инверсии и с первым входом первого элемента И блока инверсии, выход которого соединен с первым входом первого элемента ИЛИ блока инверсии, второй вход которого соединен с выходом второго элемента И блока инверсии, первый вход кото5 .1 рого соединен с выходом первого элемента НЕ блокд инверсии, второй информационный вход блока инверсии сое динен с входом второго элемента НЕ блока инверсии, первыми входами третьего, четвертого и пятого элементов И &лока инверсии, выход второго элемента НЕ блока инверсии соединен с первыми входами шестого, седьмого и восьмого элементов И блока инверсии, третий информационный вход блока инверсии соединен с входом третьего элемента НЕ блока инверсии, с первым входом седьмого элемента И блока инверсии, вторыми входами седьмого и восьмого элементов И блока инверсии, выход третьего элемента НЕ блока инверсии соединен с первым входом деся того элемента И блока инверсии и вто рым входом пятого элемента И блока инверсии, четвертый информационный вход блока инверсии соединен с входо четвертого элемента НЕ блока инверси и первым входом одиннадцатого элемен та И блока инверсии, второй вход которого соединен с вторыми входами девятого, первого и третьего элементов И блока инверсии и выходом пятого элемента НЕ блока инверсии, вход которого соединен с перйым входом задания режима блока инверсии, с вторыми входами второго, шестого, десятого элементов И блока инверсии, третьими входаьш пятого .и восьмого 18 элементов И блока инверсии и первым входом двенадцатого элемента И блока инверсии, второй вход которого соединен с выходом четвертого эЛемента НЕ блока инверсии и четвертым входом восьмого элемента И блока инверсии, третий вход задания режима блока инверсии соединен с вторым входом четвертого элемента И блока инверсии и третьим входом седьмого элемента И блока инверсии, третий вход задания режима соединен с третьими входами шестого, десятого, двенадцатого элементов И блока инверсии, выходы четвертого, шестого, третьего элементов И блока инверсии соединены соответственно с первым, вторым, третьим входами второго элемента ИЛИ блока инверсии, выходы пятого, седьмого, девятого, десятого элементов И блока инверсии соединены соответственно с первым, вторым, третьим, четвертым входами третьего элемента ИЛИ блока инверсии, выходы восьмого, одиннадцатого, двенадцатого элементов И блока инверсии соединены соответственно с первым, вторым, третьим входами четвертого элемента ИЛИ блока инверсии, выходы первого, второго, третьего, четвертого элементов ИЛИ блока инверсий соединены соответственно с информационными входами второй группы четырехразрядного комбинационного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Двоично-десятичный сумматор | 1990 |

|

SU1728859A1 |

| Десятичный сумматор в избыточной системе счисления | 1988 |

|

SU1594524A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Десятичный сумматор в избыточной системе счисления | 1985 |

|

SU1256015A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

Изобретение может использоваться в области автоматики и вычислительной техники для выполнения операций в двоичной и двоично-десятичной системах счисления. Цель изобретения - упрощение устройства. В устройство для сложения-вычитания, содержащее в каждой тетраде лок инверсии, четырехразрядный комбинационный сумматор, три элемента ИЛИ, один элемент И, введены три элемента НЕ, три элемента ИЛИ, восемь элементов И. 2 ил.

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1985-06-25—Подача