I1

Изобретение относится к вычислительной технике,

Цель изобретения - расширение области применения за счет возможности суммирования N чисел, представленных в двоично-десятичной системе счисления .

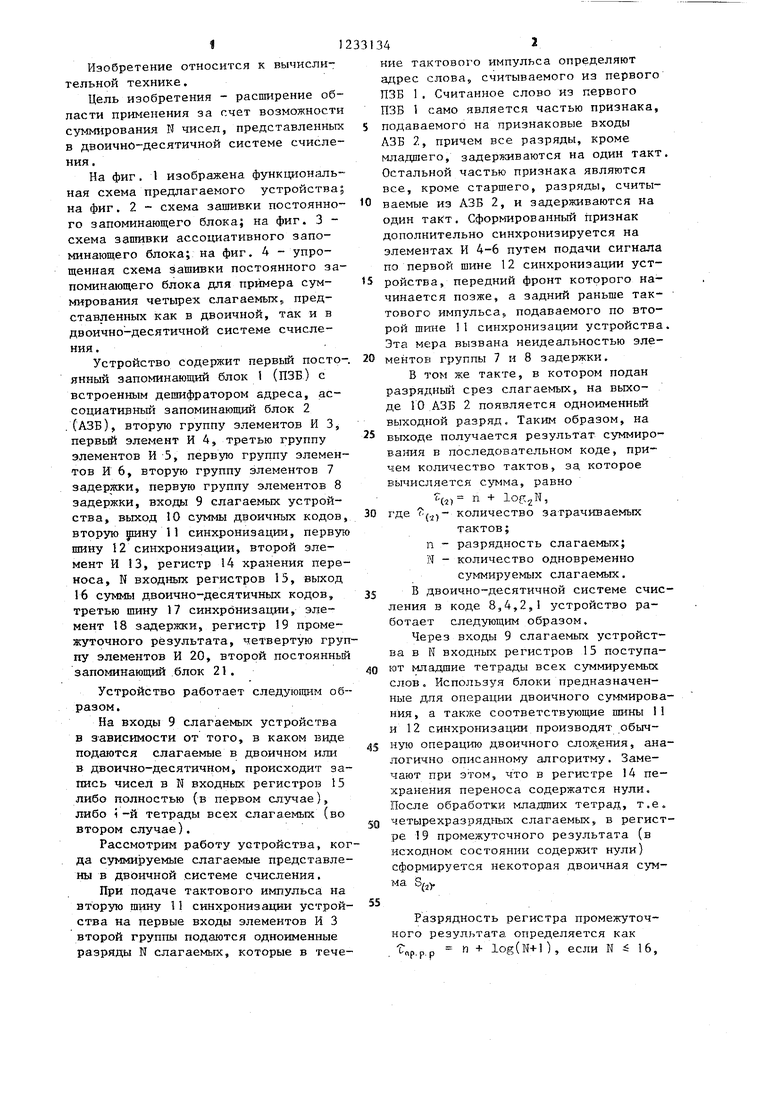

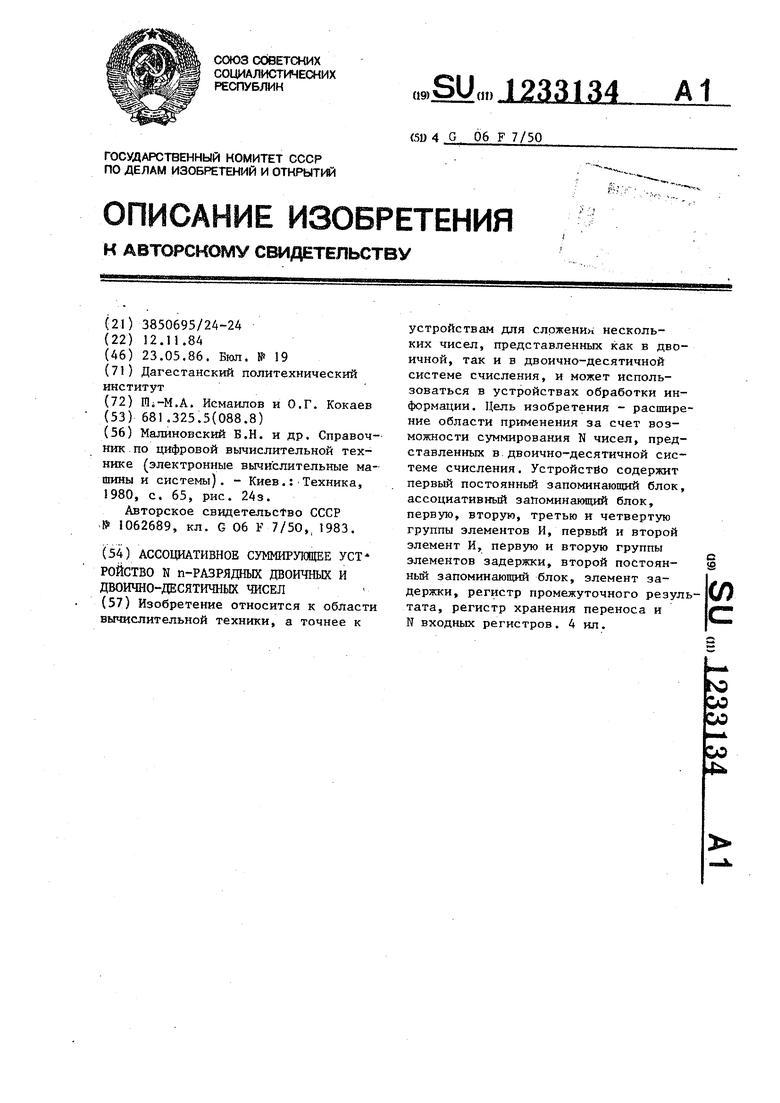

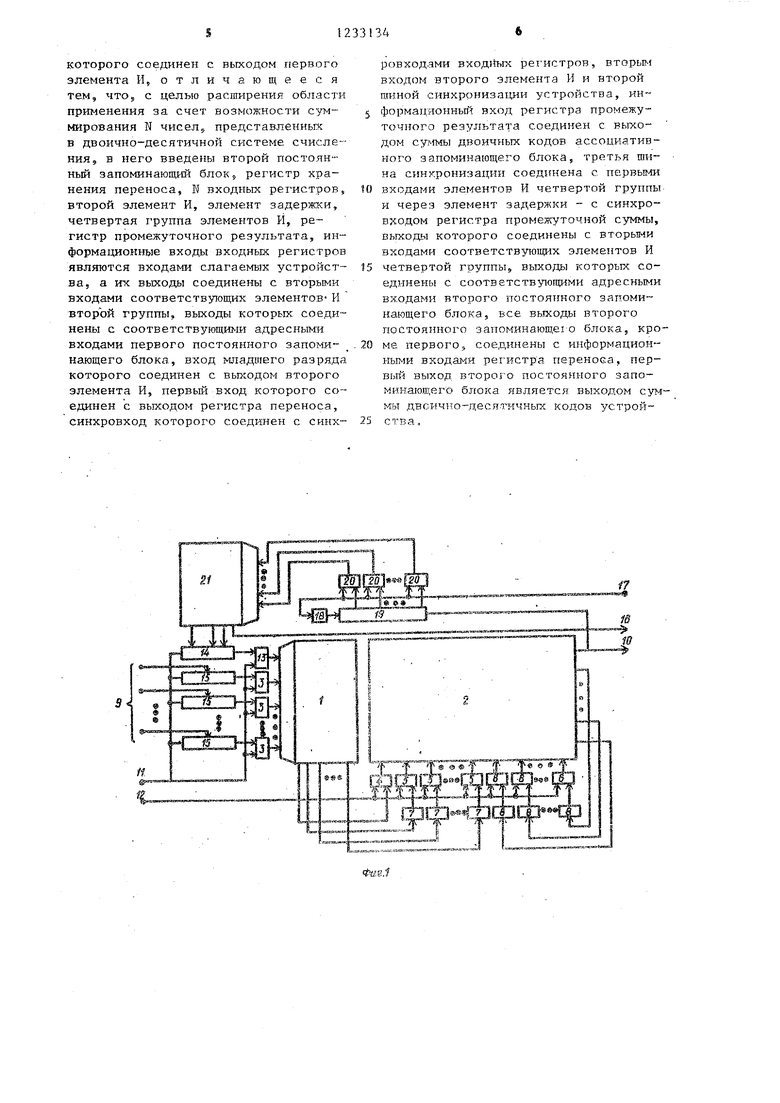

На фиг. 1 изображена функ1щональ- ная схема предлагаемого устройства5 на фиг. 2 - схема зашивки постоянно- го запоминающего блока; на фиг. 3 - схема зашивки ассоциативного запоминающего блока; на фиг. 4 - упрощенная схема зашивки постоянного запоминающего блока для примера сум- мирования четырех слагаемых., представленных как в двоичной, так и в двоично-десятичной системе счисления .

Устройство содержит первьй постоянный запоминающий блок 1 (ПЗБ) с встроенным дешифратором адреса, ассоциативный запоминающий блок 2 .(АЗБ), вторую группу элементов ИЗ, первый элемент И 4, третью группу элементов И -5, первую груцпу элементов И 6, вторую группу элементов 7 задержки, первую группу элементов 8 задержки, входы 9 слагаемых устройства, выход 10 суммы двоичных кодов, вторую 5рину II синхронизации, первую шину 12 синхронизации, второй элемент И 3, регистр 14 хранения переноса, N входных регистров 15, выход 16 суммы двоично-десятичных кодов, третью шину 17 синхронизации, элемент 18 задержки, регистр 19 промежуточного результата, четвертую группу элементов И 20, второй постоянный запоминающий блок 21.

Устройство работает следующим образом.

На входы 9 слагаемых устройства в зависимости от того, в каком виде подаются слагаемые в двоичном или в двоично-десятичном, происходит запись чисел в N входных регистров 15 либо полностью (в первом сл:учае), либо i -и тетрады всех слагаемых: (во втором случае).

Рассмотрим работу устройства, когда сумми руемые слагаемые представлены в двоичной системе счисления,

При подаче тактового импульса на вторую шину 11 синхронизации устрой- ства на первые входы элементов И 3 второй группы подаются одноименные разряды N слагаемых, которые в тече342

ние тактового импульса определяют адрес слова, считываемого из первого ПЗБ 1 . Считанное слово из первого ПЗБ 1 само является частью признака, подаваемого на признаковые входы ЛЗБ 2, причем все разряды, кроме младшего, задерживаются на один такт Остальной частью признака являются все, кроме старшего, разряды, считываемые из АЗВ 2, и задерживаются на один такт. Сформированный признак дополнительно синхронизируется на элементах И 4-6 путем подачи сигнала по первой шине 12 синхронизации устройства, передний фронт которого начинается позже, а задний раньше тактового импульса подаваемого по второй шине 11 синхронизации устройства Эта мера вызвана неидеальностью элементов группы 7 и 8 задержки.

В том же такте, в котором подан разрядньй срез слагаемых, на выходе 10 АЗБ 2 появляется одноименный выходной разряд. Таким образом, на выходе получается результат суммирования в последовательном коде, причем количество тактов, за которое вычисляется сумма, равно

(,, п + , где (j.;,- количество затрачиваемых

тактов;

п - разрядность слагаемых; N - количество одновременно суммируемых слагаемых,

В двоично-десятичной системе счисления в коде 8,4,2,1 устройство работает следующим образом,

Через входы 9 слагаемьгх устройства в N входных регистров 15 поступают младшие тетрады всех суммируемых слов. Используя блоки предназначенные дпя операции двоичного суммирования, а также соответствующие шины 11 и 12 синхронизации производят обычную операцию двоичного сложения, аналогично описанному алгоритму. Замечают при этом, что в регистре 4 пе- хранения переноса содержатся нули. После обработки младших тетрад, т.е. четырехразрядных слагаемых, в регистре 19 промежуточного результата (в исходном состоянии содержит нули) сформируется некоторая двоичная сумма В,

(2У

Разрядность регистра промежуточного результата определяется как . С пр.р.р п log(N+), если N ; 16,

гдеУ, - разряд ость регистра промежуточного результата; разрядность слагаемого (м-4) N - количество суммируемых слаraeNibix.

При подаче на третий тактовый вход 7 синхронизации устройства импульса происходит передача информации с регистра 19 промежуточного результата через элементы И 20 четвер- той группы на вход встроенного ратора адреса второго постоянного запоминающего блока 2, поступает информация с промежуточного результата регистра и в том же такте происходит его обнуление (время хранения информации в промежуточном регистре результата определяется элементом 18 задержки).

Организация второго постоянного запоминающего блока 21 следующая (фиг, 4).

На вход второго постоянного запо минающего блока 21 поступает информация с регистра промежуточного ре- зультата с учетом переноса из преды- дул(их тетрад. -Так как рассматривают двоичную сумму, полученную при сложении младших тетрад, то соответственно переносов из предьщущих тетрад нет. С выхода постоянного запоминающего блока 21 по соответствующему адресу считывается слово, которое содержит два вида информации, а именно вьщеляет разряд единиц в двоично

десятичном коде, содержащихся в сумме , а также остальные разряды (десятки, сотни, и т.д.) содержащиеся 5(2) в двоичном коде. Например: S(- lllllin 255,„ 1 10012 L, О101.,„,о.

L,

Полученная информация L в двоично-десятичном коде поступает на выходную шину 16 устройства, что является результатом суммирования уст- ройством младших тетрад. Информация, полученная с выхода второго постоянного запоминающего блока 21, Ь в двоичном коде поступает на входы регистра 14 хранения переноса, что и есть количество переносов, необходимых учесть при суммировании вторых тетрад всех слагаемых. Разрядность регистра 14 хранения переноса определяется как

tj,. log (N-1).,

Обработка следующих тетрад всех слагаемых происходит аналогично.

5

0 5

0

5 о

5

0

5 0

- Разрядность регистра переноса меньиге или равно четырем

(2-,.) + logj (N+l)l если N 1 16.

Разрядность регистра 14 переноса больше четырех.

( lORj(N-l.) + 10gj(N+l)}.

,Доя;2(11-1 ) Р,

где Р - разрядность двоично-десятичного числа.

Формула изоб ретення

Ассоциативное суммирующее устройство N п-разрядных двоичных и двоично-десятичных чисел, содержащее первый постоянньй запоминающий блок, ассоциативньш запоминаюпдгй блок, первьй элемент И, первую группу элементов И, вторую группу элементов И, третью группу элементов И, первую и вторую группы элементов задержки, первьш разрядный выход ассоциативного запоминающего блока является выходом суммы двоичных кодов, остальные выходы ассоциативного запоминающего блока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключен к первой шине синхронизации устройства, а выходы - к соответствующим входам опроса первой группы ассоциативного запоминающего блока, адресные входы первого постоянного запоминающего блока соединены с выходами соответствующих элемеитов И второй группы, первые входы которых соединены с второй шиной синхронизации устройства, первый разрядньш вьгход первого постоянного запоминающего блока соединен с первым входом первого элемента И, второй выход которого соединен с первыъш входами элементов И третьей группы и подключен к первой

шине элементов И третьей группы и I

подключен к первой шине синхронизации, выходы первого запоминающего блока, кроме первого, подключены через соответствующие элементы задержки второй группы ко вторым входам соответствующих элементов И третьей группы, выходы которых соединены с соответствующими входами опроса второй группы ассоциативного запоминающего блока, вход младшего разряда

которого соединен с выходом первого элемента И, отличающееся тем, 4TOj с целью расширения области применения за счет возможности суммирования N чисел, представленных в двоично-десятичной системе счисления, в него введены второй постоян- ньй запоминающий блок, регистр хранения переноса, К входных регистровs второй элемент И, элемент задержки, четвертая группа элементов И, регистр промежуточного результата, информационные входы входных регистров явл5ттся входами слагаемБ х устройства, а их выходы соединены с вторыми входами соответствующих элементов- И второй группы, выходы которых соединены с соответствующими адресными входами первого постоянного запоминающего блока, вход младшего разряда которого соединен с вькодом второго элемента И, первый вход которого соединен с выходом регистра переноса, синхровход которого соединен с синхровход.ами регистров, вторым входом второго элемента И и второй шиной синхронизации устройства, информащгонный вход регистра промежуточного результата соединен с выходом СУ1ЧМЫ двоичных кодов ассоциативного запоминающего блока, третья шина синкронизации соединена с первьми

входами элементов И четвертой группы и через элемент задержки - с синхро- ЕХОДОМ регистра промежуточной суммы, выходы которого соединены с вторьми входами соответствующих элементов И

четвертой группь, выходы которых соединены с соответствующими адресными В7 одами второго постоятшого запоминающего блока, все выходь второго постоянного запоминающего блока, кроме первого5 соединены с информационными входами регистра переноса, первый выход второго постоянного запо- минают;его блока является выходом суммы двср чно-десятичньп кодов устройс ТВ а.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное суммирующее устройство | 1986 |

|

SU1424011A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1978 |

|

SU742924A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

Изобретение относится к области вычислительной техники, а точнее к устройствам для сложении нескольких чисел, представленных как в двоичной, так и в двоично-десятичной системе счисления, и может использоваться в устройствах обработки информации. Цель изобретения - расширение области применения за счет возможности суммирования N чисел, представленных в. двоично-десятичной системе счисления. Устройство содержит первый постоянный запоминающий блок, ассоциативный затгоминакяций блок, первую, вторую, третью и четвертую группы элементов И, первый и второй элемент И, первую и вторую группы элементов задержки, второй постоян- ньй запоминающий блок, элемент задержки, регистр промежуточного результата, регистр хранения переноса и N входных регистров. 4 ил. (Л

Составитель М, Есенина .Редактор Н. Бобкова Техред Л.ОлёйникКорректор М. Демчик

-..„, „ ------------ - --- - -- - - -.

Заказ 2771/50 Тираж 67 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Малиновский Б.Н | |||

| и др | |||

| Справочник .по цифровой вычислительной технике (электронные вычислительные машины и системы) | |||

| - Киев.:Техника, 1980, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-11-12—Подача