1

Изобретение относится к области запоминающих устройств.

Известно устройство для контроля блоков оиеративной намяти, содержащее блок формирования управляющих токов, выходы которого подключены к выходным шинам устройства, а входы - к блоку управления и дешифартору адреса, соединенному с регистром адреса, усилитель считывания, нодключенный к входным щинам устройства.

Известное устройство не позволяет осуществить набор тестовых операций, который давал бы возможность воспроизвести реальные режимы работы элементов оперативной памяти. Кроме того, оно имеет недостаточную точыость и эффективность контроля.

Описываемое устройство отличается от известного тем, что оно содержит дешифратор тестовых операций и дополнительный регистр. Выходы последнего подключены к блоку уиравления, а выходы - к регистру адреса и входам дешифратора тестовых операций, выходы которого соединены с блоком управления. Это позволяет расширить область применения устройства и повысить точность его контроля.

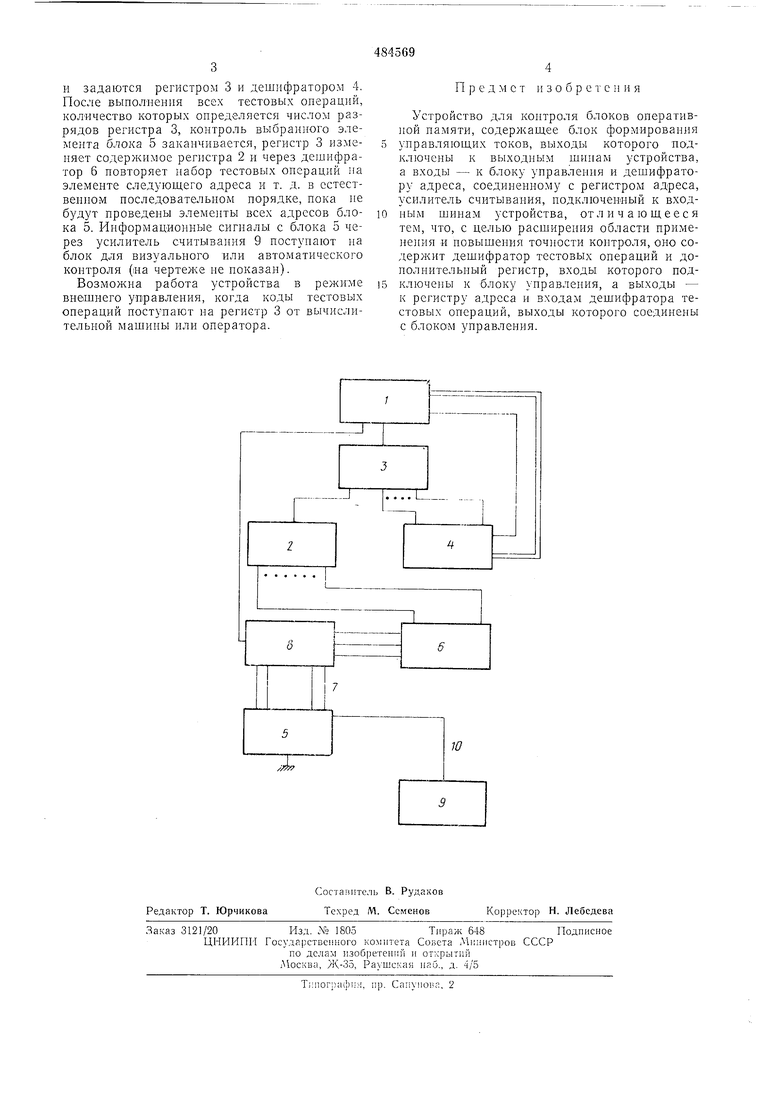

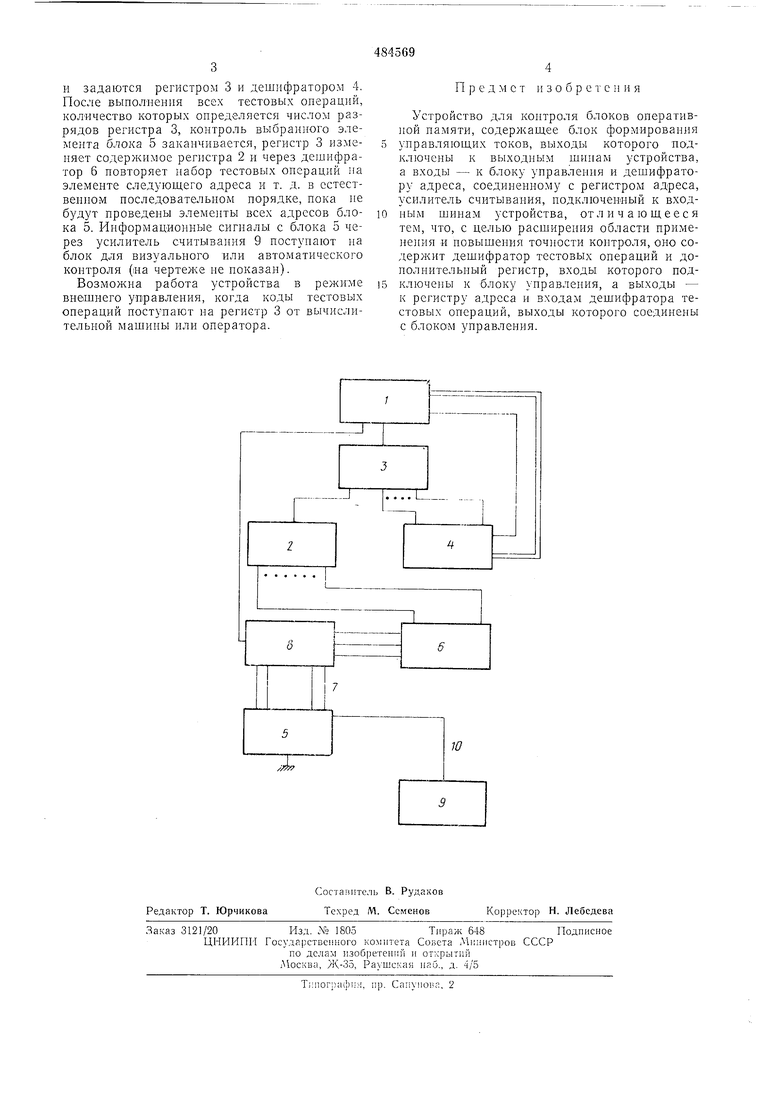

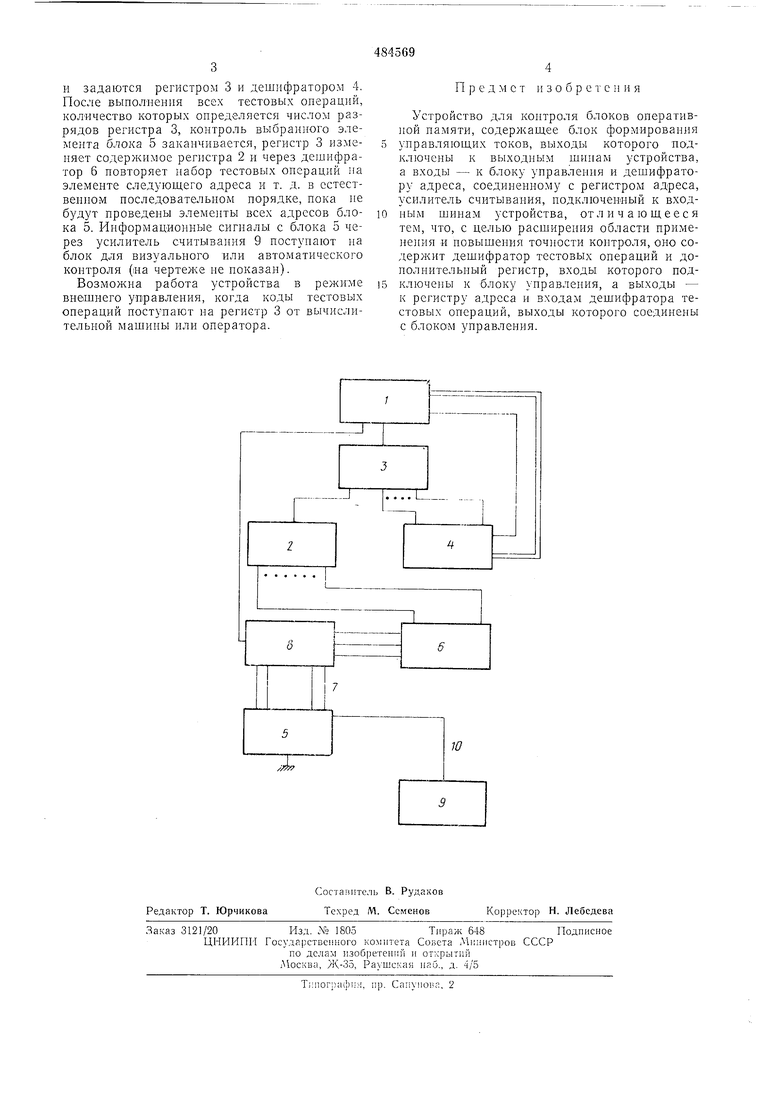

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит блок 1 управления, регистр 2 адреса, дополнительный регистр 3,

9

предназначенный для приема н хранения в нроцессе контроля двоичных кодов тестовых операций; дешифратор 4 для преобразования кода тестовых онераций в снг)1алы, унравляющие режимом контроля блока 5 оперативной памяти; дешифратор 6 адреса; выходные шины 7 устройства, к которым подключен блок оперативной памяти; блок 8 формирования управляющих токов и усилитель 9 считывания, подсоединенный к .в.ходным щпиам 10 устройства. Выходы регистра 3 нодключены к регистру 2 и входам дешифратора 4. Входы регистра 3 соединены с выходами блока 1, входы которого подключены к выходам дешифратора 4. Устройство работает следуюн1нм образом.

И.мпульсы, поступающие от блока 1 на вход регистра 3, последовательно формируют двоичные коды всего набора тестовых операций, используемых при контроле. Эти коды преобразуются дешифратором 4 в управляющие сигпалы, которые поступают в блок 1 н определяют в зависимости от выполняемой тестовой операции характер и последовательность вырабатываемых этим блоком сигналов для управления блоком 8. Таким образом, включение в работу отдельных узлов блока 8 и амплитудно-временные параметры формируемых импульсов токов могут быть разлнчны.мп

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для контроля каналов управления и сигнализации судовых энергетических установок | 1984 |

|

SU1177797A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство защиты и автоматики распределительной подстанции | 1988 |

|

SU1584023A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

Авторы

Даты

1975-09-15—Публикация

1973-09-28—Подача