1

Изобретение относится к области импульсной и вычислительной техники и может использоваться в различных устройствах дискретного действия (синтезаторах частот, частотных манипуляторах и т. д.).

Известно пересчетное устройство, содержащее источник сигнала, двоичный счетчик, выходы которого через дешифратор соединены со входами схемы «ИЛИ. Однако известное устройство не обеспечивает деления с нечетным коэффициентом деления и не сохраняет соотношения длительности импульса к паузе на выходе, равным 1:1.

Целью изобретения является сохранение соотношения длительностей импульса и паузы на выходе, равным 1:1 при нечетном коэффициенте деления.

Для этого один из входов дешифратора соединен с «леммой источника питания, а выход- с одним из управляющих входов двоичного счетчика, другой управляющий вход которого подключен к выходу схемы «ИЛИ.

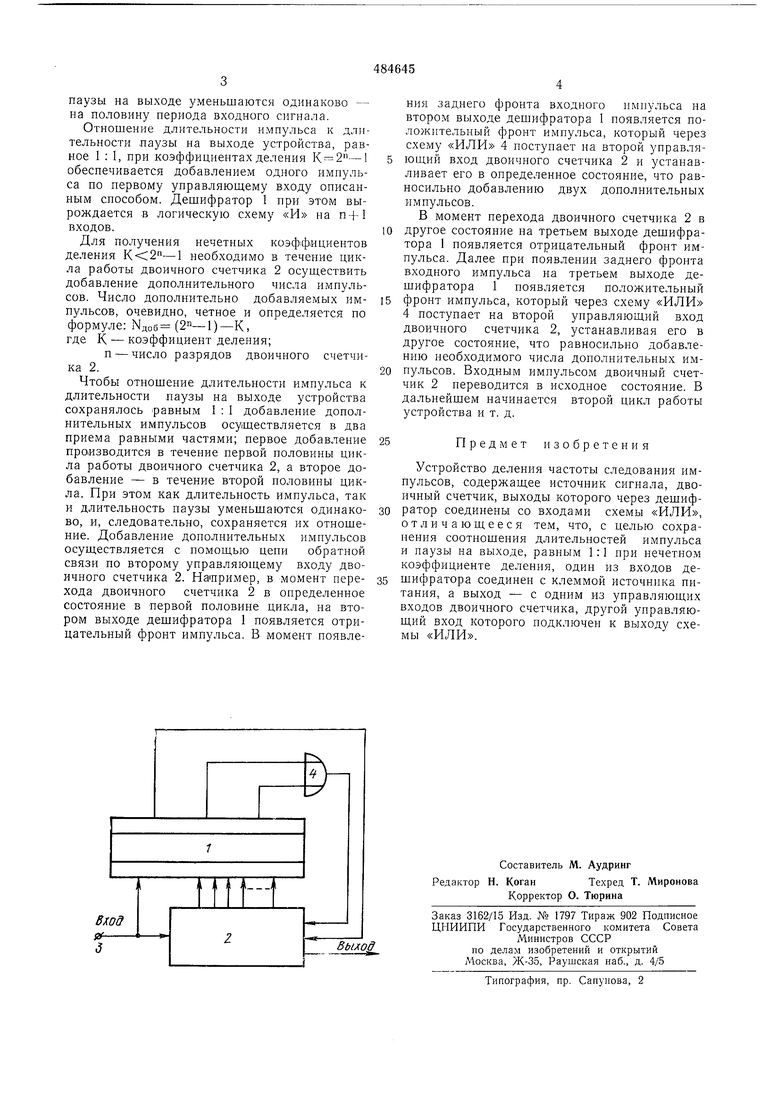

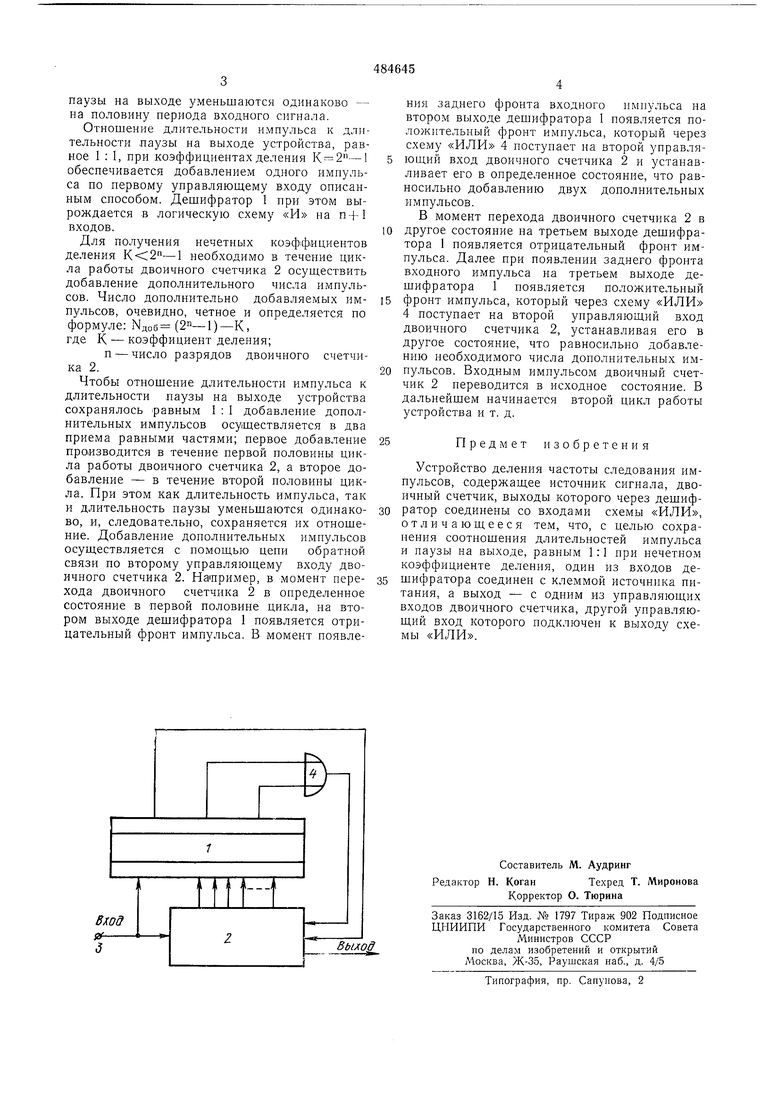

Блок-схема устройства деления частоты следования импульсов изображена на чертеже.

Устройство деления частоты следования импульсов состоит из дешифратора 1, подключенного к выходам двоичного счетчика 2 и к клемме 3 источника сигнала, первый выход дешифратора 1 соединен с одним из управляющих входов двоичного счетчика 2, а второй и третий выходы - через схему «ИЛИ 4 с другим управляющим входом двоичного счетчика 2.

Работает устройство следующим образом.

На вход устройства подается последовательность импульсов с отношением длительности импульса к длительно:сти паузы, равным 1:1. Переход счетчика из одного состояния в другое происходит в момент появления на его счетном или управляющих входах положительного фронта «мпульса.

В момент времени to двоичный счетчик 2 переходит в конечное () состояние, при этом на перво м выходе дешифратора 1 появляется отрицательный фронт импульса. Далее в момент появления заднего фронта входного импульса на первом Выходе дешифратора 1 появляется положительный фронт импульса, который поступает на первый управляющий вход двоичного счетчика 2 и устанавливает его в очередное состояние (состояние «О). Таким образом установка двоичного счетчика 2 по первому управляющему входу в состояние «О осуществляется с опережением на длительность паузы между входными импульсами. За счет введения обратной связи цикл работы устройства сокращается на единицу и коэффициент деления становится равным , а длительность импульса и

паузы на выходе уменьшаются одинаково - на половину периода входного сигнала.

Отношение длительности импульса к длительности паузы на выходе устройства, равное 1 : 1, при коэффициентах деления обеспечивается добавлением одного импульса по первому управляющему входу описанным способом. Дешифратор 1 при этом вырождается в логическую схему «И на п+1 входов.

Для получения нечетных коэффициентов деления необходимо в течение цикла работы двоичного счетчика 2 осуш,ествить добавление дополнительного числа импульсов. Число дополнительно добавляемых импульсов, очевидно, четное и определяется по формуле: ()-К, где К - коэффициент деления;

п - число разрядов двоичного счетчика 2.

Чтобы отношение длительности импульса к длительности паузы на выходе устройства сохранялась равным 1 : 1 добавление дополнительных импульсов осуществляется в два приема равными частями; первое добавление производится в течение первой половины цикла работы двоичного счетчика 2, а второе добавление - в течение второй иоловины цикла. При этом как длительность импульса, так и длительность паузы уменьшаются одинаково, и, следовательно, сохраняется их отношение. Добавление дополнительных импульсов осуш,ествляется с помош,ью цепи обратной связи по второму управляющему входу двоичного счетчика 2. Например, в момент перехода двоичного счетчика 2 в определенное состояние в первой половине цикла, на втором выходе дешифратора 1 появляется отрицательный фронт импульса. В момент появления заднего фронта входного импульса на втором выходе дешифратора 1 появляется положительный фронт импульса, который через схему «ИЛИ 4 поступает на второй управляющий вход двоичного счетчика 2 и устанавливает его в определенное состояние, что равносильно добавлению двух дополнительных импульсов. В момент перехода двоичного счетчика 2 в

другое состояние на третьем выходе дешифратора 1 появляется отрицательный фронт импульса. Далее при появлении заднего фронта входного импульса на третьем выходе дешифратора 1 появляется положительный

фронт импульса, который через схему «ИЛИ 4 поступает на второй управляющий вход двоичного счетчика 2, устанавливая его в другое состояние, что равносильно добавлению необходимого числа дополнительных импульсов. Входным импульсом двоичный счетчик 2 переводится в исходное состояние. В дальнейшем начинается второй цикл работы устройства и т. д.

Предмет изобретения

Устройство деления частоты следования импульсов, содержащее источник сигнала, двоичный счетчик, выходы которого через дешифратор соединены со входами схемы «ИЛИ, отличающееся тем, что, с целью сохранения соотношения длительностей импульса и паузы на выходе, равпым 1:1 при печетпом коэффициенте деления, один из входов дешифратора соединен с клеммой источника питания, а выход - с одним из управляющих входов двоичного счетчика, другой управляющий вход которого подключеи к выходу схемы «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов Е.М.Хайкина | 1980 |

|

SU936431A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Управляемый делитель частоты следования импульсов | 1981 |

|

SU999166A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

| Делитель частоты импульсов | 1983 |

|

SU1162037A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ИЗМЕНЯЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1996 |

|

RU2134485C1 |

| Делитель частоты с нечетным коэффициентом деления (его варианты) | 1982 |

|

SU1132368A1 |

| Устройство для измеерния неравномерности группового времени запаздывания | 1972 |

|

SU481858A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

Авторы

Даты

1975-09-15—Публикация

1973-12-03—Подача