(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Буферное запоминающее устройство | 1981 |

|

SU995123A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Вычислительная система | 1983 |

|

SU1233159A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в буферных запоминающих устройствах (БЗУ) подсистем ввода измерительной информации в многомодульные системы обработки.

Известно БЗУ, содержащее регистры, каждый из которых состоит из информационных и маркерного разрядов, узлы управления перезаписью и узел поиска старшего из свободных регистров 1.

Недостатком известного устройства является малая пропускная способность.

Наиболее близким к предложенному по технической сущности является БЗУ, содержащее поразрядно соединенные регистры . и логические схемы по числу регистров. Логические схемы выбирают регистр, куда должна записываться входная информация. Входная щина БЗУ подключена к каждому регистру, а выходная - к последнему. Сигналы состояния каждого регистра (полный или пустой) используются в логических схемах вместе с синхросигналами для записи данных в пустой регистр, предшествующий первому полному регистру. Данные каждого регистра сдвигаются к выходу, если этот регистр полный, а следующий пустой. При

использовании этого БЗУ в многомодульныхсистемах обработки на вход устройства вместе с данными подается и унитарный код назначения, каждый разряд которого соответствует назначению на обработку определенному модулю. Для обеспечения максимальной производительности многомодульной системы обработки каждое слово должно иметь возможность поступать на обработку в несколько модулей. При этом задача правления данных на обработку в определенный модуль рещается в зависимости от приоритетов модулей 2.

Недостатком известного БЗУ является неравномерность выдачи информации для внещних устройств, что снижает пропускную

15 способность устройства.

Цель изобретения - расширение функциональных возможностей за счет обеспечения равномерной выдачи информации для внешних устройств.

20 Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее последовательно соединенные регистры, выходы каждого из которых подключены к одним входам последующего регистра, а другие входы регистров объедийены и являются входами устройства, последовательно соединенные логические блоки, первый вход-выход каждого логического блока подключен ко второму входу-выходу последующего логического блока, третьи входы-выходы логических блоков подключены к управляющим входам-выходам соответствующих регистров, дополнительно введены блок анализа кодов назначения, одни входы которого подключены к соответствующим выходам регистров, блок определения длины очереди, одни входы которого подключены к входам устройства, а другие - к соответствующим выходам последнего регистра, мажоритарный элемент, входы которого подключены к другим выходам блока анализа кодов назначения, блок поиска минимальной очереди, первый вход которого подключен к выходу мажоритарного элемента, вторые входы блока поиска минимальной очереди подключены к выходам блока определения длины очереди, а третьи входы блока поиска минимальной очереди подключены к одним выходам блока анализа кодов назначения, блок элементов И, одни входы которого подключены к другим выходам блока анализа кодов назначения, другие входы - к выходам блока поиска минимальной очереди, щифратор, входы которого подключены к выходам блока элементов И, и регистр состояния, выходы которого подключены к другим входам блока анализа кодов назначения.

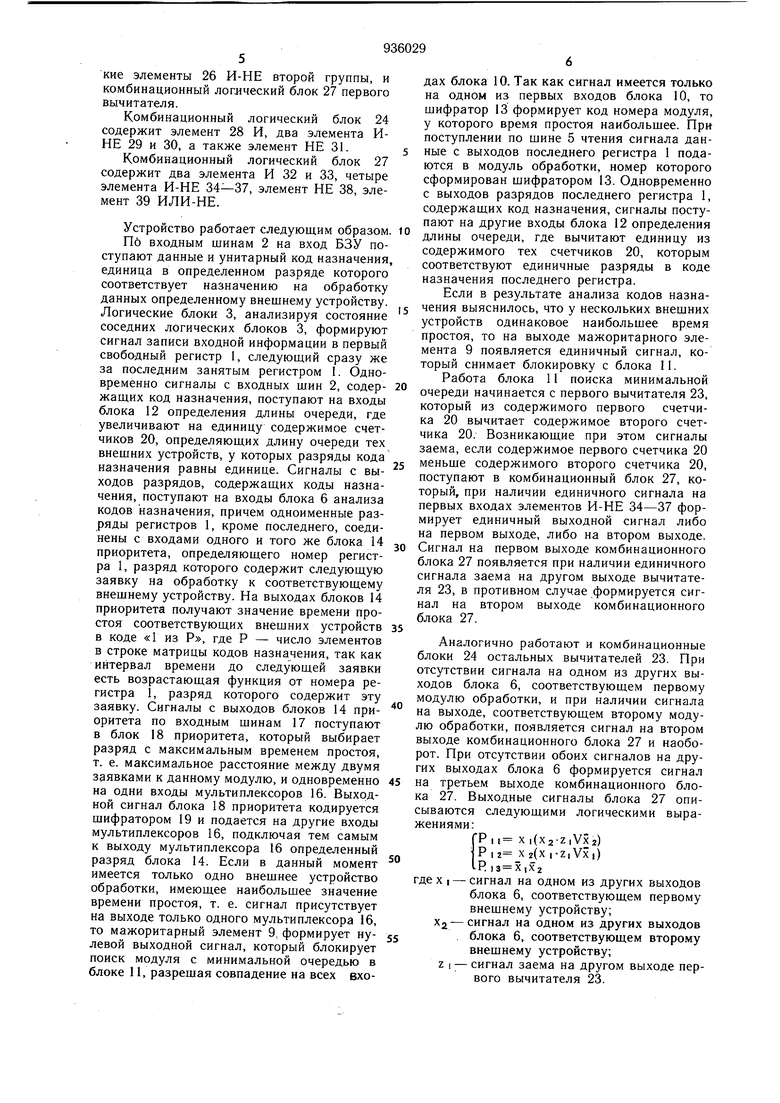

Блок анализа кодов назначения содержит блок приоритета, группу блоков приоритета, мультиплексоры, элементы И и шифратор, выход которого подключен к управляющим входам мультиплексоров, входы шифратора подключены к выходам блока приоритета, входы которого подключены к выходам блоков приоритета группы и к информационным входам мультиплексоров, одни входы блоков приоритета группы подключены к выходам соответствующих элементов И и являются одними выходами блока анализа кодов назначения, другие входы блоков приоритета группы являются одними входами блока анализа кодов назначения, одн входы элементов И являются другими входами блока анализа кодов назначения, а другие входы элементов И являются соответствующими входами блока анализа кодов назначения, выходы мультиплексоров являются другими выходами блока анализа кодов назначения.

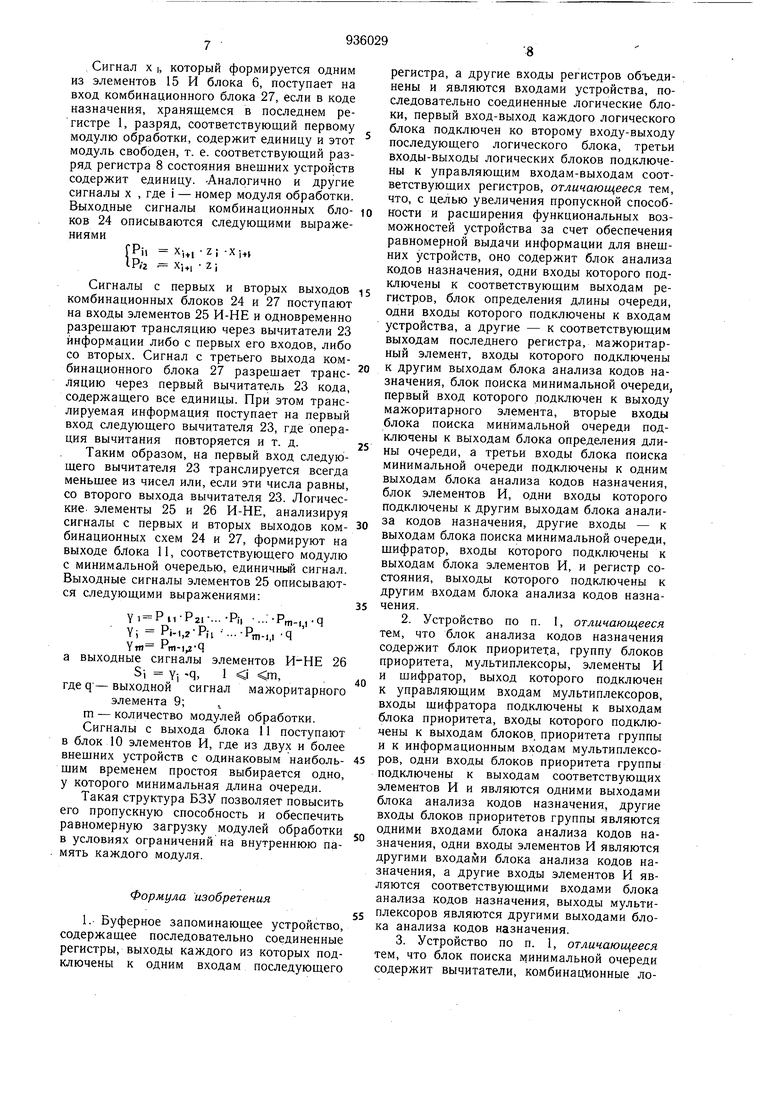

Блок поиска минимальной очереди содержит вычитатели, комбинационные логические блоки и две группы элементов И-НЕ, причем выходы элементов И-НЕ первой группы являются выходами блока поиска минимальной очереди, одни входы элементов И-НЕ первой группы подключены к выходам элементов И-НЕ второй группы, одни входы которых подключены к другим входам элементов И-НЕ первой группы и являются

третьим входом блока поиска минимальной очереди, другие входы элементов И-НЕ второй группы подключены к выходам соответствующих комбинационных блоков, одни входы которых являются вторыми входами блока поиска минимальной очереди, другие входы комбинационных блоков подключены к одним выходам соответствующих вычитателей, вторые входы рычитателей являются первыми входами блока поиска минимальной очереди, третьи входы каждого вычитателя подключены к вторым выходам соответствующего вычитателя.

Кроме того, блок определения длины очереди содержит реверсивные счетчики, одни и другие входы которых являются соответственно одними и другими входами блока определения длины очереди, а выходы реверсивных счетчиков являются выходами блока определения длины очереди.

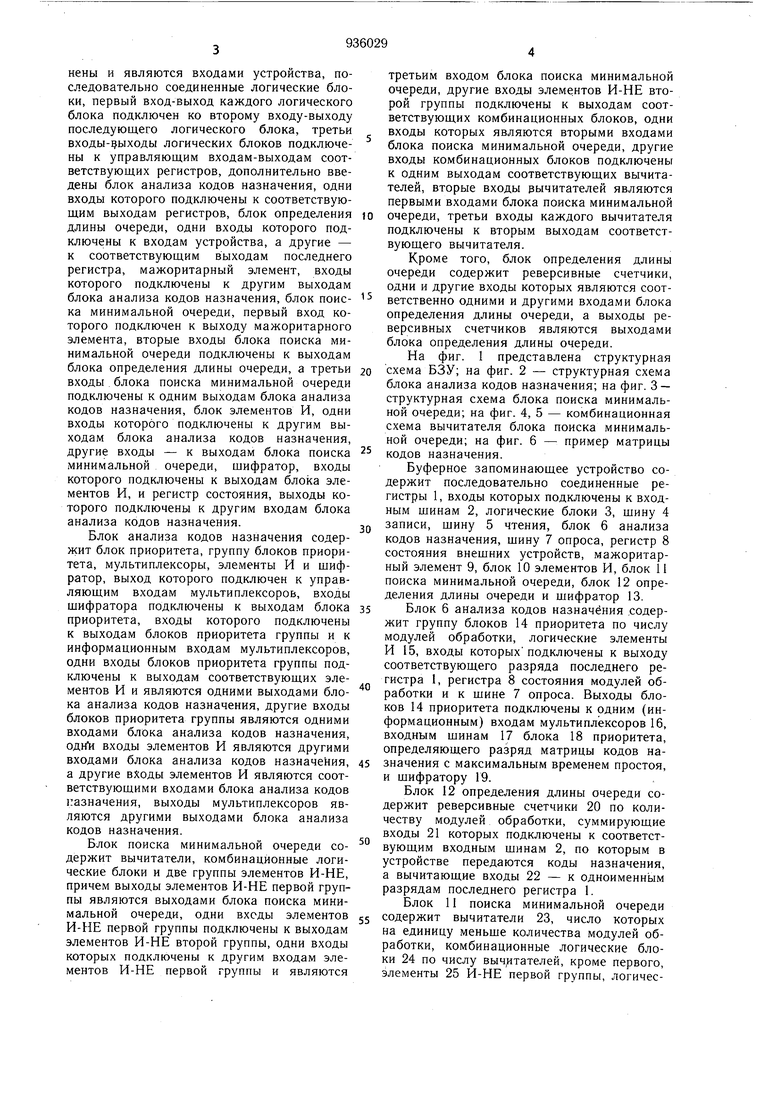

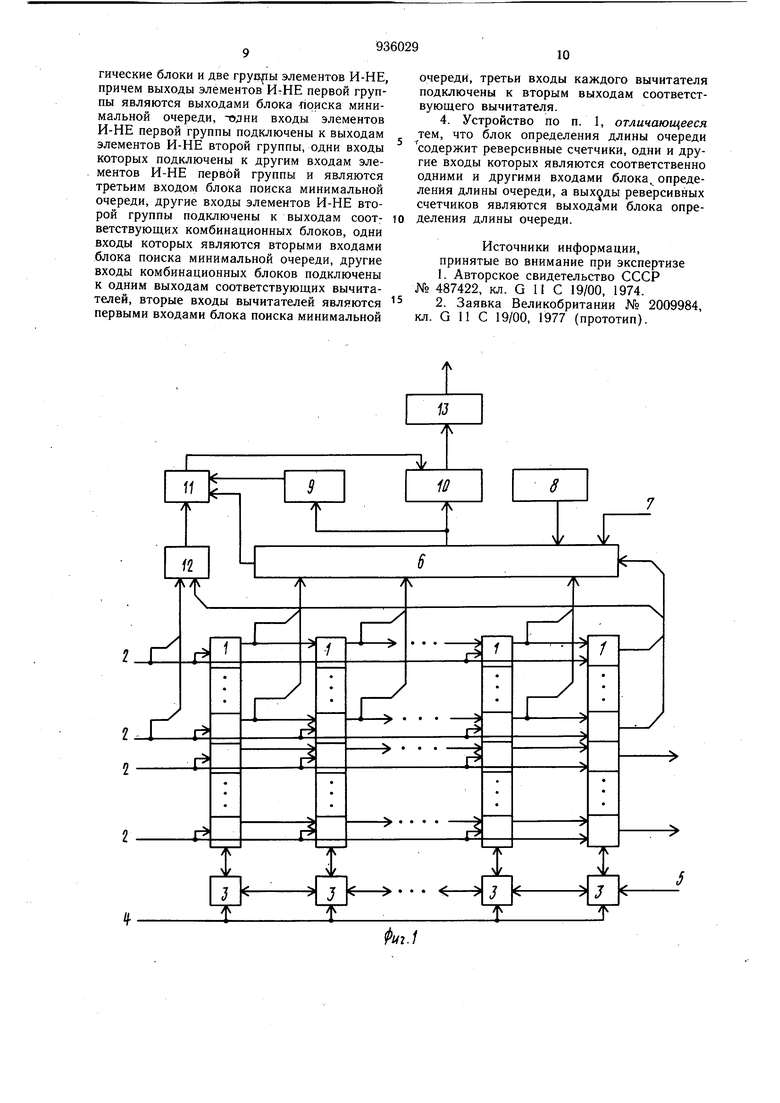

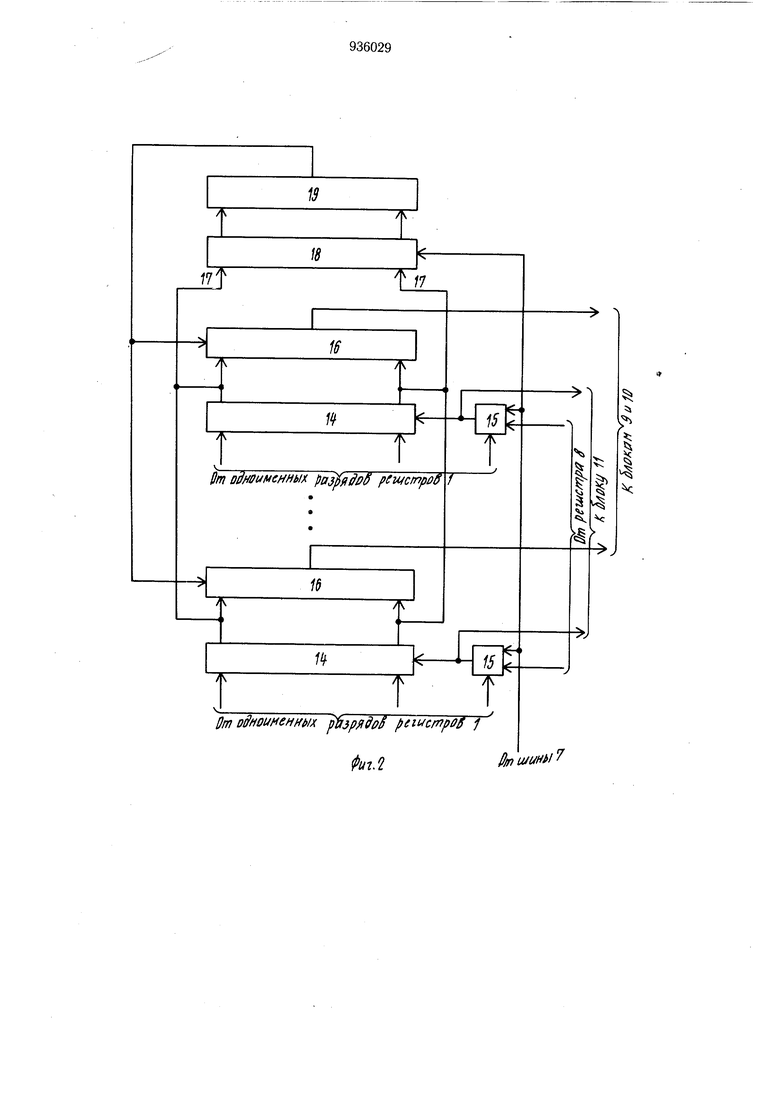

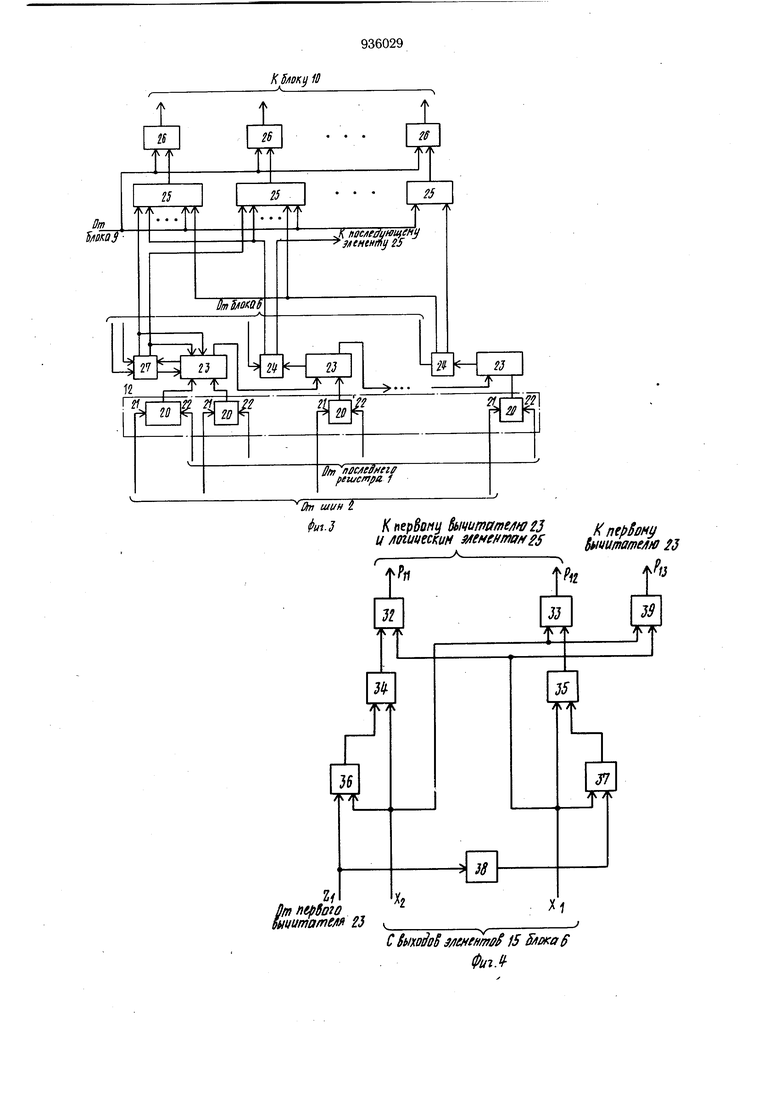

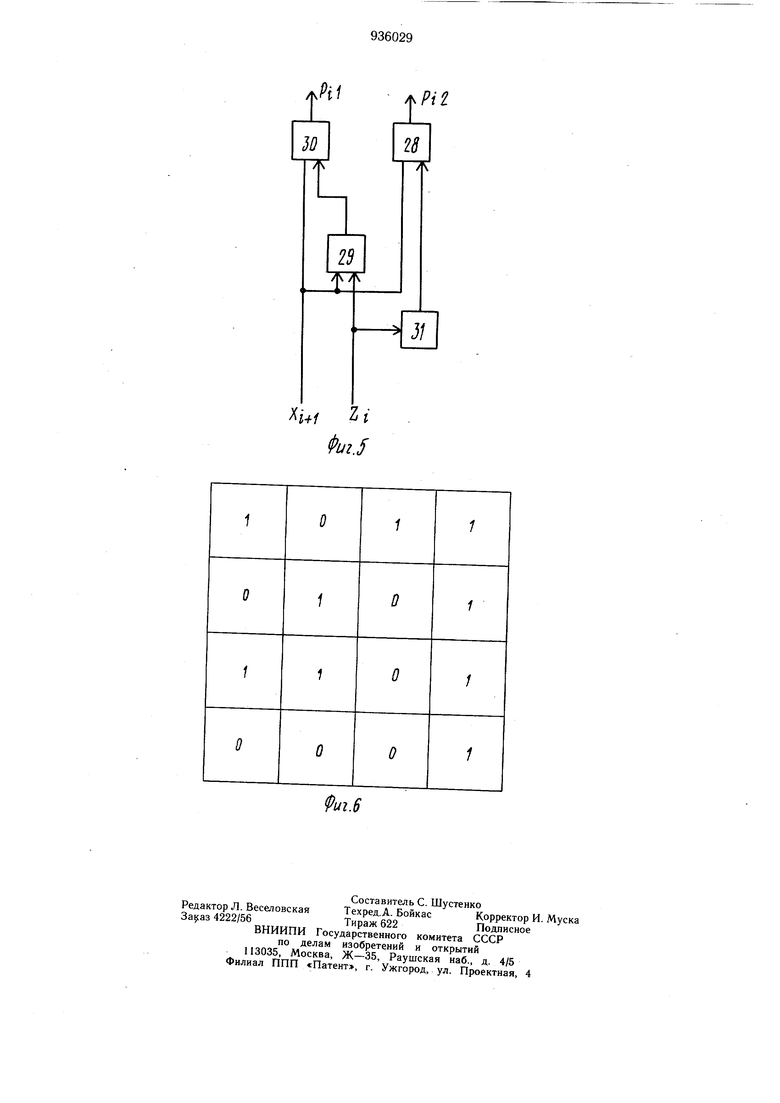

На фиг. 1 представлена структурная схема БЗУ; на фиг. 2 - структурная схема блока анализа кодов назначения; на фиг. 3 - структурная схема блока поиска минимальной очереди; на фиг. 4, 5 - комбинационная схема вычитателя блока поиска минимальной очереди; на фиг. 6 - пример матрицы кодов назначения.

Буферное запоминающее устройство содержит последовательно соединенные регистры 1, входы которых подключены к входным щинам 2, логические блоки 3, шину 4 записи, шину 5 чтения, блок 6 анализа кодов назначения, шину 7 опроса, регистр 8 состояния внешних устройств, мажоритарный элемент 9, блок 10 элементов И, блок 11 поиска минимальной очереди, блок 12 определения длины очереди и шифратор 13.

Блок б анализа кодов назначения .содержит группу блоков 14 приоритета по числу модулей обработки, логические элементы И 15, входы которыхподключены к выходу соответствующего разряда последнего регистра 1, регистра 8 состояния модулей обработки и к шине 7 опроса. Выходы блоков 14 приоритета подключены к одним (информационным) входам мультиплексоров 16, входным шинам 17 блока 18 приоритета, определяющего разряд матрицы кодов назначения с максимальным временем простоя, и шифратору 19.

Блок 12 определения длины очереди содержит реверсивные счетчики 20 по количеству модулей обработки, суммирующие входы 21 которых подключены к соответствующим входным шинам 2, по которым в устройстве передаются коды назначения, а вычитающие входы 22 - к одноименным разрядам последнего регистра 1.

Блок 11 поиска минимальной очереди содержит вычитатели 23, число которых на единицу меньше количества модулей обработки, комбинационные логические блоки 24 по числу выч тaтeлeй, кроме первого, элементы 25 И-НЕ первой группы, логические элементы 26 И-НЕ второй группы, и комбинационный логлческий блок 27 первого вычитателя. Комбинационный логический блок 24 содержит элемент 28 И, два элемента ИНЕ 29 и 30, а также элемент НЕ 31. Комбинационный логический блок 27 содержит два элемента И 32 и 33, четыре элемента И-НЕ 34-37, элемент НЕ 38, элемент 39 ИЛИ-НЕ. Устройство работает следующим образом. По входным щинам 2 на вход БЗУ поступают данные и унитарный код назначения, единица в определенном разряде которого соответствует назначению на обработку данных определенному внешнему устройству. Логические блоки 3, анализируя состояние соседних логических блоков 3, формируют сигнал записи входной информации в первый свободный регистр 1, следующий сразу же за последним занятым регистром 1. Одновременно сигналы с входных шин 2, содержащих код назначения, поступают на входы блока 12 определения длины очереди, где увеличивают на единицу содержимое счетчиков 20, определяющих длину очереди тех внещних устройств, у которых разряды кода -- . 1--г-г-- - --- назначения равны единице. Сигналы с выходов разрядов, содержащих коды назначения, поступают на входы блока 6 анализа кодов назначения, причем одноименные разряды регистров 1, кроме последнего, соединены с входами одного и того же блока 14 приоритета, определяющего номер регистра 1, разряд которого содержит следующую заявку на обработку к соответствующему внешнему устройству. На выходах блоков 14 приоритета получают значение времени простоя соответствующих внешних устройств в коде «Г из Р, где Р - число элементов в строке матрицы кодов назначения, так как интервал времени до следующей заявки есть возрастающая функция от номера регистра 1, разряд которого содержит эту заявку. Сигналы с выходов блоков 14 приоритета по входным щинам 17 поступают в блок 18 приоритета, который выбирает разряд с максимальным временем простоя, т. е. максимальное расстояние между двумя заявками к данному модулю, и одновременно на одни входы мультиплексоров 16. Выходной сигнал блока 18 приоритета кодируется щифратором 19 и подается на другие входы мультиплексоров 16, подключая тем самым к выходу мультиплексора 16 определенный разряд блока 14. Если в данный момент имеется только одно внещнее устройство обработки, имеющее наибольщее значение времени простоя, т. е. сигнал присутствует на выходе только одного мультиплексора 16, то мажоритарный элемент 9, формирует нулевой выходной сигнал, который блокирует поиск модуля с минимальной очередью в блоке 11, разрешая совпадение на всех входах блока 10. Так как сигнал имеется только на одном из первых входов блока 10, то шифратор 13 формирует код номера модуля, у которого время простоя наибольшее. При поступлении по шине 5 чтения сигнала данные с выходов последнего регистра 1 подаются в модуль обработки, номер которого сформирован шифратором 13. Однорременно с выходов разрядов последнего регистра 1, содержащих код назначения, сигналы поступают на другие входы блока 12 определения д,„у очереди, где вычитают единицу из содержимого тех счетчиков 20, которым соответствуют единичные разряды в коде назначения последнего регистра. Если в результате анализа кодов назначения выяснилось, что у нескольких внешних устройств одинаковое наибольшее время простоя, то на выходе мажоритарного элемента 9 появляется единичный сигнал, который снимает блокировку с блока 11. Работа блока 11 поиска минимальной опереди начинается с первого вычитателя 23, который из содержимого первого счетчика 20 вычитает содержимое второго счетчика 20. Возникающие при этом сигналы заема, если содержимое первого счетчика 20 меньще содержимого второго счетчика 20, поступают в комбинационный блок 27, который, при наличии единичного сигнала на первых входах элементов И-НЕ 34-37 формирует единичный выходной сигнал либо на первом выходе, либо на втором выходе. Сигнал на первом выходе комбинационного блока 27 появляется при наличии единичного сигнала заема на другом выходе вычитателя 23, в противном случае формируется сигнал на втором выходе комбинационного блока 27. Аналогично работают и комбинационные блоки 24 остальных вычитателей 23. При отсутствии сигнала на одном из других выходов блока 6, соответствующем первому модулю обработки, и при наличии сигнала на выходе, соответствующем второму модулю обработки, появляется сигнал на втором выходе комбинационного блока 27 и наоборот. При отсутствии обоих сигналов на других выходах блока 6 формируется сигнал на третьем выходе комбинационного блока 27. Выходные сигналы блока 27 описываются следующими логически.ми выражениями:Р 11 X |(X2-Z|VX2) Pl2 Xz(Xi-ZiVXi) IP ,X2 где X I - сигнал на одном из других выходов блока 6, соответствующем первому внещнему устройству; Xj-сигнал на одном из других выходов . блока 6, соответствующем второму внещнему устройству; Z I - сигнал заема на другом выходе первого вычитателя 23. Сигнал X 1, который формируется одним из элементов 15 И блока б, поступает на вход комбинационного блока 27, если в коде назначения, хранящемся в последнем регистре 1, разряд, соответствующий первому модулю обработки, содержит единицу и этот модуль свободен, т. е. соответствующий разряд регистра 8 состояния внешних устройств содержит единицу. -Аналогично и другие сигналы X , где i - номер модуля обработки. Выходные сигналы комбинационных блоков 24 описываются следующими выражениями1 Pji х-|, Z ; -х i+f lP/2 Х Сигналы с первых и вторых выходов комбинационных блоков 24 и 27 поступают на входы элементов 25 И-НЕ и одновременно разрешают трансляцию через вычитатели 23 информации либо с первых его входов, либо со вторых. Сигнал с третьего выхода комбинационного блока 27 разрешает трансляцию через первый вычитатель 23 кода, содержащего все единицы. При этом транслируемая информация поступает на первый вход следующего вычитателя 23, где операция вычитания повторяется и т. д. Таким образом, на первый вход следующего вычитателя 23 транслируется всегда меньшее из чисел или, если эти числа равны, со второго выхода вычитателя 23. Логические, элементы 25 и 26 И-НЕ, анализируя сигналы с первых и вторых выходов комбинационных схем 24 и 27, формируют на выходе блока 11, соответствующего модулю с минимальной очередью, единичный сигнал. Выходные сигналы элементов 25 описываются следующими выражениями: У1 Ри-Р2Г...-Pii ...Pm-,,,.q Yi Pi-i,2-P,-i ...Pm-i,i Ч Ytn Pffl-M-q a выходные сигналы элементов И-НЕ 26 Si Yi -q, 1 i m. где q-выходной сигнал мажоритарного элемента 9; m - количество модулей обработки. Сигналы с выхода блока 11 поступают в блок 10 элементов И, где из двух и более внешних устройств с одинаковым наибольшим временем простоя выбирается одно, у которого минимальная длина очереди. Такая структура БЗУ позволяет повысить его пропускную способность и обеспечить равномерную загрузку модулей обработки в условиях ограничений на внутреннюю память каждого модуля. Формула изобретения 1.- Буферное запоминающее устройство, содержащее последовательно соединенные регистры, выходы каждого из которых подключены к одним входам последующего регистра, а другие входы регистров объединены и являются входами устройства, последовательно соединенные логические блоки, первый вход-выход каждого логического блока подключен ко второму входу-выходу последующего логического блока, третьи входы-выходы логических блоков подключены к управляющим входам-выходам соответствующих регистров, отличающееся тем, что, с целью увеличения пропускной способности и расщирения функциональных возможностей устройства за счет обеспечения равномерной выдачи информации для внещних устройств, оно содержит блок анализа кодов назначения, одни входы которого подключены к соответствующим выходам регистров, блок определения длины очереди, одни входы которого подключены к входам устройства, а другие - к соответствующим выходам последнего регистра, мажоритарный элемент, входы которого подключены к другим выходам блока анализа кодов назначения, блок поиска минимальной очереди, первый вход которого подключен к выходу мажоритарного элемента, вторые входы блока поиска минимальной очереди подключены к выходам блока определения длины очереди, а третьи входы блока поиска минимальной очереди подключены к одним выходам блока анализа кодов назначения, блок элементов И, одни входы которого подключены к другим выходам блока анализа кодов назначения, другие входы - к выходам блока поиска минимальной очереди, шифратор, входы которого подключены к выходам блока элементов И, и регистр состояния, выходы которого подключены к другим входам блока анализа кодов назначения. 2.Устройство по п. 1, отличающееся тем, что блок анализа кодов назначения содержит блок приоритета, группу блоков приоритета, мультиплексоры, элементы И и шифратор, выход которого подключен к управляющим входам мультиплексоров, входы щифратора подключены к выходам блока приоритета, входы которого подключены к выходам блоков, приоритета группы и к информационным входам мультиплексоров, одни входы блоков приоритета группы подключены к выходам соответствующих элементов И и являются одними выходами блока анализа кодов назначения, другие входы блоков приоритетов группы являются одними входами блока анализа кодов назначения, одни входы элементов И являются другими входами блока анализа кодов назначения, а другие входы элементов И являются соответствующими входами блока анализа кодов назначения, выходы мультиплексоров являются другими выходами блока анализа кодов назначения. 3.Устройство по п. 1, отличающееся тем, что блок поиска минимальной очереди содержит вычитатели, комбинащнонные логические блоки и две элементов И-НЕ, причем выходы элементов И-НЕ первой группы являются выходами блока поиска минимальной очереди, -одни входы элементов И-НЕ первой группы подключены к выходам элементов И-НЕ второй группы, одни входы которых подключены к другим входам элементов И-НЕ первой группы и являются третьим входом блока поиска минимальной очереди, другие входы элементов И-НЕ второй группы подключены к выходам соответствующих комбинационных блоков, одни входы которых являются вторыми входами блока поиска минимальной очереди, другие входы комбинационных блоков подключены к одним выходам соответствующих вычитателей, вторые входы вычитателей являются первыми входами блока поиска минимальной

очереди, третьи входы каждого вычитателя подключены к вторым выходам соответствующего вычитателя.

Источники информации, принятые во внимание при экспертизе

:s

Г

ч

фигЛliint uHH7

KS/ioKy1S

-A1

.

Jf nec/ie fufeuftHy

ЬахаЗ jfeHtHfny 25

Ztf

I ,« Mr

и

ДГЖ

20

Лг пваеанеге peiucmpa 1

Dm шин z ui.3

if

a

KnepSofig mmame/jto 23

К и muutCKUH злеме/fmoff S vuifiame/ia 23

n

/ft

i

/V i.

Z/

Sfn nepSow шатате/1Я f J .

Xi

С SbiKoioS злкнентв 15 SADKO Фи1.Ч

Авторы

Даты

1982-06-15—Публикация

1980-10-29—Подача