1

Изобретение относится к области вычислительной техники.

Известеи реверсивный распределитель, каждый разряд которого содержит четыре элемента И - НЕ, шину «влево и шину «вправо. Причем выход первого элемента И - НЕ соединен с входом второго элемента И - НЕ своего разряда и с входом четвертого элемента И - НЕ предыдущего разряда, выход второго элемента И - НЕ подключен К входам первого и третьего элементов И - НЕ своего разряда, выход третьего элемента И - НЕ соединен с входом второго элемента И - НЕ своего разряда и с входом четвертого элемента И - НЕ последуюш,его разряда, шина «влево соединена с входами первых элементов И - НЕ всех разрядов, шина «вправо - с входами третьих элементо|3 И - НЕ всех разрядов.

Цель изобретения - уменьшение числа инверторов и расширение логических возможностей распределителя. Для этого в .предлагаемом распределителе дополнительно выход второго элемента И - НЕ подключен к входам вторых элементов И - НЕ предыдущего и последующих разрядов, выход четвертого элемента И - НЕ соединен с входами первого и третьего элементов И - НЕ своего разряда, с входами второго, третьего и четвертого элементов И - НЕ предыдущего разряда и

с входами первого, второго и четвертого элементов И - НЕ последующего разряда, а вновь введенная шина «сдвиг соединена с входами четвертых элементов И - НЕ всех разрядов.

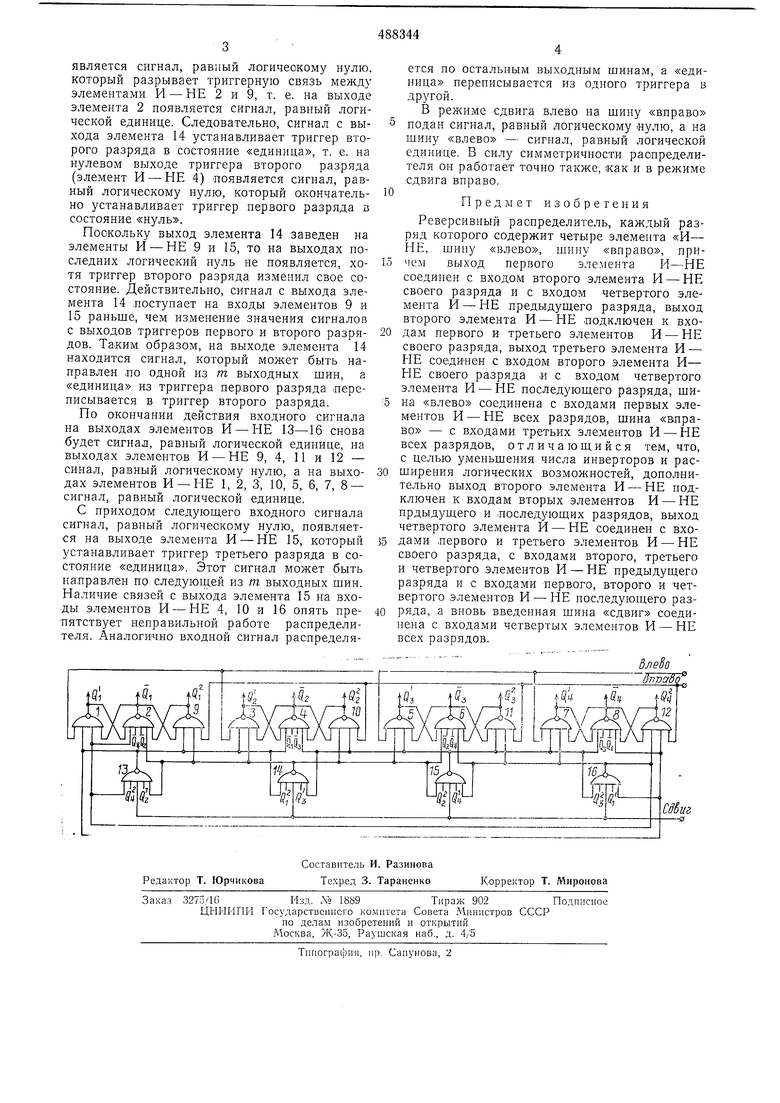

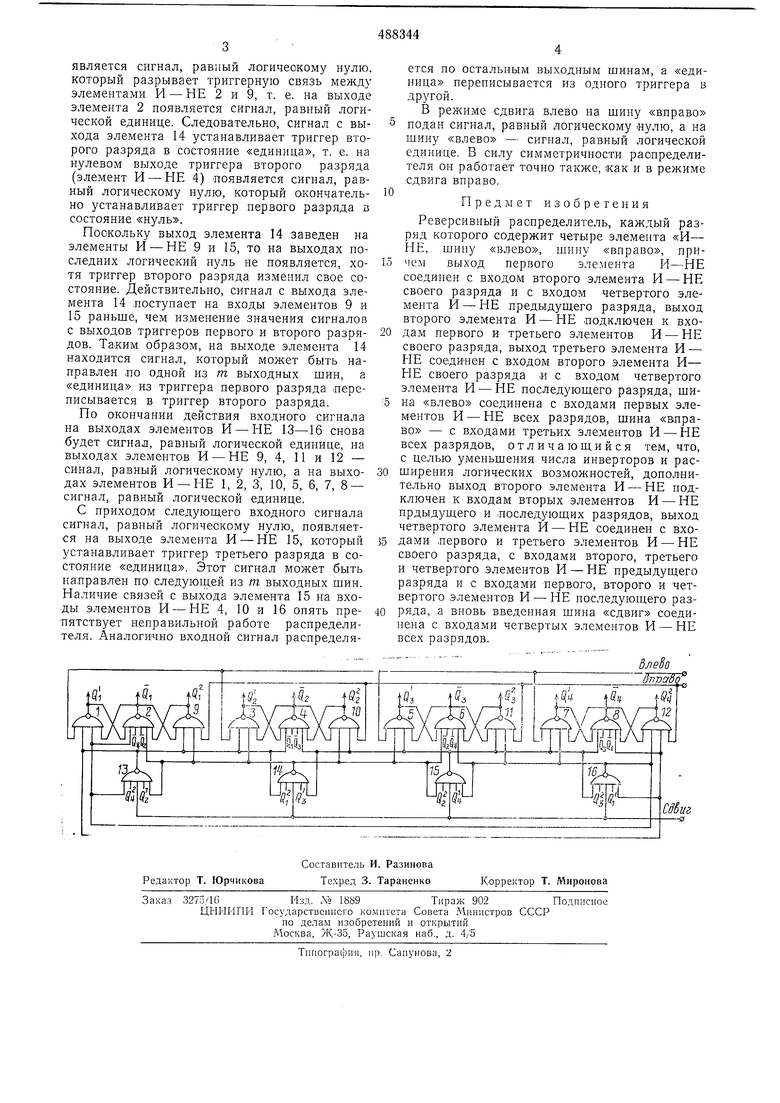

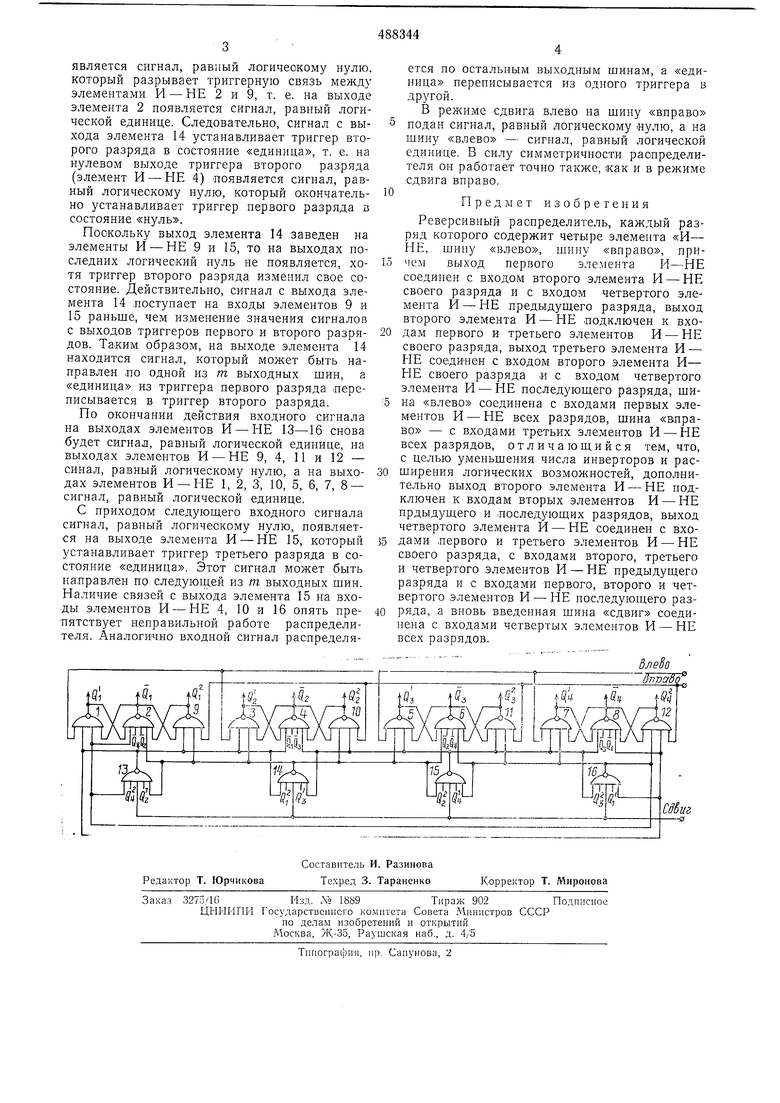

На чертеже изображена схема предлагаемого реверсивного распределителя с числом разрядов, равным четырем (число разрядов может быть любым).

Распределитель содержит элементы И - НЕ 1 и 2, 3 и 4, 5 1 6, 7 1 8, которые образуют триггеры, и элементы И - НЕ 9-12 и 13-16 соответственно первого, второго, третьего л четвертого разрядов.

Е начальный момент времени триггер первого разряда установлен в состояние «единица, остальные триггеры - в состояние «нуль.

В начале режима сдвига вправо на шину «влево подан сигнал, равный логическому нулю, а на шину «вправо - сигнал, равный логической единице. Поскольку в начальный момент времени тактирующий игнал отсутствует (равен логическому нулю), то на выходах элементов И- НЕ 1, 9,3,4, 5, 6, 7, 8, 13, 14. 15, 16 находится сигнал, равный логической единице, а на выходах элементов И - НЕ 2, 10, 11, 12 - сигнал, равный логическому нулю.

С приходом такт рующего сигнала срабатывает элемент И - НЕ 14, на его выходе по

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный распределитель сигналов | 1973 |

|

SU750564A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ СИГНАЛОВ | 1973 |

|

SU408375A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1580555A1 |

| Устройство для сопряжения | 1979 |

|

SU842772A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

Авторы

Даты

1975-10-15—Публикация

1974-03-11—Подача