(54) СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1594691A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1179538A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| Аналого-цифровой преобразователь | 1980 |

|

SU924852A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900438A2 |

I

Изобретение относится к аналого-цифровым преобразователям и может быть использовано в области связи, вычислительной и измерительной технике, а также в автоматизированных системах управлеиия технологическими процессами и системах автоматизации научных исследований.

Известен следящий аналого-цифровой преобразователь, содержащий блок сравнения, аналоговый запоминающий блок, цифроаналоговый преобразова- тель, реверсивный счетчик, первый логический блок, второй логический блок, распределитель импульсов, блок поиска поддиапазона, третий логический блок, генератор тактовых импульсов, перв, второй, третий триггеры, причем первый вход блока сравнения соединен с выходом аналогового запоминающего блока, вход которого соединен с источником входного сигнала, второй вход блока сравнения соединен с выходом дифроаналоговогЬ

преобразователя, цифровые входы которого соединены с выходами разрядов реверсивного счетчика, выход блока сравнения соединен с первым входом первого логического блока, второй вход которого соединен с единичным выходом триггера переполнения реверсивного счетчика, выходы разрядов реверсивного счетчика соединены с первой группой входов второго логи10ческого блока 6, вторая группа входов которой соединена с выходами соответствуюв их разрядов распределителя импульсов, первая группа выходов второго логического блока соединена

IS со счетными входами соответствукицих разрядов реверсивного счетчика, первый выход первого логического блока соединен с третьим входом блока поиска поддиапазона и со вторым входом

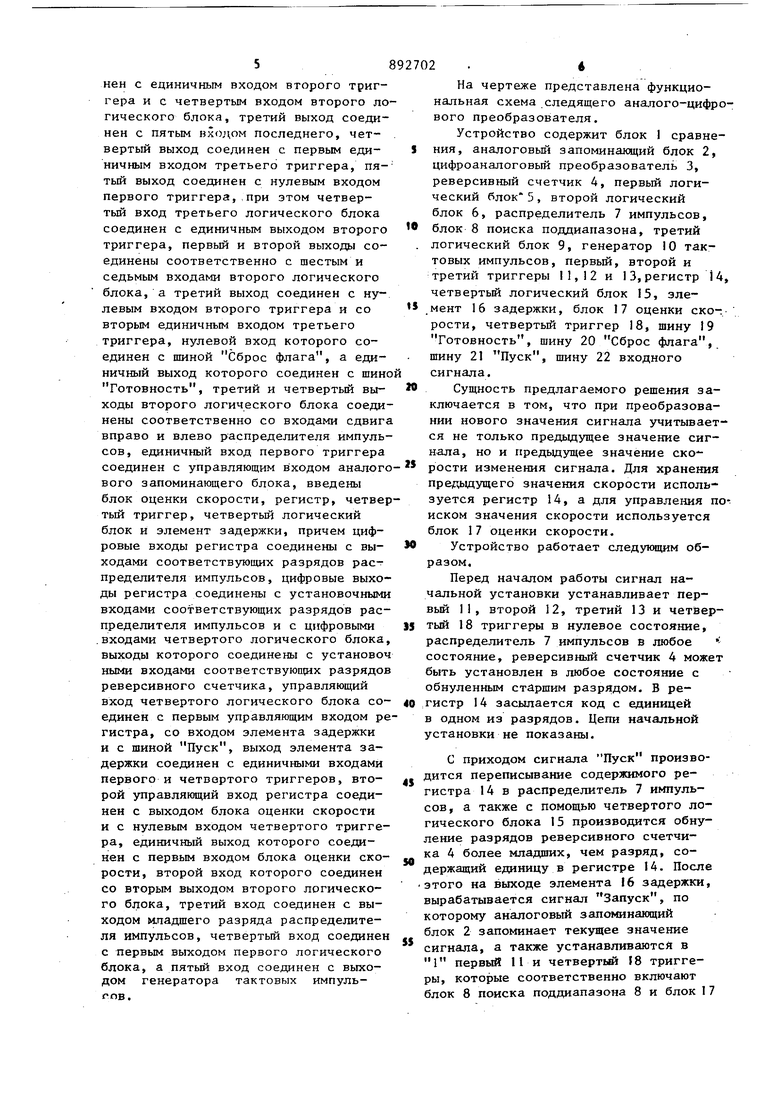

20 третьего логического блока, второй и третий выходы первого логического блока соединены со входами установки Iрежима реверсивного счетчика, пер38вый вход блока поиска поддиапазона соединен с первым входом третьего логического блока и с единичным выходом последнего (младшего) разряда распределителя импульсов, второй вход соединен с первым выходом второго логического блока, четвертый вход соединен с третьим входом третьего логического блока и с выходом генератора тактовых импульсов, пятый вход соединен с единичным выходом первого триггера, первый выход соединен со вторым входом второго логического 5лока, второй выход соединен с единич ным входом второго триггера и с первьм входом второго логического блока, третий выход соединен с четвертым входом второго логического блока,чет, вертьй выход соединен с единичным входом третьего триггера, пятый вы- ход соединён с нулевым входом первого триггера, четвертый вход третьего логи-, :ческого блока соединен с единичным выходом второго триггера, первый и второй выходы третьего логического блока coef3fi иены соответственно с третьим и пятым входами второго логического блока, а третий выход третьего логического бло ка соединен с нулевым входом второго триггера и с единичным входом третьего триггера, нулевой вход которого соединен с шиной Сброс флага, а еди ничный выход которого соединен с шиной Готовность, второй и третий выходы второго логического блока соединены соответственно со входами сдвига вправо и влево распределителя импульсов, единичный вход первого триггера соединен с управляющим входом аналогового запоминающего блока и с шиной Запуск.. Сущность работы известного устройства заключается в том, что новое пре образование учитывает предыдущее значение сигнала и начиная от него ищется новое значение сигнала. При этом вначале определяется поддиапазон расположения сигнала, а затем поразрядным методом определяется точное значение сигнала ij. Недостатком известного устройства является большое время преобразования обусловленное тем. Что поиск поддиапазона всегда начинается с минимального шага квантования равного кванту, т.е. не учитывается скорость изменения входного сигнала. Так, например, если скорость сигнала веля2ка, то поиск его в прежнем кванте Приводит к бесполезной потере времени. Скорость изменения сигнала должна учитываться при выборе начального шага квантования при поиске поддиапазона. Очевидно, что уменьшить время преобразования можно, если учитывать при преобразовании нового значения сигнала не только предыдущее значение сигнала, но и предыдущее значение скорости изменения сигнала. Цель изобретения - уменьшение времени преобразования. Поставленная цель достигается тем, что в следящий аналого-цифровой преобразователь, содержащий блок сравнения, первый вход которого соединен с выходом аналогового запоминающего блока, вход которого соединен с источником входного сигнала, второй вход блока сравнения соединен с выходом цифроаналогового преобразователя, цифровые входы которого соединены с выходами разрядов реверсивного счетчика, выход блока сравнения соединен с первым входом первого логического блока, второй вход которого соединен с единичным выходом триггера переполнения реверсивного счет- чика, выходы разрядов реверсивного счетчика соединены с первой группой входов второго логического блока, вторая группа входов которого соединена с выходами соответствующих разрядов распределителя импульсов, а первая группа выходов соединена со счетными входами соответствующих разрядов реверсивного счетчика, первый выход первого логического блока соединен с первым входом блока поиска поддиапазона и с первым входом третьего логического блока, второй и третий выходы первбго логического блока соединены со входами установки режима реверсивного счетчика, второй вход блока поиска поддиапазона соединен со вторым входом третьего логического блока и с единичным выходом младшего разряда распределителя импульсов, третий вход соединен со вторым выходом второго логического блока, четвертый вход соединен с третьим входом третьего логического блока и с выходом генератора тактовых импульсов, пятый вход соединен с единичным выходом первого триггера, первый выход соединен с третьим входом второго логического блока, второй выход соедчнен с единичным входом второго триггера и с четвертым входом второго ло гического блока, третий выход соединен с пятым входом последнего, четвертый выход соединен с первым единичным входом третьего триггера, пятый выход соединен с нулевым входом первого триггера, при этом четвертый вход третьего логического блока соединен с единичным выходом второго триггера, первый и второй выходы соединены соответственно с шестым и седьмым входами второго логического блока, а третий выход соединен с нулевым входом второго триггера и со вторым единичным входом третьего триггера, нулевой вход которого соединен с шиной Сброс флага, а единичный выход которого соединен с шин Готовность, третий и четвертый выходы второго логического блока соеди нены соответственно со входами сдвиг вправо и влево распределителя импуль сов, единичный вход первого триггера соединен с управляющим входом аналог вого запоминающего блока, введены блок оценки скорости, регистр, четве тый триггер, четвертый логический блок и элемент задержки, причем цифровые входы регистра соединены с выходами соответствующих разрядов распределителя импульсов, цифровые выходы регистра соединены с установочными входами соответствующих разрядов распределителя импульсов и с цифровыми .входами четвертого логического блока выходы которого соединены с установоч ными входами соответствующих разрядов реверсивного счетчика, управляющий вход четвертого логического блока соединен с первым управляющим входом ре гистра, со входом элемента задержки и с шиной Пуск, выход элемента задержки соединен с единичными входами первого и четвертого триггеров, второй управляющий вход регистра соединен с выходом блока оценки скорости и с нулевым входом четвертого триггера, единичный выход которого соединен с первым входом блока оценки скорости, второй вход которого соединен со вторым выходом второго логического блока, третий вход соединен с выходом мпадшего разряда распределителя импульсов, четвертый вход соединен с первым выходом первого логического блока, а пятый вход соединен с выходом генератора тактовых импуль« пв. 2 .« На чертеже представлена функциональная схема следящего анаггого-цифрового преобразователя. Устройство содержит блок 1 сравнения, аналоговьп запоминающий блок 2, цифроаналоговый преобразователь 3, реверсивный счетчик 4, первый логический блок 5, второй логический блок 6, распределитель 7 импульсов, блок 8 поиска поддиапазона, третий логический блок 9, генератор 10 тактовых импульсов, первый, второй и третий триггеры 11,12 и 13,регистр 14, четвертый логический блок 15, эле.мент 16 задержки, блок 17 оценки ско-.. рости, четвертьй триггер 18, шину 19 Готовность, шину 20 Сброс флага, шину 21 Пуск, шину 22 входного сигнала. Сущность предлагаемого решения заключается в том, что при преобразовании нового значения сигнала учитьгоается не только предыдущее значение сигнала, но и предыдущее значение ско-рости изменения сигнала. Для хранения предыдущего значения скорости используется регистр 14, а для управления по иском значения скорости используется блок 17 оценки скорости. Устройство работает следуюпщм образом. Перед началом работы сигнал начальной установки устанавливает первый 11, второй 12, третий 13 и четвертый 18 триггеры в нулевое состояние, распределитель 7 импульсов в любое состояние, реверсивный счетчик 4 может быть установлен в любое состояние с обнуленным старшим разрядом. В регистр 14 засылается код с единицей в одном из разрядов. Цепи начальной установки не показаны. с приходом сигнала Пуск производится переписывание содержимого регистра 14 в распределитель 7 импульсов, а также с помощью четвертого логического блока I5 производится обнуление разрядов реверсивного счетчика 4 более младших, чем разряд, содержащий единицу в регистре 14. После ЭТОГО на выходе элемента 16 задержки, вырабатывается сигнал Запуск, по которому аналоговый запоминающий блок 2 запоминает текущее значение сигнала, а также устанавливаются в 1 первый Пи четвертый J8 триггеры, которые соответственно включают блок 8 поиска поддиапазона 8 и блок 1 7 /8 оценки скорости. После того как будет оценена скорость .входного сигнала по сигналу на выходе блока оцен-. ки скорости содержимое распределителя 7 импульсов переписывается в регистр 14, сбрасывается в О четвертый триггер 18, прекращая работу блока 17 оценки скорости. Работа предлагаемого устройства по определению значения сигнала совпа дает с работой известного за исключением того факта, что поиск поддиапазо на начинается не с ьшнимального шага квантования (как в известном), ас: промежуточного шага квантования, величина которого определяется скоростью входного сигнала и хранится в регистре 14. Формула изобретения Следящий аналого-цифровой преобразователь содержит блок сравнения, первый вход которого соединен с выходом аналогового запоминающего блока, вход которого соединен с источником входного сигнала, второй вход блока сравнения соединен с выходом цифроаналогового преобразователя, цифровые входы которого соединены с выход ми разрядов реверсивного счетчика, выход блока сравнения соединен с пер в№1 входом Первого логического блока второй вход которого соединен с единичным выходом триггера переполнения реверсивного счетчика, выходы разрядов реверсивного счетчика соединены с первой группой входов второго логического блока, вторая группа входо которого соединена с выходами соответствующих разрядов распределителя импульсов, а первая группа выходо соединена со счетными входами соотве ствующих разрядов реверсивного- счетчика, первый выход первого логическо го блока соединен с первым входом бл ка поиска поддиапазона и с первым вх дом третьего логического блока, второй и третий выхода первого логического блока соединены со входами уста новки режима реверсивного счетчика, второй вход блока поиска поддиапазона соединен со вторым входом третьего логического блока и с единичным .выходом младшего разряда распределителя импульсов, третий вход соединен сО вторым выходом второго логического блока, четвертый вход соединен с третьим входом третьего логического блока и с выходом генератора тактовых импульсов, пятый вход соединен с единичным выходом первого триггера, j первый выход соединен с третьим входом второго логического блока, второй выход соединен с единичным входом второго триггера и с четвертым входом второго логического блока, третий выход соединен с пятым входом последнего, четвертый выход соединен с пер- вым единичным входом третьего триггера, пятый выход соединен с нулевыми входом первого триггера, при зтом четвертый вход третьего логического блока соединен с единичным выходом второго триггера, первый и второй выходы соединены соответственно с шестым и седьмым входами второго логического блока, а третий выход соединен с нулевым входом второго триггера и со вторым единичным входом третьего триггера, нулевой вход которого соединен с шиной Сброс флага, а единичный выход которого соединен с шиной Готовность, третий и четвертый выходы второго логического блока соединены соответственно со входами сдвига вправо и влево распределителя импульсов, единичный вход первого триггера соединен с управляющим входом аналогового запоминающего блока, отличающийся тем, что, с целью уменьшения времени преобразования, введены блок оценки скорости, регистр, четвертый триггер, четвертый логический блок и элемент задержки, причем цифровые входы регистра соединены с выходами соответствующих разрядов распределителя импульсов, цифровые выходы регистра соединены с установочными входами соответствующих разрядов распределителя импульсов и с. 1щфровыми входами четвертого логического блока, выходы которого соединены с установочными входами соответствующих разрядов реверсивного счетчика, управляющий вход четвертого/логического блока соединен с первым управляющим входом регистра, со входом элемента задержки и с шиной Пуск, выход элемента задержки соединен с единичными входами первого и четвертого триггеров, второй управляющий вход регистра соединен с выходом блока оценки скорости и с нулевым входом четвертого триггера, единичный выход которого соединен с первым входом блока оценки скорости, второй вход которого соединен со вт рым выходом второго логического бло ка, третий вход соединен с выходом младшего разряда распределителя импульсов, четвертый вход соединен с первым выходом первого логического JO блока, а пятый вход соединен с выходом генератора тактовых импульсов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2745134/21, кл. Н 03 К 13/02, 12.04.79.

Вымднои яо

Авторы

Даты

1981-12-23—Публикация

1980-04-08—Подача