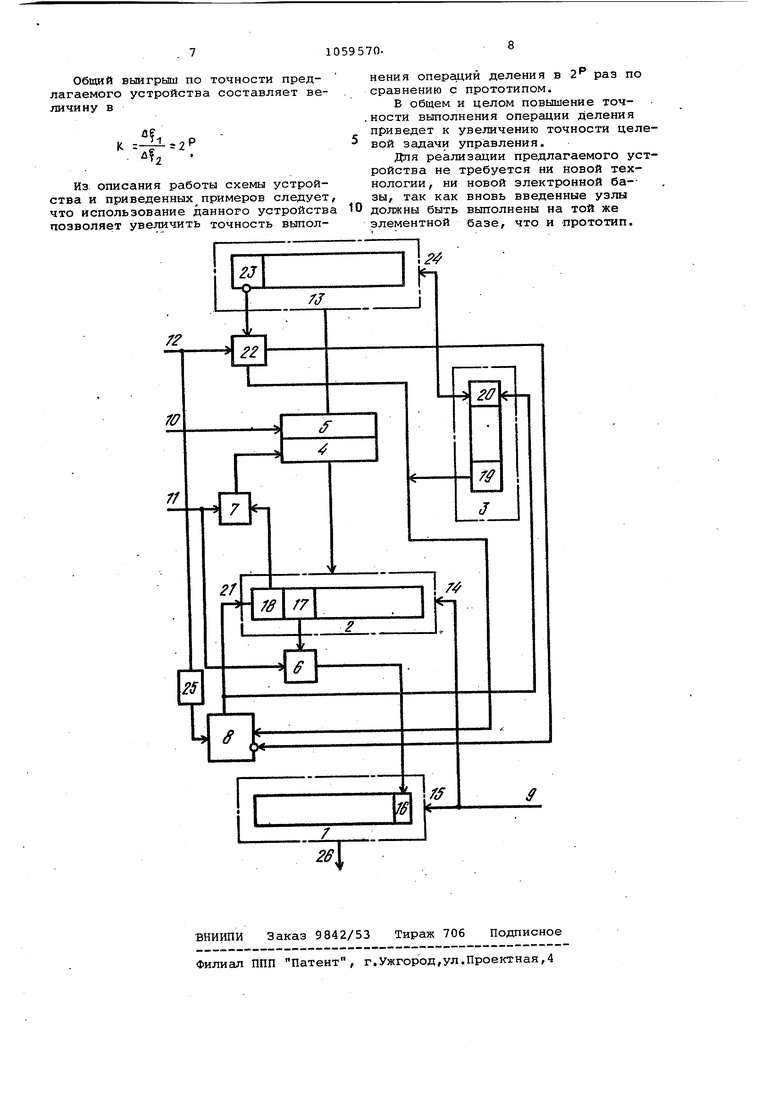

Изобретение относится к вычислительной технике и может найти применение при создании специализированных систем переработки цифровой информации. Известны устройства деления с во становлением остатка, содержащие регистры делителя, частного, сумматор, элементы управления Cl-If Недостаток указанных устройств состоит в том, что они не обладают возможностью производить деление с автоматическим изменением масшта ба делимого, что уменьшает точност вычислений. Наиболее близким к .предлагаемом является устройство для деления чисел с фиксированной запятой с восстановлением остатка, содержащее регистры делителя, частного, сумматор, группы элемента И для пе редачи прямого и инверсного кЬдов делителя, два элемента И, три шины тактовых сигналов С23. При делении чисел с фиксированной запятой для исключения перепол нения разрядной сетки вводится масштабный множитель 2- (Л где X - делимое,У - делитель, Z частное. К - масштабный множитель. Учитывая, что масштабный множитель представлен в виде , алго ритм реализации формулы (1) будет следующий. Реализуется правый сдвиг делимо го X на заданный целочисленный арг мент г . Реализуется деление Реализация формулы (1) приводит к значительной инструментальной по грешности, так как при ограниченно длине разрядной сетки правый сдвиг делимого тождественен усечению е.го на младших разрядов. Цель изобретения - повышение точности вычислений путем уменьшен числа правых.сдвигов делимого. ПоставленнаяЦель достигается тем, что в устройство для деления чисел с фиксированной запятой, содержащее сумматор, сдвиговый регис частного, две группы элементов И, два элемента И, сдвиговый регистр делителя, прямые и обратные выходы которого соединены соответственно с первыми входами элементов И первой и второй групп, выходы которых соединены соответственно с входами сумматора, вход сдвига влево которого подключен к шине первого так вого сигнала и к входу сдвига влево сдвигового регистра частного, вход младшего разряда которого соединен с выходом первого элемента И, первый вход которого подключен к инверсному выходу знакового разряда сумматора, выход знакового разряда которого подключен к первому входу второго элемента И, выход которого подключен к вторым объединенным входам элементов И первой группы, вторая шина тактовых сигналов подключена к вторым объединенным: входам элементов И второй группы, третья шина тактовых сигналов соедлнена с вторыми входами первого и второго элементов И, дополнительно введены третий и четвертый элементы И, сумматор аргумента, элемент задержки, причем первый вход третьего элемента И подключен к выходу знакового разряда су «1матора аргумента и к первому входу четвертого элемента И, второй вход которого соединен с четвертой шиной тактовых сигналов и входом элемента задержки, выход которой соединен с вторым входом третьего элемента И, выход .которого соединен с . входом сдвига вправо сумматора и с первым входом младшего разряда cjTviMaTopa аргумента, второй вход которого соединен с третьим инверсным входом четвертого элемента И, управляющим входом сдвига влево сдвигового регистра делителя и вы- ходом третьего элемента И, третий вход которого соединен с инверсным выходом старшего разряда сдвигового регистра делителя. На чертеже приведена структурная схема устройства. Устройство содержит регистр 1 частного, сумматор 2, сумматор 3 аргумента, группы элементов И прямого 4 и инверсного 5 кода, три элеMeHfa И 6 - 8, четыре шины тактог вых сигналов 9 - 12, регистр 13 делителя, информационные выходы которого через группы элементов И прямого 4, инверсного 5 кода соединены с информационными входами сумматора 2, вход 14 сдвига влево которого подключен к шине первого тактового сигнала 9 и входу 15 сдвига влево регистра частного 1, младший разряд 16 которого через первый элемент И б подключен к инверсному выходу 17 знакового разряда сумматора 2, прямой выход 18 которого через второй элемент И 7 подключен к управляющему входу группы элементов И прямого кода 4, вторая шина тактовых сигналов 10 подключена к управляющему входу группы элементов И инверсного кода 5, третья шина тактовых сигналов 11 соединена с входом перво о и второго элементов И б, 7, управляющий вход третьего элемента И 8 подключен к знаковому разряду 19 сумматора аргумента 3 , а его выход - к первому входу 20 младшего разряда сумматора аргумента 3 и входу сдвига вправо 21 сумматора 2

Устройство дополнительно снабжено элементом И 22, вход которого соединен с четвертой шиной тактовых сигналов 12, первый управляющий вход дополнительного элемента И 22 соединен с инверсным выходом старшего разряда 23 регистра 13 делителя, второй управляющий вход соединен со знаковым разрядом 19 сумматора 3 аргумента, а выход со вторым входом младшего разряда 20 сумматора 3 аргумента, с входом 24 сдвига влево регистра 13 делителя, и инверсным входом третьего элемента И 8, вход которого через линию 25 задержки соединен с четвертой шиной тактовых сигналов 12, информационный выход 26 регистра 1 частного является выходом устройства.

Устройство работает следующим образом.

Умножая числитель и знаменатель выражения (1) на число, равное 2, можно записать

X2-V

(21 42

Тогда алгоритм реализации формулы (2) будет следующий.

1.Доводится анализ значения аргумента - г и проверяется возможность первого сдвига делителя на

1 разряд влево. .

Г|зи этом, если при предполагаемом сдвиге делителя не фиксирует ся переполнение и значение аргумента - г не равно нулю, то осуществляется левый сдвиг делителя на 1 разряд, а к аргументу - г прибавляется единица. Далее повторяется выполнение первого пункта до тех пор, пока или значение аргумента - г станет равным нулю, или будет зафиксирована невозможность левого сдвига делителя, сть число повторений пункта, равно Р.

2.Осуществляется сдвиг делимого на fr-р разрядов вправо.

3.Реализуется деление сдвинутого ;вправо на -р разрядов делимого на сдвинутый влево на Р разрядов делитель У 2 .

Устройство работает следующим образом.

Для реализации деленияделимое X направляется в сумматор- 2,геделитель Y - в регистр 13 делителя, а аргумент г масштабного множителя в сумматор 3 аргумента. Г)и ч ем аргумент - представлен в дополнительном коде. Так, для машины с 32-разрядной сеткой аргумент масштабного множителя равен 5 и будет записан в виде: прямой код - 0,0101, дополнительный код 1.1011.

ifo сигналам с шины тактовых сигналов 12 на вькоде элемента И 22 возникает единичный сигнал в том случае, если на его первый вход поступает единичный сигнал с инверс ного выхода старшего разряда 23 регистра 13 делителя и на второй.вход поступает единичный сигнал с выхода знакового разряда 19 сумматора 3 аргумента, на выходе элемента И 8

5 возникает единичный сигнал в случае, если на его вход поступает единичный сигнал с выхода знакового разряда 19 сумматора 3 аргумента, а на инверсный вход с выхода элемен0 та И 22 поступает нулевой сигнал. Единичный сигнал -с выхода элемента И 22 поступает на вход 24 сдвига влево регистра 13 делителя, на второй вход младшего разряда 20 сумма5 тора 3 аргумента и на инверсный вход элемента ИЗ, Пэ этому сигналу осуществляется сдвиг влево на 1 разряд содержимого регистра 13 делителя, прибавление единицы к соQ держимому сумматора 3 аргумента и запрет возникновения единичного сигнала на выходе элемента И 8.

Таким образом, по сигналам с шины тактовых сигналов 12 производится

5 сдвиг влево содержимого регистра

13 делителя до тех пор, пока в старшем разряде 23 регистра 13 делителя не окажется единицы или в знаковом разряде 19 сумматора 3 аргумен0 та не окажется ноль. Если старший разряд делителя стал равен единице, а сумматор 3 аргумента еще не обнулился, то на выходе элемента И 22 будет нулевой сигнал, который сов5 местно с единичным сигналом знакового разряда сумматора аргумента 3 по. приходу, тактового импульса с шины 12 будут вызывать срабатывание элемента И 8, на выходе которого будет вырабатываться единичный сигнал. Единичный сигнал с выхода элемента И 8 поступает на вход сдвига вправо 21 сумматора 2 и на первый вход младшего разряда 2.0 сумматора 3 аргумента. ГЬ этому сигналу осуществляется сдвиг вправо на 1 разряд сумматора 2 и прибавление единицы к содержимому сумматора 3 аргумента. Сдвиг вправо содержимого сумматора 2 будет длит.ься до тех

0 пор, пока не обнулится знаковый разряд 19 сумматора 3 аргумента. Схема задержки 25 служит для исключения момента срабатывания элемента И 8 раньше появления сигнала на выходе

5 элемента И 22 и имеет время задержки, равное времени прохождения сигнала через элемент И 22, , Пусть -необходимо реализовать при мер 2 0.0001-1 . О, 000011... тогда в регистре 13 де.лителя будет находиться код 0.000011..., в сумматоре 2 код 0.00011, ав сумматоре аргумента 1.1011. В этом случае по первому сигналу с шины тактовых сигналов 12 на выходе элемента И 22 возникает единичный сигнал, так как на его. первый и второй управляющие входы поступают единичные сигналы соответственно с инверсного выхода старшего эазряда 23 и знакового разряда 19 сумматора 3 аргумента, так как в старшем разряде 23 регистра 13 де .лителя содержится ноль, а в знаковом разряде19 сумматора 3 аргумент единица. . По единичному сигналу с выхода элемента И 22 производится сдвиг влево на 1 разряд содержимого регистра 13 делителя, прибавление еди ницы к содержимому сумматора 3 аргумента и осуществляется запрет прохождения сигнала с шины тактовых сигналов 12 через элемент И 8. Таким образом, после поступления первого сигнала с шины тактовых сиг налов 12 на регистре 13 делителя будет-находиться код равный 0,00011.., в сумматоре 3 аргумента будет находиться код 1.1100, после прохождения второго сигнала с шины тактовых сигналов 12 на регистре 13 делителя будет код, равный 0.0011. в сумматоре аргумента 1.1101, пос.пе прохождения третьего и четвертого сигнала соответственно 0.11..: и 1.1111. Ши прохождении пятого сигнала на выходе элемента .И 22 единичный сигнал не возникает, так как старший разряд 23 регистра 13 делктеля стал равен единице, а на его инверсном выходе ПОЯВИ.ЛСЯ нулевой си нал. В этом случае возникает единичный сигнал на выходе элемента И 8, так как на его управляющий вход с выхода знакового разряда сумматора 3 аргумента поступает единичный си нал, а на инверсный вход с выхода элемента И 22 поступает нулевой сигнал. Ш этому сигналу осуществляется сдвиг на 1 разряд содержимого сумматора 2 вправо и прибавле единицы в младший разряд 20 сумматора 3 аргумента. В результате это го в сумматоре 2 окажется код, рав ный 0.00001.1..., а в сумматоре 3 аргумента - код 0,0000, Так как в знаковом разряде 19 сумматора 3 аргумента теперь находится код нуля, то на выходе элементов И 22 и И 8 единичные сигналы при прохождении последующих сигналов с шины тактовых сигналов 12 будут отсутствова.ть, Щзи обнулении сумматора аргумента 3 начинается непосредственно процесс деления. Для определения п цифр частного выполняется п одинаковых циклов. В первом такте (тактовая шина 9 ) каждого цикла содержимое сумматора 2 и регистра 1 частного сдвигается на 1 разряд влево, во втором такте (тактовая шина 10 ) из кода на сумматоре 2 вЕЛчитается де.литель (содержимое регистра делителя -13), для чего в сумматор 2 передается инверсный код делителя, а в младший разряд единица. В третьем такте (тактовая цшна 11) в случае, если в знаковом разряде сумматора 2 окажется нуль, то в младший разряд 16 регистра 1 часгного записывается единица. ЕС.ПИ в знаковом разряде сумматора 2 будет единица, то в младший разряд 16 регистра 1 частного записи не производится и в нем сохранится нуль. В этом случае производится восстановление остатка в сумматоре 2, для чего в сумматор 2 передается содержимое регистра 13 делителя прямым кодом. В результате сдвига влево регистра 1 частного в первом такте каждого цикла деления отдельные цифры регистра 1 частного, всегда направляемые в младший разряд 16, постепенно заполняют весь регистр. В общем виде для максимальных оценок, когда то( ,2-n 111017. - -min среднеквадратичная ошибка деления по известному алгоритму 2 равна ) Среднеквадратичная ошибка деления по алгоритму предлагаемого устройства значительно меньше и может быть определена по выражению ( 2- -- , Еде Р - число левых сдвигов де.лителя. Это объясняется тем, что в предлагаемом устройстве у де.лимого .при правом сдвиге отсекается г-р младших разрядов, а у прототипа г разрядов .

Общий вьмгрыш по точности предлагаемого устройства составляет величину в

as к -li.jp

- .е- - . .

Из. описания работы схемы устройства и приведенных примеров следует, что использование данного устройства позволяет увеличить точность выполнения операций деления в 2 раз по сравнению с прототипом.

В общем и целом повышение точ.ности выполнения операции деления приведет к увеличению точности целевой задачи управления.

Для реализации предлагаемого устройства не требуется ни новой технологии, ни новой электронной ба-зы, так как вновь введенные узлы должны быть выполнены на той же элементной базе, что и -прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1388853A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления чисел с восстановлением остатка | 1972 |

|

SU485447A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1283753A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ С ФИКСИРОВАННОЙ ЗАПЯТОЙ, содер-жащее сумматор, .сдвиговый регистр частного, две группы элементов И, два элемента И, сдвиговый регистр делителя, прямые и обратные выходы которого соединены соответственно с первыми входами элементов и первой и второй групп, ЕЫХОДЬ которых соединены соответственно с входами сулшатора, вход сдвига влево которого подключен к шине первого тактового сигнала и к входу сдвига влево сдвигового регистра частного, вход младшего разряда которого соединен с выходом первого элемента И, первый вход которого подключен к инверсному выходу знакового разряда сумматора, прямой выход знакового разряда которого подключен к первому входу второго элемен1а И, выход которого подключен к вторым объединенным входам элементов И первой группы, вторая шина тактовых сиг налов подключена к вторым объединенным входам элементов И второй группы, третья шина тактовых сигналов соединена с вторыми входами первого и второго элементов И, о т личающееся тем, что, с целью увеличения точности вычислений, в него введены третий и четвертый элементы И, сумматор аргумента, элемент задержки, причем первый вход третьего элемента И подС $5 ключен к выходу знакового разряда су№.1атора аргумента и- к первому вхо(Л ду четвертого элемента И, второй вход которого соединен с четвертой шиной тактовых сигналов и входом элемента задержки, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с входом сдвига бправо сумматора и с первым входом младшего разряда, сумматора аргумента, второй ел вход которого соединен с третьим со инверсным входом четвертого элемента И, входом сдвига влево сдвигоСП вого регистра делителя и выходом третьего элемента И, третий вход которого соединен с инверснЕлм выходом старшего разряда сдвигового регистра делителя.

| I, Папернов А.А | |||

| Логические основы цифровой вычислительной техники | |||

| М., Советское радио, 1972, с | |||

| Приспособление для нагрузки тендеров дровами | 1920 |

|

SU228A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Соренков Э.И., Телега А.И., Шамаков А.С | |||

| Точность вычислительных устройств и алгоритмов | |||

| М. | |||

| , Машиностроение, 1976, с | |||

| Раздвижной паровозный золотник с подвижными по его скалке поршнями между упорными шайбами | 1922 |

|

SU148A1 |

Авторы

Даты

1983-12-07—Публикация

1982-04-27—Подача