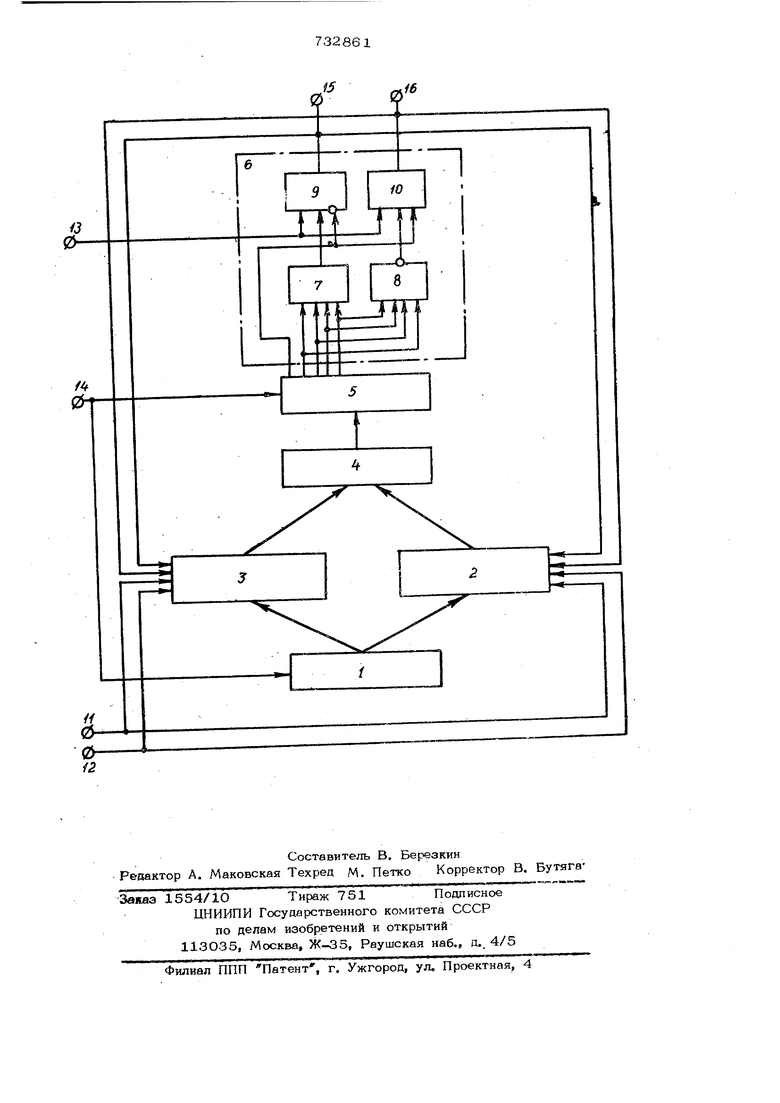

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах. Известны устройства для вычисления обратной величины, построенные на основе универсальных цифровых вычислительных машин l, 2 и 3. . Обратная величина в таких устройствах вычисляется программными методами Однако такое вычисление специализированных вычислительных устройствах явля ется нерациональным, так как связано с большими аппарйтурными затратами и, кроме того, требует значительного времени, так как необходимы многократные обращения к памяти. Наиболее близким к предлагаемому яв ляется устройство для вычисления обратной величины, в состав которого входят входной и выходной регистры (сумматоры), блок выделения начального приближения, множительный блок, цифровой ком паратор, коммутатор прямого и обратного кодов, блок фиксирования заданной точности приближений и блок контроля верных разрядов в очередном приближении обратной величины. Вычисление обратной величины в этом устройстве производится по . итерационной формуле. - При этом выделяется начальное приближение и производится некоторое число итераций, которое зависит от требуемой точности вычислений Однако такое устройство имеет невысокое быстродействие при работе в свстемах управления процессами в реальном масштабе времени. Цель изобретения - повышение быст родействия. Указанная цель достигается тем, что устройство для вычисления обратной величины, в которое входят два сумматора, содержит третий сумматор, регистр, блок элементов ИЛИ и блок анализа разрядов, причем выходы первого и второго сумматоров соединены с первой в второй группами входов блока элементов ИЛИ соотэлементов ШТРТ ветственно, выходы блока подключены ко входам третьего сумматора, выходы регистра подключены к информационным входам первого и второго сум маторов, первый и второй управляющие входы которых подключены к первому и второму информационным входам устрой™ ства соответственно, а третий и четвертый управляющие входы - к первому и второму выходам устройства соответственно, первый управляющий вход устройст ва подключен к управляющему входу блока анализа разрядов, выходы которого по ключены к выходам устройства, а знаковый и информационные входы - к знаково му и информационным выходам третьего сумматора соответственно, второй управляющий вход устройства подключен к управляющим входам регистра и третьего сумматора, Кроме того, для достижения постав-ленной цели блок анализа разрядов содержит элементы И, ИЛИ, И-НЕ и запрета, причем информационные входы блока анализа разрядов подключены ко входам элемента ИЛИ и элемента И-НЕ, выходы кот рых подключены к первым входам элемен тов запрета и И соответственно, вторые входы которых соединены с управляющим входом блока анализа разрядов, знаковый вход которого подключен к управляющему входу элемента запрета и третьему входу элемента И, выходы которых подключены соответственно к первому и второму выходам блока анализа разрядов. На чертеже представлена функциональная схема устройства, Устройство содержит регистр 1, сумматоры 2 и 3, блок 4 элементов ИЛИ, сумматор 5, блок 6 анализа разрядов. Выходы регистра 1 подключены ко вхо дам сумматоров 2 и 3. Сумматоры 2 и 3 содержат h информационных разрядов (h - разрядность представления операнда и результата) и один знаковый. Выходы сумматоров 2 и 3 подключены ко входам блока 4 элементов ИЛИ, причем знаковые разряды подключены ко входам двух первых элементов ИЛИ блока 4 элементов ИЛИ ;а каждый i -ый информационный разряд сумматоров 2 и 3 соединен со входом (i+l)-го элемента ИЛИ блока 4 элементов ИЛИ. Выходы блока 4 элементов ИДИ подключены ко входам сумматора 5, содержащего ( 1+ 3) разрядов, из которых один знаковый, а два предназначены для хранения целой части. Блок,6 анализа разрядов сод&ржит элементы ИЛИ 7 1 7, И-НЕ 8, запрета 9 и элемент И 10. Выходы четырех старших разрядов сумматора 5, начиная со второго, подключены ко входам элемента 7 и элемента 8, выходы KOTopibix соединены соответственно со входами элемента 9 и 1О, Вькод первого (знакового) разряда сумматора 5 соединен с управляющим входом элемента 9 и со входом элемента 10. Устройство содержит также информационные входы 11 и 12j управляющие входы 13 и 14и выходы 15 и 16. Информационный вход 11 устройства соединен с управляющим входом приема прямого кода сумматора 2 и с управляющим входом выдачи дополнительного кода сумматора 3. Информационный вход 12 устройства подключен к управляющему входу приема дополнительного кода сумматора 2 и к управляющему входу выдачи прямого кода cjTviMaTopa 3. Управляющий вход 13 устройства подключен к управляющему входу блока 6 анализа . разрядов, который соединен со входами элемента запрета 9 и элемента И 1О, Управляющий вход 14 устройства соединен с управляющими входами сдвига регистра 1 и сумматора 5. Выход 15устройства подключен к первому выходу блока 6 анализа разрядов и соединен с управляющими входами выдачи дополнггтельного кода сумматора 2 и приёма прямого кода сумматора 3, Выход 16 устройства подключен ко второму вьисоду блока 6 анализа разрядов к соединен с управляющими входами выдачи прямого кода сумматора 2 и приема дополнительного кода сумматора 3. Первый и второй выходы блока анализа соединены с выходами элемента 9 запрета и элемента И 10 соответственно. В качестве сумматоров 2, 3 и 5 исользуются накапливающие сумматоры. Суммирование в сумк- аторе 5 производитя с задержкой. При сдвиге в сумматоре 5 содержимое третьего разряда (второго разряда целой части) записывается в первый и второй разряд1з1, В остальном сдвиг роизводится как обычно. Прием и выдау дополнительного кода в с мматорах 2 и 3 можно осуществлять приемом (выдаей) обратного кода с добавлением единиы в младший разряд, Для представлени5 операнда X и результата Y-4- применяется избыточная симметричная двоичная система с цифрами , 1,

Устройство работает в соответствии следующим алгоритмом

-ч

л,если N.-2 0,ecNM-2 N.2

&. Vf 1

1

-2.

1,если I

-YH., 23. .у.,

очередная цифра операнда

где

( т,ои);

содержимое сумматора 2 в i - цикле вычислений;

очередная цифра результата; Х - Содержимое сумматора 3 в i цикле вычислений; содержимое сумматора 5 к на 1-1чалу i -го цикла вычислений N; - содержимое сумматора 5 в

i -м цикле.

Исходное состояние Кр 2 | X -Yo-O На величину аргумента накладываются ограничения 2 ( 1,

В начальном состоянии в старшем разряде регистра 1 записана единица, в остальных разрядах - нули.

Обратная величина исходного операнда вычисляется в (Н + З) циклах, каждый из которых состоит из трех тактов. В первом такте каждого i -го цикла на входы устройства поступает очередной разряд операнда (операнд поступает,начиная со старших разрядов). При этом, если единичный сигнал поступает на информационный вход 11 устройства, это свидетельствует о том, что очередной разряд операнда численно равен 1. Если единичный сигнал поступает на 1шформационный вход 12, очередной разряд операнда численно равен Т . Если же единичный разряд не поступает ни на один из входов 11 и 12 очередной разряд операнда численно равен О. В зависимости от сигнала, поступившего на входы 11 и 12, содержимое сумматора 3 прибавляется или вычитает ся из Содержимого сумматора 5 со сдвигом на один разряд влево. Кроме того, к содержимому сумматора 2 прибавляется прямой или дополнительный код содержимого регистра 1. В результате в сумматоре 5 образуется значение , а в

Зумматоре 2 - значение X -. К началу второго такта информационные сигналы совходов 11 и 12 снимаются.

Во втором такте по управляющему сигналу, поступившему на управляющий вход 13, производится выдача информации на выходы 15 и 16 устройства. При этом если единичный сигнал появляется на выходе 15, это свидетельствует о том, что

0 очередной разряд результата численно равен 1. Если единичный сигнал появляется на выходе 16, очередной разряд результата равен 1 . : Если единичный сигнал не появляется ни на одном из выходов 15 и 16, очередной разряд результата численно равен О. По единич юму сигналу с выхода 15 в i -ый разряд сумматора 3 прибавляется 1 и производится выдача дополнительного кода сумматора

0 2. По единичному сигналу с выхода 16 из 1 --ГО разряда сумматора 3 вычитается единица, что осушествляется приемом дополнительного кода из регистра 1, а также производится выдача прямого кода

5 сумматора 2. В результате во втором такте в сумметоре 3 образуется код по окончании второго такта (так как суммирование в сумматоре 5 производигся с задержкой) в сумматоре 5 образует0ся код К .

В третьем такте по управляющему сигналу, поступающему на управляющий вход 14 устройства, производится сдвиг влево на один разряд содержимого

5 сумматора 5 и сдвиг вправо на один разряд содержимого регистра 1. На этом заканчивается цикл, вычислений.

В результате выполнения (И+3) циклов на вььходах 15 и 16 устройства фор0мируется последовательно разряд за раз-рядом (начиная со старших разрядов) зн&чение обратной величины исходного опе,ранда, задержанное на три- разряда, т.е.

функция Y- , представленное избы .

ТОЧНЫМ двоичным кодом с цифрами 1,0, 1,

в каждом разряде. В результате выполнения (П + 3) циклов результат получается симметрично округленным.

Благодаря совмещению во времени про0цесса поразрядного ввода операнда и вычисления очередных цифр результата разряды его, несущие большую 1шфор мацию о HeMj вычисляются в первых цик- . лах. Это позволяет эффективно использо5вать устройство в системах управления процессами в реальном масштабе времени когда процесс формирования цифр операнда ограничен внешними факторами, а управляющее воздействие для исполнительного органа системы формируется непосредственно по результатам вычислений. Кроме тогО| увеличивается быстродействие при работе в вычислительной среде, где устройства такого типа соединены последовательно. Поразрядный ввод операнда и вьгаод результата позволяет длительно уменьшать количество внешних связей, которое не зависит от увеличения разрядности операнда. Это обуславливает возможность реализации устройства в виде большой интегральной схемы. Формула изобретения 1. Устройство для вычисления обратной величины, содержащее два сумматора, отличающееся тем, что, с целью повышения быстродействия, устройсгво содержит третий сумматор, регистр, блок элементов ИЛИ и блок анализа разрядов, причем выходы первого и второго сумматоров соединены с первой и второй группами входов блока элементов ИЛИ со- oTBeTCTBeHHOj выходы блока элементов ИЛИ подключены ко входам третьего сумматора, выходы регистра подключены к ин формационным входам первого и второго сумматоров, первый и второй управляющие входы которых подключены к первому и второму информационным входам устройства соответственно, а третий и четвертый управляющие входы - к первому и второму выходам устройства соответствен но, первый управляющий вход устройства подключен к управляющему входу блока анализа разрядов, выходы которого подключены к выходам устройства, а знакбвый и информационны э входы - к знаковому и информационным выходам третьего сумматора соответственно, второй управляющий вход устройства подключен к управляющим входам регистра и третьего сумматора. 2, Устройство по п. 1,отличающее с я тем, что блок анализа разрядов содержит элементы И, ИЛИ, И-НЕ и запрета, причем информационные входы блока анализа разрядов подключены ко входам элемента ИЛИ и элемента И-НЕ, выходы которых подключены к первым входам элементов запрета и И соответственно, вторые входы Которых соединены с управляющим входом блока анализа разрядов, знаковый вход которого подключен к управляющему входу элемента запрета и третьему входу элемента И, выходы которых подключены соответственно к первому и второму выходам блока анализа разрядов. Источники информации, принятые во внимание при экспертизе 1.Акцептованная заявка Великобритании № 13О40О8, кл. G 4 А, 1973. 2.Патент США N 374О722, кл. 34О-172.5, 1973. 3.Патент Франции № 2147937, кл. Q 06 F, 1973. 4.Авторское свир;етельство СССР № 362296, кл. G 06 F 7/39, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат двоичных чисел | 1976 |

|

SU602941A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для алгебраического сложения чисел | 1976 |

|

SU638959A1 |

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Устройство для вычисления обратной величины | 1984 |

|

SU1262477A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

Авторы

Даты

1980-05-05—Публикация

1976-08-03—Подача