(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1981 |

|

SU1010652A1 |

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

| Запоминающее устройство с автономным контролем | 1975 |

|

SU690567A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1974 |

|

SU492000A1 |

1

Изобретение относится к области за поминающих устройств. Известно оперативное запоминающее устройство с блокировкой неисправных яек, содержащее первый регист адреса, подключенный через дешифратор адреса накопителю, соединенному с регистром числа, второй регистр адреса и блок управления.

Предлагаемое устройство отличается от известного тем, что с целью. упрощения устройства и повышения надежности :его работы оно содержит схему сравне- ния, счетчик к дополнительный регистр, входы которого соединены с выходами первого регистра адреса, входы схемы сравнения подключены к выходам дополнительного регистра и второго регистра .адреса, выход схемы сравнения и вход :счетчика соединены с блоком управления а выход счетчика иодкнючен к накопителю.

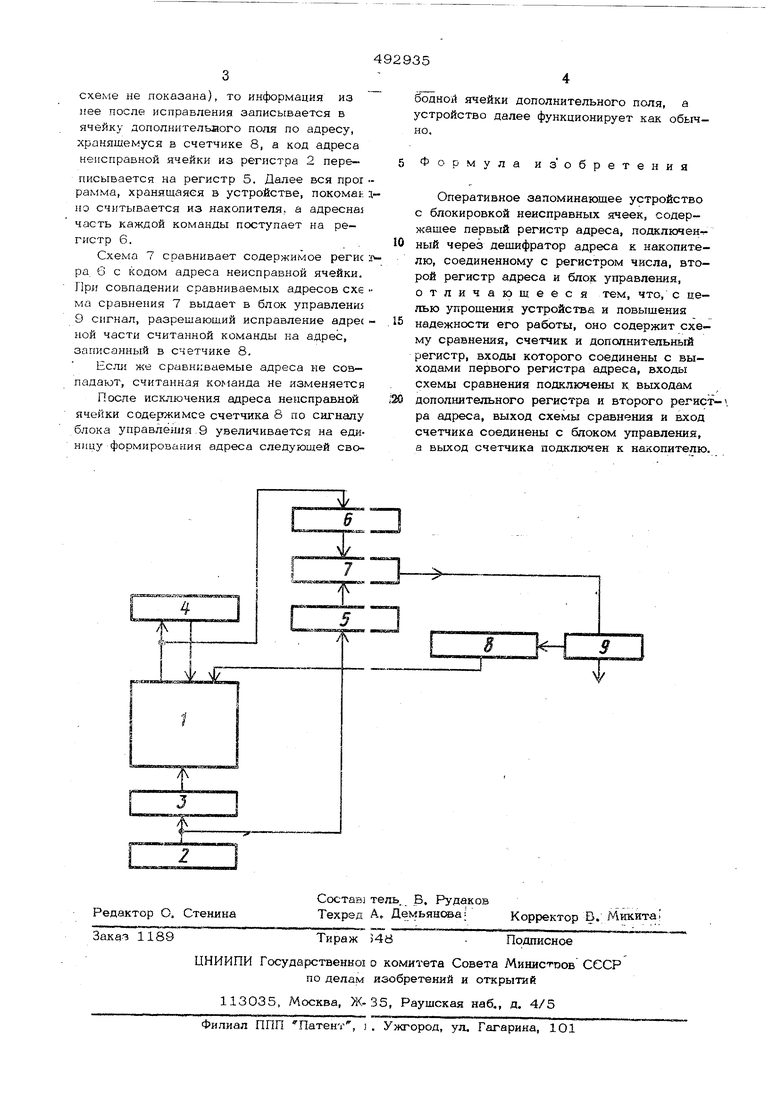

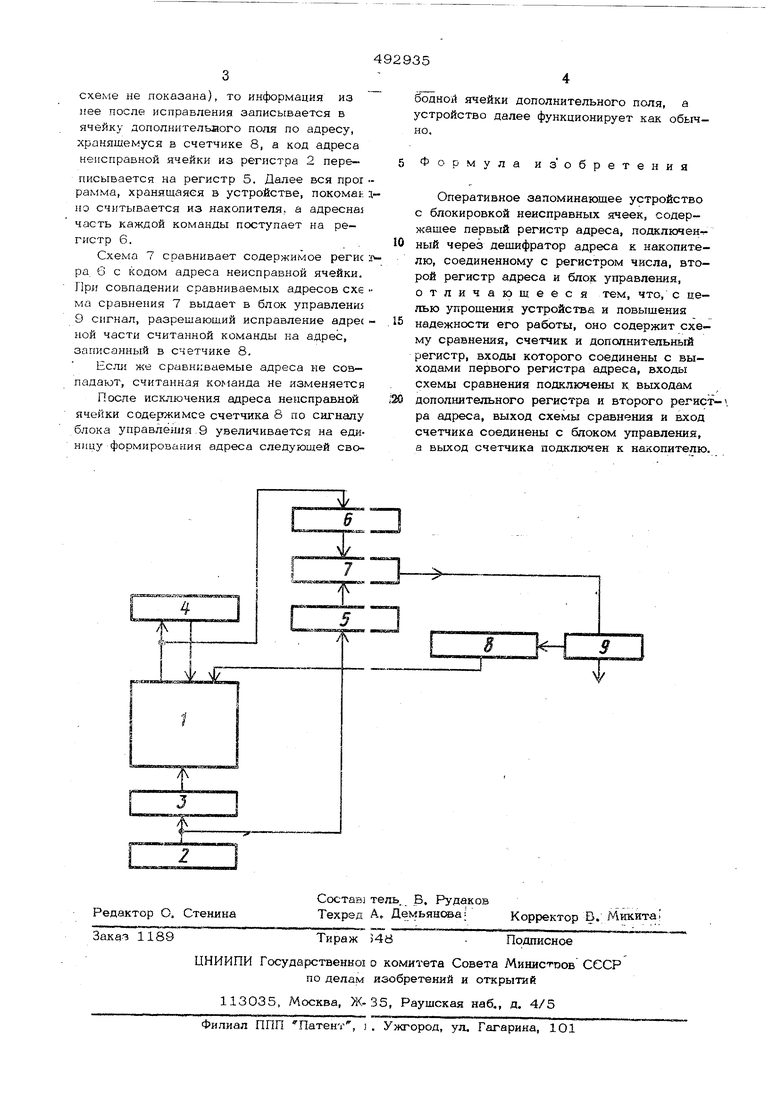

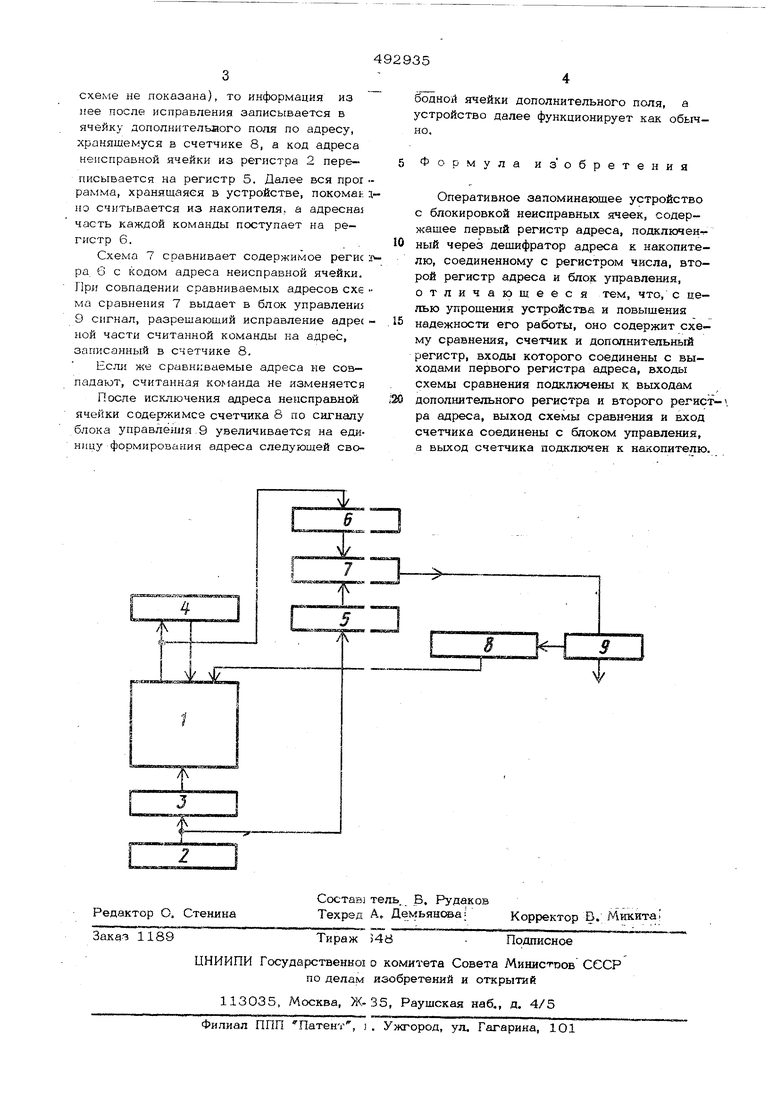

На чертеже изображена блок-схема .устройства.

Устройство содержит накопитель 1, 1цхлючающий основное и дополнительное поля элементов памяти, первый регистр ;адреса 2, дешифратор адреса 3, регистр 5 числи 4, второй регистр адреса 5, слу:жащий для хранения кода адреса неисп- |равной ячейки, дополнительный регистр 6, преднаизначенный для хранения кода текущего адреса, схему сравнения 7, счет

10 ;чик 8 и блок управления .9.

; Входы регистра 5 соединены с въ хо:дами регистра 2. Входы схемы сравнения 7 подключены к выходам регистров 6 и 15. Выход схемы 7 и вход счетчика 8 сое55 |динены с блоком управления 9, а вы од i счетчика 8 подключен к накопителю 1, ; При работе устройства код адреса поступает на первый регистр адреса 2. Чеipea регистр числа 4 производится прием

20 :и выдача информации в накопителе 1. В счетчике 8 хранится код адреса свобод: ной в .данный момент ячейки из дополни,тельного поля. Если при работе устройст ва обнаружится неисправная ячейка (необ25 ходимая для этого схема контроля на блоксхеме не показана), то информация из ее после исправления записывается в ячейку дополнительного поля по адресу, хранящемуся в счетчике 8, а код адреса неисправной ячейки из регистра 2 переписывается на регистр 5. Далее вся прог рамма, хранящаяся в устройстве, покомак д™ ю считывается из накопителя, а адресная часть каждой команды поступает на регистр 6.. .

Схема 7 сравнивает содержимое регис ра 6 с кодом адреса неисправной ячейки. При совпадении сравниваемых адресов схе ма сравнения 7 выдает в блок управлени5 9 сигнал, разрешающий исправление адрес ной части считанной команды на адрес, записанный в счетчике 8.

Если же сравниваемые адреса не совпадают, считанная команда не изменяется

После исключения адреса неисправной ячейки содержимое счетчика 8 по сигналу блока управления,9 увеличивается на единицу формирования адреса следующей сво±

И

А

t ioexa мнвжаяхЗ

бодной ячейки дополнительного поля, а устройство далее функционирует как обычно.

Формула и а обретения

Оперативное запоминающее устройство с блокировкой неисправных ячеек, содержащее первый регистр адреса, подключенный через дешифратор адреса к накопителю, соединенному с регистром числа, второй регистр адреса и блок управления, отличающееся тем, что, с целью упрощения устройства и повыщения

надежности его работы, оно содержит схему сравнения, счетчик и дополнительный

регистр, входы которого соединены с выходами первого регистра адреса, входы

схемы сравнения подключены к выходам дополнительного регистра и второго регнст- ра адреса, выход схемы сравнения и вход счетчика соединены с блоком управления, а выход счетчика подключен к накопителю.

ц

Z3

«fK-SSa:. IMaeMHDBa

Л-J

«

Авторы

Даты

1975-11-25—Публикация

1973-11-16—Подача