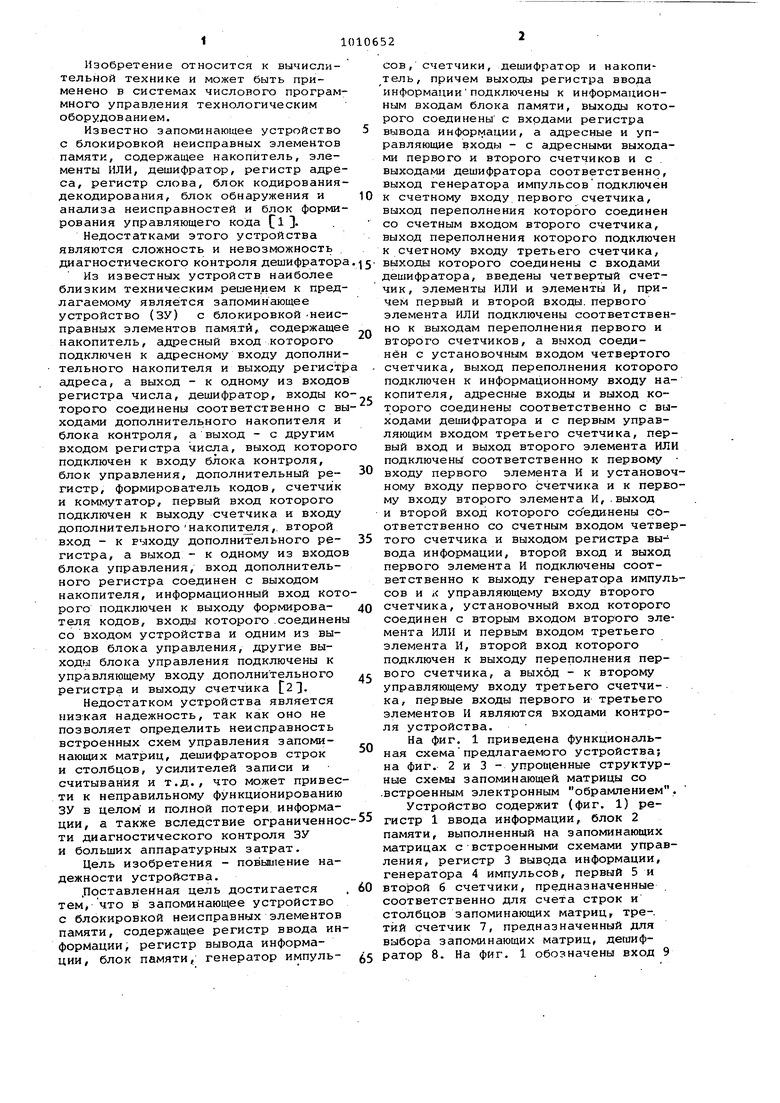

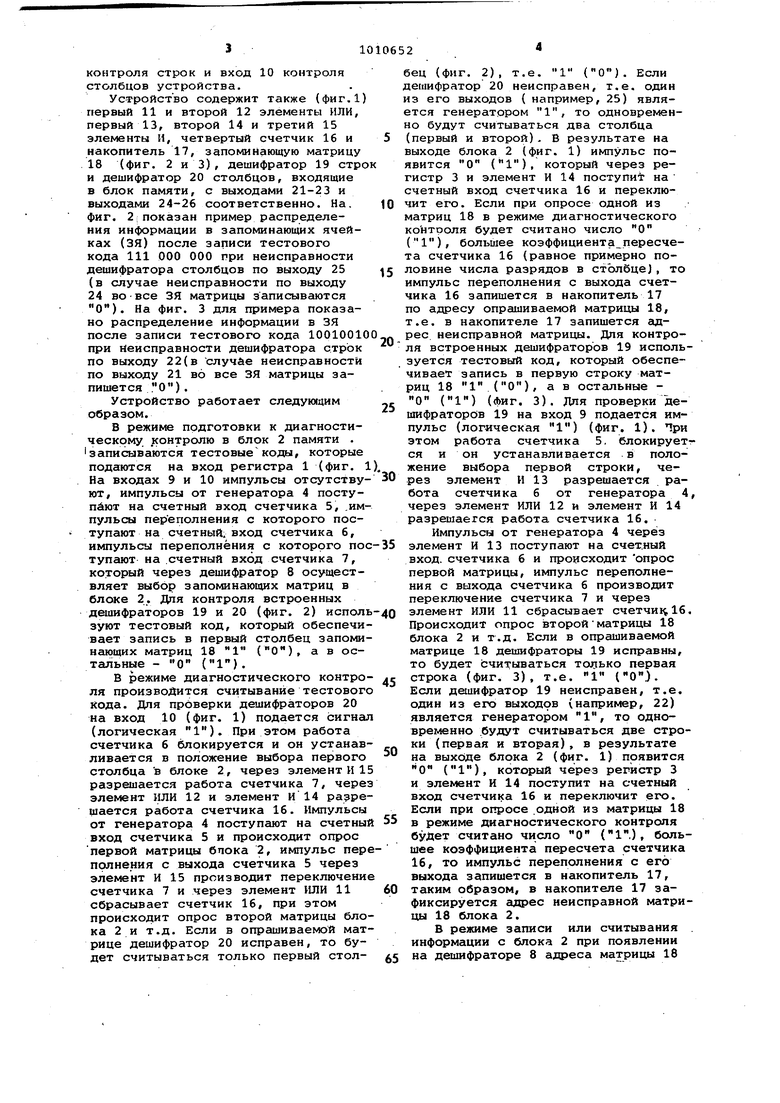

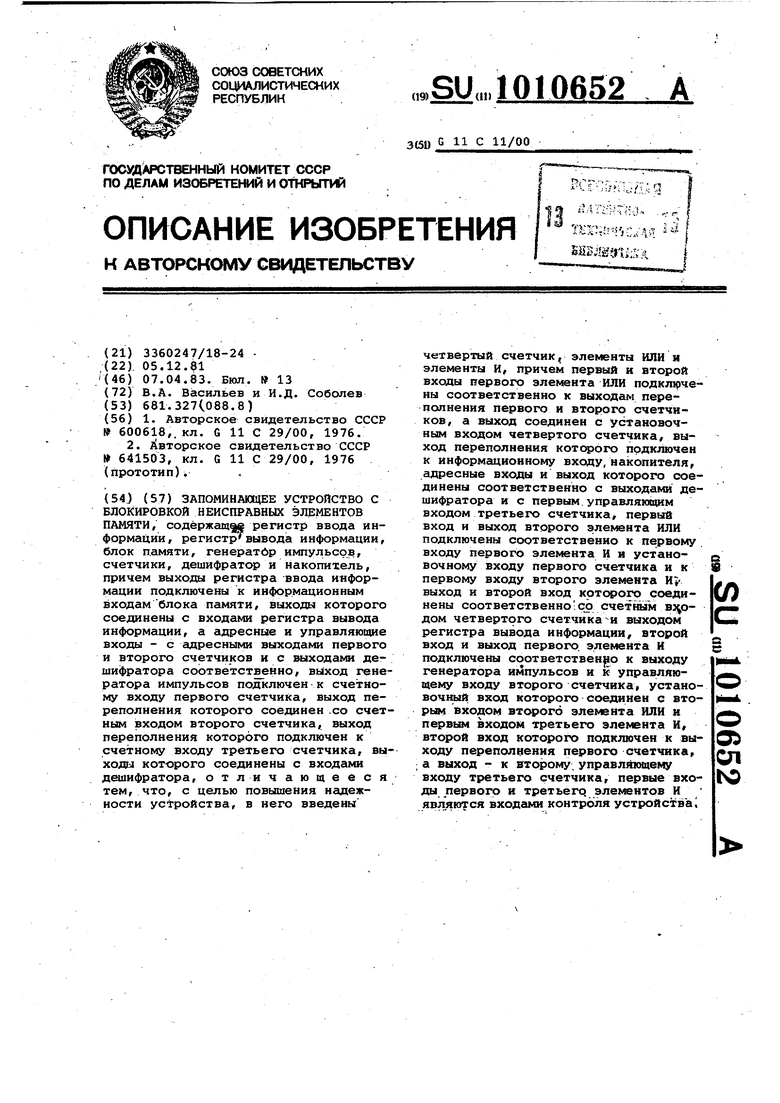

Изобретение относится к вычислительной технике и может быть применено в системах числового програм много управления технологическим оборудованием. Известно запоминающее устройство с блокировкой неисправных элементов памяти, содержащее накопитель, элементы ИЛИ, дешифратор, регистр адре са, регистр слова, блок кодирования декодирования, блок обнаружения и анализа неисправностей и блок форми рования управляющего кода fl 3Недостатками этого устройства являются сложность и невозможность диагностического контроля дешифратор Из известных устройств наиболее близким техническим решением к пред лагаемому является запоминающее устройство (ЗУ) с блокировкой .неис правных элементов памяти, содержаще накопитель, адресный вход которого подключен к адресному входу дополни тельного накопителя и выходу регист адреса, а выход - к одному из входо регистра числа, дешифратор, входы к торого соединены соответственно с в ходами дополнительного накопителя и блока контроля, а выход - с другим входом регистра числа, выход которо подключен к входу блока контроля, блок управления, дополнительный регистр, формирователь кодов, счетчик и коммутатор, первый вход которого подключен к выходу счетчика и входу дополнительного накопителя,, второй вход - к Еыходу дополнительного регистра, а выход - к одному из входо блока управления, вход дополнительного регистра соединен с выходом накопителя, информационный вход кот рого подключен к выходу формирователя кодов, входы которого .соединены со входом устройства и одним из выходов блока управления, другие выходы блока управления подключены к управляющему входу дополнительного регистра и выходу счетчика 2. Недостатком устройства является низкая надежность, так как оно не позволяет определить неисправность встроенных схем управления запоминающих матриц, дешифраторов строк и столбцов, усилителей записи и считывания и т.д., что может привести к неправильному функционированию ЗУ в целом и полной потери, информации, а также вследствие ограниченное ти диагностического контроля ЗУ и больших аппаратурных затрат. Цель изобретения - повышение надежности устрой-ства. Доставленная цель достигается тем что в запоминающее устройство с блокировкой неисправных элементов памяти, содержащее регистр ввода информации, регистр вывода информации, блок памяти, генератор импульсов, счетчики, дешифратор и накопитель, причем выходы регистра ввода информацииподключены к информационным входам блока памяти, выходы которого соединены с входами регистра вывода информации, а адресные и управляющие входы - с адресными выходами первого и второго счетчиков и с выходами дешифратора соответственно, выход генератора импульсовподключен к счетному входу первого счетчика, выход переполнения которого соединен со счетным входом второго счетчика, выход переполнения которого подключен к счетному входу третьего счетчика, выходы которого соединены с входами дешифратора, введены четвертый счетчик, элементы ИЛИ и элементы И, причем первый и второй входы, первого элемента ИЛИ подключены соответственно к выходам переполнения первого и второго счетчиков, а выход соединён с установочным входом четвертого счетчика, выход переполнения которого подключен к информационному входу накопителя, адресные входы и выход которого соединены соответственно с выходами дешифратора и с первым управляющим входом третьего счетчика, первый вход и выход второго элемента ИЛИ подключены соответственно к первому входу первого элемента И и установочному входу первого счетчика и к первому входу второго элемента И,.выход и второй вход которого соединены соответственно со счетным входом четвертого счетчика и выходом регистра вывода информации, второй вход и выход первого элемента И подключены соответственно к выходу генератора импульсов и к управляющему входу второго счетчика, установочный вход которого соединен с вторым входом второго элемента ИЛИ и первым входом третьего элемента И, второй вход которого подключен к выходу переполнения первого счетчика, а выход - к второму управляющему входу третьего счетчи-. ка, первые входы первого и третьего элементов И являются входами контроля устройства. На фиг. 1 приведена функциональная схемапредлагаемого устройства; на фиг. 2 и 3 - упрощенные структурные схемы запоминающей матрицы со встроенным электронным обрамлением. Устройство содержит (фиг. 1) регистр 1 ввода информации, блок 2 памяти, выполненный на запоминающих матрицах с встроенными схемами управления, регистр 3 вывода информации, генератора 4 импульсов, первый 5 и второй 6 счетчики, предназначенные соответственно для счета строк и столбцов запоминающих матриц, тре-. тйй счетчик 7, предназначенный для выбора запоминающих матриц, дешифатор 8. На фиг. 1 обозначены вход 9 контроля строк и вход 10 контроля столбцов устройства. Устройство содержит также {фиг.1) первый 11 и второй 12 элементы ИЛИ, первый 13, второй 14 и третий 15 элементы И, четвертый счетчик 16 и накопитель 17, запоминающую матрицу 18 (фиг. 2 и 3), дешифратор 19 стро и дешифратор 20 столбцов, входящие в блок памяти, с выходами 21-23 и выходами 24-26 соответственно. На. фиг. 2:показан пример распределения информации в запоминающих ячейках (ЗЯ) после записи тестового кода 111 000 000 при неисправности дешифратора столбцов по выходу 25 (в случае неисправности по выходу 24 во все ЗЯ матрицы записываются О). На фиг. 3 для примера показано распределение информации в ЗЯ после записи тестового кода 10010010 при Неисправности дешифратора строк по выходу 22(в случае неисправности по выходу 21 во все ЗЯ матрицы запишется О) . Устройство работает следуюгдим образом. В режиме подготовки к диагностическому контролю в блок 2 памяти . записываются тестовыекоды, которые подаются на вход регистра 1 (фиг. На входах 9 и 10 импульсы отсутствуют, импульсы от генератора 4 поступдют на счетный вход счетчика 5, .импульсы переполнения с которого поступают на счетный, вход счетчика 6, импульсы переполнения с которого по тупают на счетный вход счетчика 7, который через дешифратор 8 осуществляет выбор запоминаюсщх матриц в блоке 2. Для контроля встроенных дешифраторов 19 и 20 (фиг. 2) испол зуют тестовый код, который обеспечи вает запись в первый столбец запоми матриц 18 1 (О), а в остальные - О (1) . В режиме диагностического контро ля производится считывание тестовог кода. Для прбверки дешифраторов 20 на вход 10 (фиг. 1) подается сигнал (логическая 1). При этом работа счетчика 6 блокируется и он устанав ливается в положение выбора первого столбца в блоке 2, через элемент И 1 разрешается работа счетчика 7, чере элемент ИЛИ 12 и элемент И 14 разре шается работа счетчика 16. Импульсы от генератора 4 поступают на счетны вход счетчика 5 и происходит опрос первой матрицы бпока 2, импульс пер прлнения с выхода счетчика 5 через элемент И 15 производит переключени счетчика 7 и через элемент ИЛИ 11 сбрасывает счетчик 16, при этом происходит опрос второй матрицы бло ка 2 и т.д. Если в опрашиваемой мат рице дешифратор 20 исправен, то будет считываться только первый столбец (фиг. 2), т.е. 1 (О). Если ешифратор 20 неисправен, т.е. один из его выходов ( например, 25) является генератором 1, то одновременно будут считываться два столбца (первый и второй). В результате на выходе блока 2 (фиг. 1) импульс появится О (1), который через регистр 3 и элемент И 14 поступит на счетный вход счетчика 16 и переключит его. Если при опросе одной из матриц 18 в режиме диагностического контроля будет считано число О (1), большее коэффициента пересчета счетчика 16 (равное примерно половине числа разрядов в столбце), то импульс переполнения с выхода счетчика 16 запишется в накопитель 17 по адресу опрашиваемой матрицы 18, т.е. в накопителе 17 запишется адрес неисправной матрицы. Для контроля встроенных дешифраторов 19 используется тестовый код, который обеспечивает запись в первую строку матриц 18 1 (О), а в остальные (1) (фиг. 3). Для проверки дешифраторов 19 на вход 9 подается импульс (логическая 1) (фиг. 1). Чри этом работа счетчика 5. блокируется и он устанавливается в положение выбора первой строки, через элемент И 13 разрешается работа счетчика 6 от генератора 4, через элемент ИЛИ 12 и элемент И 14 разрешается работа счетчика 16. Импульсы от генератора 4 через элемент И 13 поступают на счет.ный вход, счетчика 6 и происходит опрос первой матрицы, импульс переполнения с выхода счетчика 6 производит переключение счетчика 7 и через элемент ИЛИ 11 сбрасывает счетчиц 16. Происходит опрос второйматрицы 18 блока 2 и т.д. Если в опрашиваемой матрице 18 дешифраторы 19 исправны, то будет считываться первая строка (фиг. 3), т.е. 1 (О.). Если дешифратор 19 неисправен, т.е. один из его выходов (например, 22) является генератором 1, то одновременно .будут считываться две строки (первая и вторая), в результате на выходе блока 2 (фиг. 1) появится О (1), который через регистр 3 и элемент И 14 поступит на счетный вход счетчика 16 и переключит его. Если при опросе .одной из матрицы 18 в режиме диагностического контроля будет считано число О (1), большее коэффициента пересчета счетчика 16, то импульс переполнения с его выхода запишется в накопитель 17, таким образом, в накопителе 17 зафиксируется адрес неисправной матрицы 18 блока 2. В режиме записи или считывания . информации с блока 2 при появлении на дешифраторе 8 адреса матрицы 18

G неисправным электронным обрамлением на выходе накопнтеля 17 появится импульс, который поступает на вход счетчика 7 и вызывает его переключение на следующий адрес,

Таким образом, устройство позволяет выявить, зафиксировать и блокировать именно те неисправные запоминающие матрицы 18 блока 2 памяти.

которые ведут к искажению и полной потере информации при рабрте ЗУ. При выходе из строя одной или нескольких матриц 18 устройство сохраняет работоспособность.

Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой надежности по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1010651A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для обработки информации о комплектовании партии деталей | 1986 |

|

SU1425718A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| СИСТЕМА ДИАГНОСТИКИ ЗАБОЛЕВАНИЙ | 1991 |

|

RU2007755C1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2020 |

|

RU2723288C1 |

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1474739A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЭЛЕМЕНТОВ ПАМЯТИ, содержащее регистр ввода информации, регистр вывода информации, блок памяти, генератбр импульсов, счетчики, дешифратор и накопитель, причем выходы регистра ввода информации подключены к информационным входам блока памяти, выходы которого соединены с входами регистра вывода информации, а адресные и управляющие входы - с адресными выходами первого и второго счетчиков и с выходами дешифратора соответственно, выход генератора импульсов подключен к счетному входу первого счетчика, выход переполнения которого соединен .со счетным входом второго счетчика, выход переполнения которого подключен к счетному входу третьего счетчика, выходы которого соединены с входами дешифратора, отличающееся тем, что, с целью повышения надежности устройства, в него введены четвертый счетчик, элементы ИЛИ и элементы И, причем первый и второй входы первого элемента ИЛИ подкл19чены соответственно к выходам переполнения первого и второго счетчиков, а выход соединен с установочным входом четвертого счетчика, выход переполнения которого подключен к информационному входу, накопителя, адресные входы и выход которого соединены соответственно с выходами дешифратора и с первым.управляющим входом третьего счетчика, первый вход и выход второго элемента ИЛИ подключены соответственно к первому входу первого элемента И и установочному входу первого счетчика и к первому входу второго элемента И;. выход и второй вход которого соединены соответственно ,со счетйымвз одом четвертого счетчиками выходом регистра вывода информации, второй вход и выход первого, элемента И подключены соответственно к выходу генератора И14пульсов и к управляющему входу второго счетчика, устаноВОЧ1ШЙ вход которого соединен с вторьт входом второго элемента ИЛИ и первым входом третьего элемента И, О второй вход которого подключен к выходу переполнения первого счетчика, ел ; а выход - к второму. управл5«ощему ND входу третьего счетчика, первые входы первого и третьегр элементов И являются входами контроля устройстваi

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU600618A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-04-07—Публикация

1981-12-05—Подача