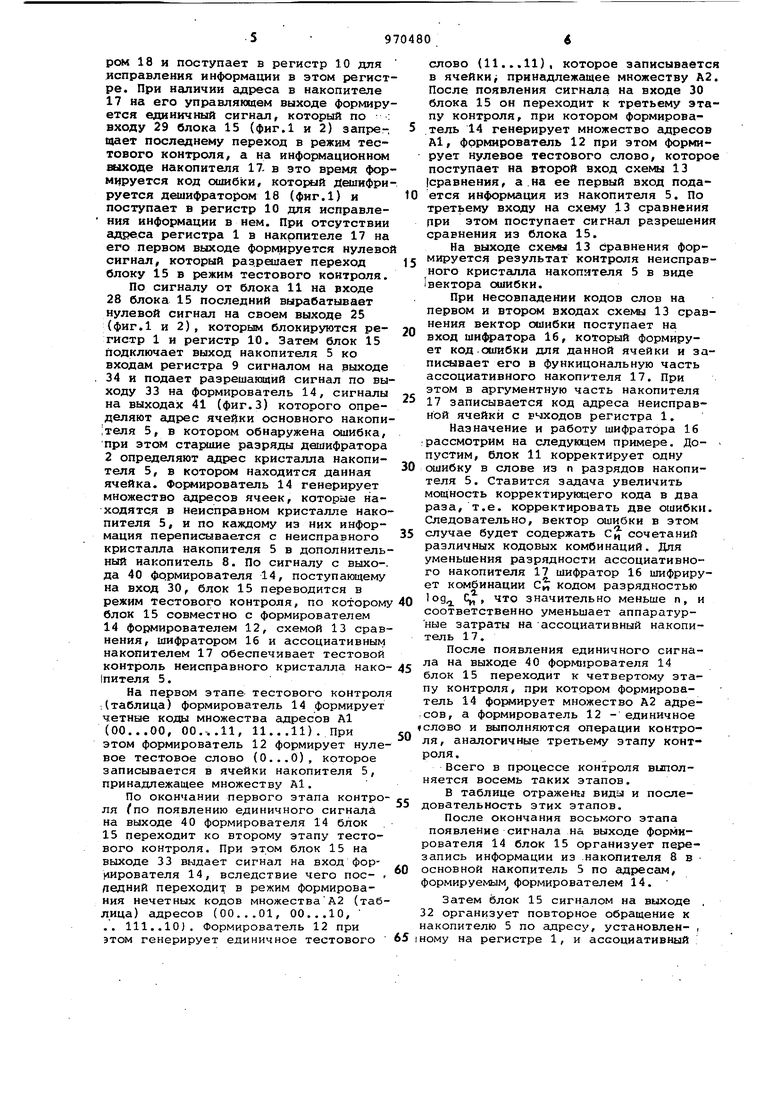

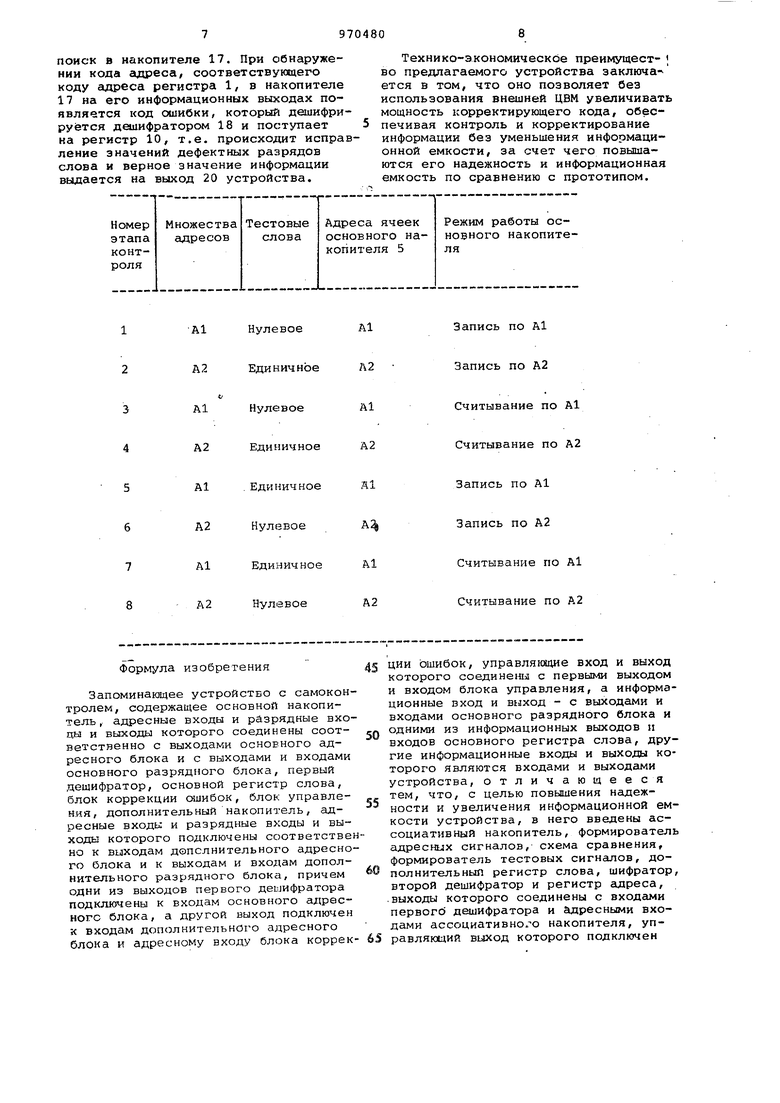

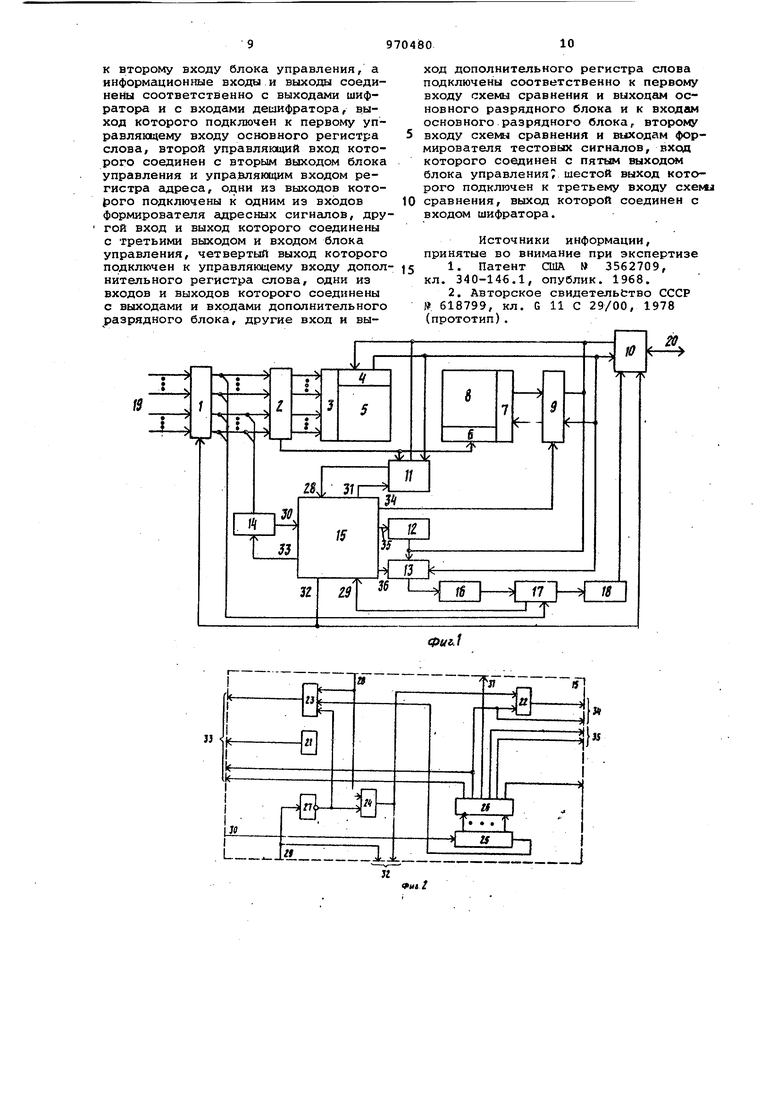

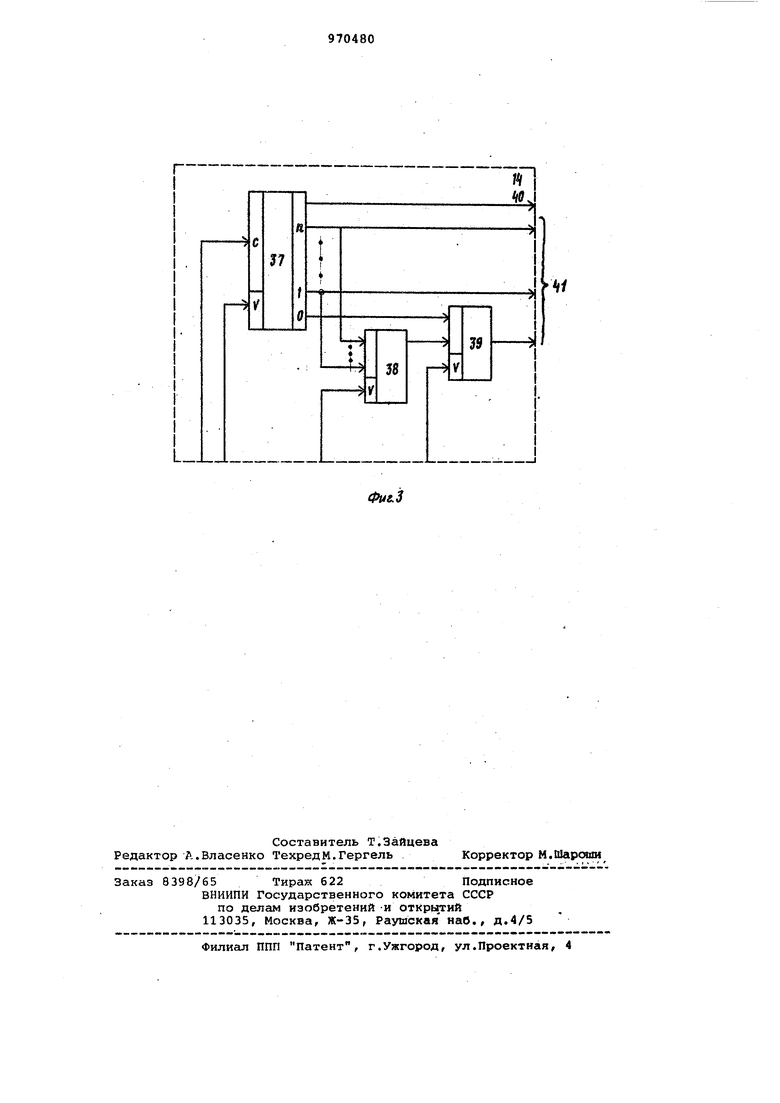

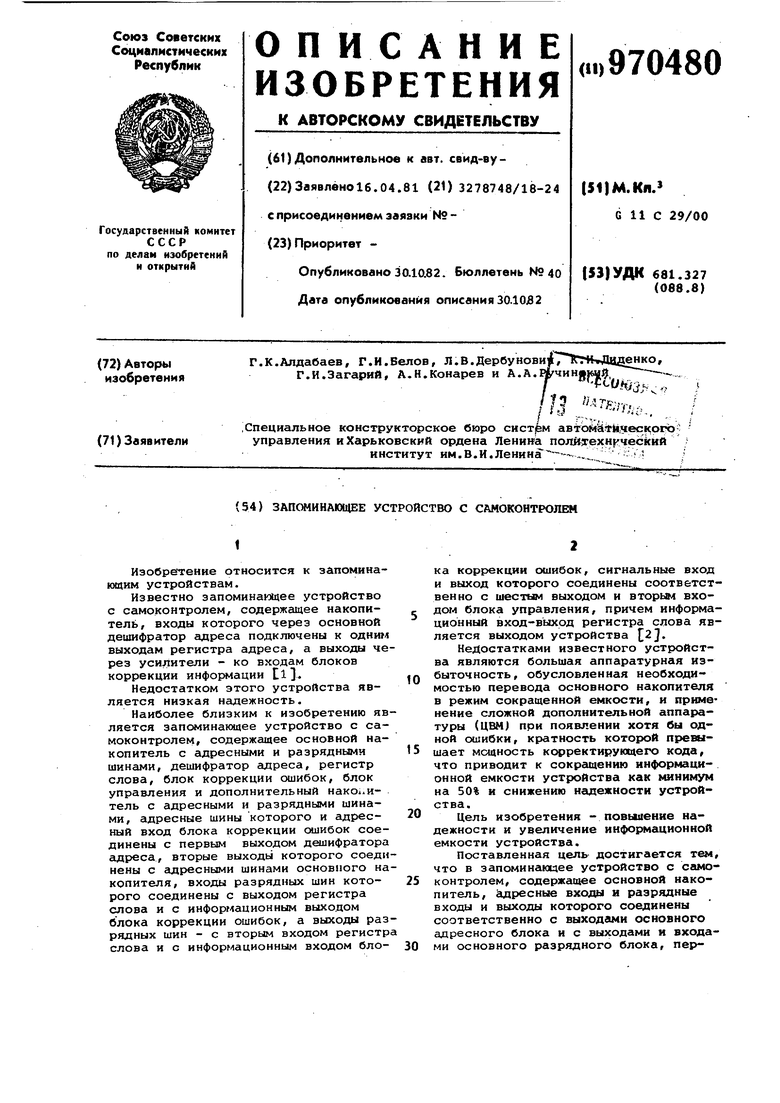

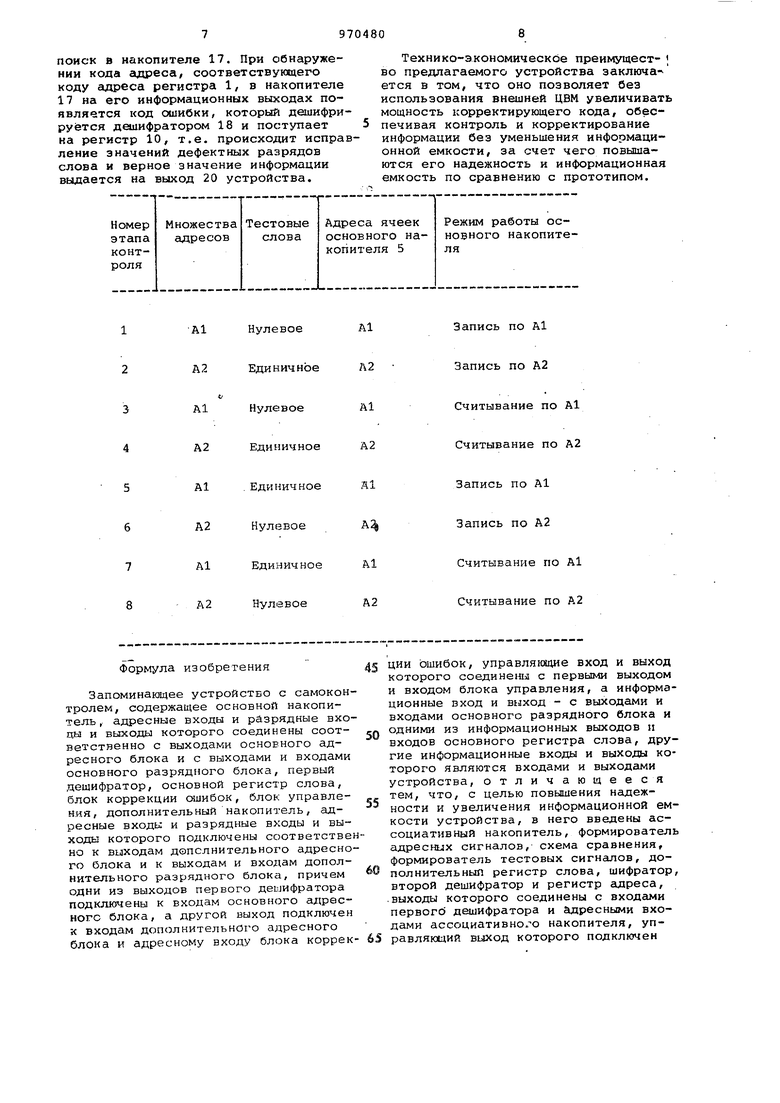

вый дешифратор, основной регистр слова, блок коррекции ошибок, блок управления, дополнительный накопитель, адресные входы и разрядные входы и выходы которого подключены соответственно к выходам дополнительного адресного блока и к выходшч и |входам дополнительного разрядного блока, причем одни из выходов первого дешифратора подключены ко входам основного адресного блока, а другой выход подключен ко входам дополнительного адресного блока и адресному входу блока коррекции ошибок, управляющие вход и выход которого соедине ны с первьпии выходами и входами блока управления, а информационные вход и выход - с выходами и входами основ ного разрядного блока и одними из информационных выходов и входов осно ного регистра слова, другие информационные входы ивыходы которого явля ются входами и выходами устройства, введены ассоциативный накопитель,фор мирователь тестовых сигналов, дополнительный регистр слова, шифратор, второй.дешифратор и регистр адреса, выходы которЬго соединены со входами первого дешифратора и адресными входами ассоциативного накопителя, управляющий выход которого подключен к второму входу блока управления, а ин формационные входы и выходы соединен соответственно с выходами шифратора со входами дешифратора, выход которо го подключен к первому управляющему входу основного регистра слова, второй управляющий вход которого соединен со вторым выходом блока управления и управляющим входом регистра ад реса, один из выходов которого подключен к одному из входов формирователя адресных сигналов, другой вход и выход которого соединены с третьими выходом и входом блока управления четвертый выход которого подключен к управляющему входу дополнительного регистра слова, один из входов и выходов которого соединены с выходами и входами дополнительного разрядного блока, другие вход и выход дополнительного регистра слова подключены соответственно к первому входу схемы сравнения и выходам основного разряд ного блока и ко входам основного раз рядного блока, второму входу схемы сравнения и выходам формирователя тестовых сигналов, вход которого сое динен с пятым выходом блока управления , шестой выход которого подключен к третьему входу схемы сравнения, вы ход которой соединен со входом шифратора. На фиг. 1 приведено предлс1гаемое устройство, структурная схема; на . фиг.2 и 3 - функциональные схемы бло ка управления и формирователя адресных сигналов соответственно. Устройство (фиг.1) содержит реистр 1 адреса, первый дешифратор 2, сновной адресный блок 3, основной азрядный блок 4, основной накопиель 5, дополнительный адресный блок б, дополнительный разрядный блок 7, ополнительный накопитель 8, основной 9 и дополнительный 10 регистры лова, блок 11 коррекции ошибок,формирователь 12 тестовых сигналов, схему 13 сравнения, формирователь 14 адресных сигналов, блок 15 управления, шифратор 16, ассоциативный накопитель 17, второй дешифратор 18. На Фиг.1 обозначены адресные входы 19 и информационные входы и выходы 20. Блок управления содержит (фиг.,2) генератор 21 прямоугольных сигналов, первый 22, второй 23 и третий 24 элементы И, счетчик 25, третий дешифратор 26 и элемент НЕ 27. На фиг.1 и 2 обозначены также первый 28, второй 29 и третий 30 входы блока управления, первый 31, второй 32, третий 33, четвертый 34, пятый 35 и шестой 36. выходы блока управления. Формирователь адресных сигналов (фиг.З) содержит п-разрядный двоичг ный счетчик 37, блок 38 контроля четности и коммутатор 39. Счетный и управляющий входы счетчика 37, управляющие входы блока 38 и коммутатора 39 являются входами . формирователя. Выход 40 переполнения счетчика является одним из выходов формирователя, а разрядные выходы счетчика, кроме нулевого, и-выход коммутатора являются другими выходами 41 формирователя. Устройство работает следующим образом. Основной накопитель 5 при числе отказов, которые устраняются применением блока 11, работает с коррекцией ошибок посредством корректирукяцих кодов. В определенный момент времени наступает ситуация, когда-МОЩНОСТЬ корректирующего кода блока 11 оказывается недостаточной для нормального функционирования-, основного накопителя 5. При этом блок 11 выдает единичный сигнал на вход 28 .блока 15 управления. Параллельно с выборкой информации из накопителя 5 и работой блока 11 осуществляется ассоциативный поиск по адресу регистра 1 в ассоциативном накопителе 17. При наличии этого адреса в накопителе 17 на его управляющем выходе формируется единичный сигнал, который по входу 29 блока 15 (фиг.1 и 2) запрещает последне1 1у переход в режим тестового контроля, а на информационном выходе накопителя 17 в это время формируется код ошибки, который дешифрируется дешифратором 18 и поступает в регистр 10 для исправления информации в этом регист ре. При наличии адреса в накопителе 17 на его управляющем выходе формиру ется единичный сигнсШ, который по : входу 29 блока 15 (фиг.1 и 2) запре-, (цает последнему переход в режим тестового контроля/ а на информационнее выходе накопителя 17. в это время фор мируется код ошибки, который Дешифри руется дешифратором 18 (фиг.1) и поступает в регистр 10 для исправления информации в нем. При отсутствии адреса регистра 1 в накрпителе 17 на его первом выходе форлдаруется нулево сигнал, который разрешает переход блоку 15 в режим тестового контроля. По сигналу от блока 11 на входе 28 блока 15 последний вырабатывает нулевой сигнал на своем выходе 25 {фиг.1 и 2), которым блокируются регистр 1 и регистр 10. Затем блок 15 подключает выход накопителя 5 ко входам регистра 9 сигналом на выходе 34 и подает разрешающий сигнал по вы ходу 33 на формирователь 14, сигналы на выходах 41 (фиг.З) которого определяют адрес ячейки основного накопи ;теля 5, в котором обнаружена ошибка, при этом старшие разряды дешифратора 2 определяют адрес Кристалла накопителя 5, в котором находится данная ячейка. Формирователь 14 генерирует множество адресов ячеек, которые находятся в неисправном кристалле нако пителя 5, и по каждому из них информация переписывается с неисправного кристалла накопителя 5 в дополнитель ный накопитель 8. По сигналу с выхо-. да 40 формирователя 14, поступающему на вход 30, блок 15 переводится в режим тестового контроля, по которому блок 15 совместно с формирователем 14формирователем 12, схемой 13 срав нения, шифратором 16 и ассоциативным накопителем 17 обеспечивает тестовой контроль неисправного кристалла нако1пителя 5. На первом этапе- тестового контроля ; (таблица) формирователь 14 формирует четные коды множества адресов А1 (00...00, 00.-..11, 11...11). При этом формирователь 12 формирует нулевое тестовое слово (0...0), которое записывается в ячейки накопителя 5, принадлежащее множеству А1. По окончании первого этапа контроля (по появлению единичного сигнала на выходе 40 формирователя 14 блок 15переходит ко второму этапу тестового контроля. При этом блок 15 на выходе 33 выдает сигнал на вход форК1Ирователя 14, вследствие чего пос- . дедний переходит в режим формирования нечетных кодов множества А2 (таблица) адресов (00...01, 00...10, .. 111..10). Формирователь 12 при этом генерирует единичное тестового слово (11. ..11), которое записывается в ячейки принадлежащее множеству Л2. После появления сигнала на входе 30 блока 15 он переходит к третьему этапу контроля, при котором формирователь 14 генерирует множество адресов А1, формирователь 12 при этом формирует нулевое тестового слово, которое поступает на второй вход схемы 13 |сравнения, а . на ее первый вход подается информация из накопителя 5. По третьему входу на схему 13 сравнения ПРИ этом поступает сигнгш разрешения сравнения из блока 15. На выходе схемы 13 сравнения формируется результат контроля неисправного кристалла накопителя 5 в виде iвектора ошибки. При несовпадении кодов слов на первом и втором входах схемы 13 сравнения вектор ошибки поступает на вход шифратора 16, который формирует код ошибки для данной ячейки и запиолвает его в функицональную часть ассоциативного накопителя 17. При этом в аргументную часть накопителя 17 записывается код адреса неисправной ячейки с рчходов регистра 1. Назначение и работу шифратора 16 рассмотрим на следующем примере. До- пустим, блок 11 корректирует одну ошибку в слове из п разрядов накопителя 5. Ставится задача увеличить мощность корректирующего кода в два раза, т.е. корректировать две ошибки. Следовательно, вектор ошибки в этом случае будет содержать С сочетаний различных кодовых комбинаций. Для уменьшения разрядности ассоциативного накопителя 17 шифратор 16 шифрирует ксадбинации С, кодом разрядностью log Су,, что значительно меньше п, и соответственно уменьшает аппаратурные затраты на ассоциативный накопитель 17. После появления единичного сигнала на выходе 40 формирователя 14 блок 15 переходит к четвертому этапу контроля, при котором формирователь 14 формирует множество А2 адресов, а формирователь 12 -единичное СЛОВО и выполняются операции контроля, аналогичные третьему этапу контроля. Всего в процессе контроля выполняется восемь таких этапов. В таблице отражены виды и последовательность этих этапов. После окончания восьмого этапа появление сигнала на выходе формирователя 14 блок 15 организует перезапись информации из .накопителя 8 в основной накопитель 5 по адресс1М, формируемым формирователем 14. Затем блок 15 сигналом на выходе , 2 организует повторное обращение к акопителю 5 по адресу, установлен- , ОМУ на регистре 1, и ассоциативный

поиск в накопителе 17. При обнаружении кода адреса, соответствующего коду адреса регистра 1, в накопителе 17 на его информационных выходах появляется код ошибки, KOTopfctfi дешифрируется даиифратором 18 и поступает ка регистр 10, т.е. происходит исправление значений дефектных разрядов слова и верное значение информации выдается на выход 20 устройства.

Технико-экономическсзе преимущество предлагаемого устройства заключается в том, что оно позволяет без использования внешней ЦВМ увеличиват мощность корректирующего кода, обеспечивая контроль и корректирование информации без уменьшения информационной емкости, за счет чего повышаются его надежность и информационная емкость по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU945904A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

А1

Нулевое

А2 Единичное Л2

t/ Al Нулевое Al

Единичное А2

А2

Единичное Д1

А1

А2 Нулевое

Единичное Al

Al

А 2 Нулевое Формула изобретения Запоминающее устройство с самокон тролем, содержащее основной накопитель , адресные входы и разрядные вхо ды и выходы которого соединены соответственно с выходами Основного адресного блока и с выходами и входами основного разрядного блока, первый дешифратор, основной регистр слова, блок коррекции ошибок, блок управления, дополнительный накопитель, адресные входы и разрядные входы и выходы которого подключены соответстве но к выходам дополнительного адресно го блока и к выходам и входам дополнительного разрядного блока, причем одни из выходов первого дешифратора подключены к входам основного адресного блока, а другой выход подключен к входам дополнительного адресного блока и адресному входу блока коррек

Запись по Al Запись по А2 Считывание по Al Считывание по А2

Запись по Al

Запись по А2

Считывание по Al

Считывание по А2 дни ошибок, управляюдие вход и выход которого соединены с первыми выходом и входом блока управления, а информационные вход и выход - с выходами и входами основного разрядного блока и одними из информационных выходов и входов основного регистра слова, другие информационные входы и выходы которого являются входами и выходами устройства, отлич ающееся тем, что, с целью повышения надежности и увеличения информационной емкости устройства, в него введены ассоциативный накопитель, формирователь адресных сигналов, схема сравнения, формирователь тестовых сигналов, дополнительный регистр слова, шифратор, второй дешифратор и регистр гшреса, .выходы которого соединены с входами первогЬ дешифратора и адресными входами ассоциативно о накопителя, управляющий выход которого подключен К второму входу блока управления, а информационные входы и выходы соединены соответственно с выходами шифратора и с входами дешифратора, выход которого подключен к первому управляющему входу основного регистра слова, второй управлякщий вход которого соединен с вторым выходом блока управления и управлякяцим входом регистра адреса, одни из выходов которого подключены к одним из входов формирователя адресных сигналов, дру гой вход и выход которого соединены с третьими выходом и входом блока управления, четвертый выход которого подключен к управляющему входу допол нительного регистра слова, одни из входов и выходов которого соединены с выходами и входами дополнительного разрядного блока, другие вход и выfutiход дополнительного регистра слова подключены соответственно к первому входу схемы сравнения и выходам основного разрядного блока и к входам основного разрядного блока, второму входу схемы сравнения и выходам формирователя тестовых сигналов, вход которого соединен с пятым выходом блока управления7 шестой выход которого подключен к третьему входу схеьвл сравнения, выход которой соединен с входом шифратора. Источники информации, принятые во внимание при экспертизе 1. Патент США 3562709, кл. 340-146.1, опублик. 1968. 2. Авторское свидетельство СССР Я 618799, кл. G 11 С 29/00, 1978 (прототип).

Авторы

Даты

1982-10-30—Публикация

1981-04-16—Подача