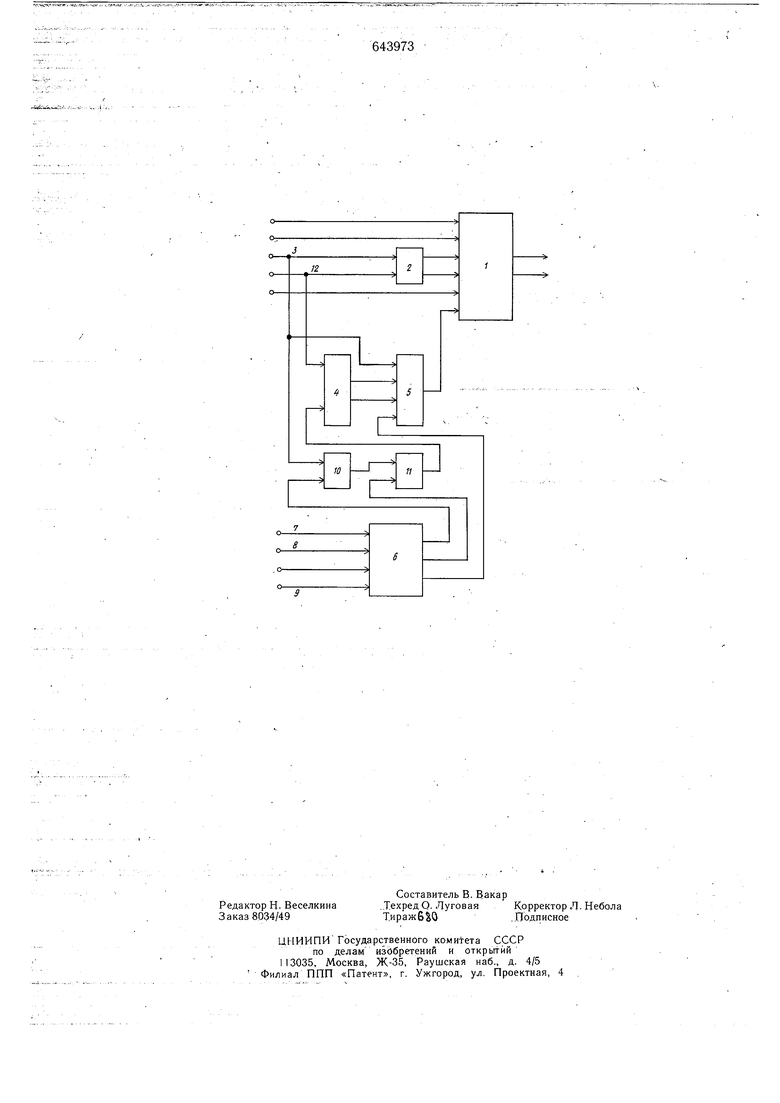

(54) УСТРОЙСТВО ДЛЯ УПР НА ЗАПОМИНАЮЩИХ Э СЧИТЫВА Изобретение относится к области вычислительной техники, в частности к устройствам управления,и может быть использовано в системах отображения, передачи и обработки дискретной информации. Известно устройство для управления накопителем на запоминающих элементах с неразрушающим считыванием информации, содержащее непрерывно работающий адресный счетчик считывания, регистр адреса записи и блок сравнения кодов регистра адреса записи и адресного счетчика считы-. вания, выход которого соединен с накопителем 1. Наиболее близким по т;ехническому рещению к предлагаемому является устройство для управления накопителем, содержащее адресный счетчик считывания, выходы которого соединены с соответствующими входами накопителя, щину первого такта и установочную щину, подключенные к соответствующим входам адресного счетчика считывания 2./ Недостатком указанных устройств для управления накопителем является их сложность вследствие необходимости специального регистра адреса записи, устройства ЕНИЯ НАКОПИТЕЛЕМ ЕНТАХ С НЕРАЗРУШАЮЩИМ М ИНФОРМАЦИИ срав нения кодов и схем образования кода адреса запйсъшаемого числа. Кроме того в данных устройствах усложнены выработка адреса записи следующего знаКа (маркера) и управление им с помощью сигналов редактирования. Целью изобретения является повышение надежности и упрощение устройства. Эта цель достигается за счет того, что устройство для управления накопителем на запоминающих элементах с неразрущаю считыванием информации содержит счетчик записи, первый элемент И, второй элемент И, элемент ИЛИ, формирователь, щины записи, редактирования и второго такта, при этом выход- первого элемента И подключен к соответствующему. входу накопителя, первый вход - к щине первого такта, второй и третий вход - к соответствующим выходам счетЧика записи, а четвертый вход - к третьему выходу формирователя, первый выход которого соединен со вторым входом второго элемента И, а второй выход - со вторым входом элемента ИЛИ, первый вход которого соединен с вь1х6дом второго элемента И, первый вход второго элемента И соединен с щиной первого такта, второй вход счетчика записи подключен к выходу элемента ИЛИ, а первый - к установочной шине, шины записи, редактирования и второго такта подключены к соответствующим входам формирователя. Устройство (см. чертеж) содержит накопитель на запоминающих элементах с неразрушаюшим считыванием информации 1, адресный счетчик считывания 2, шину первого такта 3, счетчик записи 4, первый элемент И 5, формирователь 6, шину второго такта 7, шину зациси 8, шину редактирования 9, второй элемент И 10, элемент ИЛИ 11, установочную шину 12. Устройство работает следующим образом. После подачи сигнала по установочной щине .12 адресный счетчик 2 считывания и счетчик 4 записи устанавливаются в одинаковое фазовое состояние и синхронно переключаются под воздействием тактовых импульсов, поступающих по шине первого такта 3. Коэффициенты счета обоих счетчиков равны.. При отсутствии сигнала записи на шине записи 8 с выхода первого элемента И 5 поступает на вход накопителя уровень напряжения, разрешающий считывание информации из него с каждым тактом по шине первого такта 3, и на выходе накопителя 1 появляется очередная считанная информация, хранящаяся в нем. При записи информации по шине записи 8 поступает синхросигнал записи, сопровождающий входную информацию, поступающую на накопитель I. Этот сигнал воздействует на формирователь 6, который вырабатывает сигнал, синхронизированный с импульсами второго такта, поступающими по шине второго такта 7. Этот сигнал, поступая на второй вход второго элемента И 10, запрещает прохождение одного импульса первого такта на первый вход счетчика записи 4. При этом фазовое состояние счетчика записи 4 изменится на один шаг по сравнению с фазовым состоянием адресноч го счетчика считывания 2. После окончания импульса с первого выхода- формирователя 6 на третьем выходе формирователя 6 появляется сигнал гхзрешения записи. При этом один раз за цикл обращения счетчика записи 4 на выходе первого элемента И 5 появляется сигнал, разрешающий запись информации в накопитель 1 по адресу, определяемому состоянием адресного счетчика считывания 2. При подаче очередного импульса записи по шине записи 8 формирователь 6 вырабатывает очередной импульс на первом выходе, поступающий на второй вход второ, .1. го элемента И 10 и запрещающий прохожде ние одного импульса первого такта в счетчик записи 4. При этом фаза счетчика записи 4 изменяется еще на один щаг по сравнению с фазовым состоянием адресного счетчика считывания 2. Сигнал с третье-, го выхода формирователя 6 разрещает выработку первым элементом И 5 импульса, поступающего на вход накопителя 1 и разрешающего запись очередной информации по адресу, соседнему с адресом предыдущего записанного числа. Дальнейшая работа устройства для управления накопителем происходит аналогично. С приходом каждого синхроимпульса записи по шине записи 8, сопровождающего входную информацию, поступающую на, накопитель 1, фаза счетчика записи 4 изменяется на один щаг (отстает) по сравнению с фазой адресного счетчика считывания 2 и запись информации происходит по очередному соседнему адресу. При необходимости произвольного изменения фазового состояния счетчика записи 4. и, значит, произвольного выбора адреса записи информации используются сигналы, поступающие по шинам редактирования 9 формирователя 6. Под воздействием этих сигналов на формирователь 6 на первом или втором выходе формирователя появляются сигналы, изменяющие фазовое состояние счетчика записи 4. При этом на третьем выходе формирователя 6 сигнал разрешения записи не появляется. Сигналы с первого выхода формирователя 6 поступают на второй вход второго элемента И 10 и не разрешают прохождение одного или нескольких импульсов первого такта в счетчик записи 4. При этом фаза счетчика записи 4 изменяется на один или несколько шагов по сравнению с фазой адресного счетчика считывания 2, аналогично изменению фазы, происходящему при записи информации (фаза счетчика записи 4 отстает на один или несколько шагов по сравнению с фазой адресного счетчика считывания 2). Сигналы со второго выхода формирователя 6 представляют собой импульсы второго такта и через элемент ИЛИ 11 поступают на второй вход счетчика записи 4. При этом фаза счетчика записи 4 изменяется на один или несколько шагов по сравнению с фазой адресного счетчика считывания 2, причем в этом случае она опережает на один или несколько (в зависимости от числа добавочных импульсов второго такта) шагов фазу адресного счетчика считывания 2, Так как при прохождении сигналов по шинам реда тирования 9 формирователь б не вырабатывает сигнал разрешения записи на третьем вйходе, на входе накопителя ,1 сигналь записи не появляются и ин-. формация, записанная в накопителе, не нарушается. . . Такоепостроение устройства позволяет значительно сократить количество оборудования, поскольку отпадает необходимость в

регистре адреса, схемах, совпадения кодов, схемах выработки адреса записи и др. Особенно упрощается устройство для управления накопителем в дисплеях.

Для выработки маркерного сигнала к выходам разрядов снетчика записи 4 необходимо подключить элемент И (на чертеже не показан).

Моменты срабатывания этого элемента И выбираются такими, чтобы они указывали место записи последующей информации. С помощью сигналов редактированияпри визуальном контроле маркерного сигнала легко осуществляется редактирование записанной информации. Для этого просто осущест-, вляется пощаговый (добавление или вычитание одного тактового импульса в счетчик записи 4) или построчный (добавление или вычитание тактовых импульсов по количеству равных количеству знаков в одной строке) сдвиг маркера.

Следует отметить, что счетчик записи 4 можно использовать также для выборочного или последовательного считывания информации в дополнительный регистр памяти из накопителя 1. Для этого необходим дополнительный переключатель (на чертеже не показан), вход которого соединен с выходом первого элемента И 5, один выход - со входом накопителя 1, а второй выход - с входом дополнительного регистра памяти (на чертеже не показан) . Сигнал считывания поступает на вход формирователя 6 и управляющий вход переключателя. При этом при поступлении сигнала считывания изменяется фаза счетчика записи 4 на шаг, а сигнал с выхода первого элемента И 5 поступает не на управляющий записью вход накопителя 1, а осуществляет запись выходной информации с выходных шин накопителя 1 в дополнительный регистр памяти. Далее, эту информацию можно использовать, например, для передачи в линию или для распечатки данного знака печатающим устройством.

Формула изобретения

Устройство для управления накопителем

на запоминающих элементах с неразрушаюшим считыванием информации, содержащее адресный счетчик считывания, выходы которого соединены с соответствующими входами накопителя, шину первого такта и установочную шину, подключенные к соответствующим входам адресного счетчика считывания, отличающееся тем, что, с целью повышения надежности и упрощения устройства, оно содержит счетчик записи, первый и второй элементы И, элемент ИЛИ, формирователь, шины записи, редактирования и второго такта, при этом выход первого элемента И подключен к соответствующему входу накопителя, первый вход - к шине первого такта, второй и третий вход - к соответствующим выходам счетчика записи, а четвертый вход - к третьему выходу формирователя, первый выход которого соединен со вторым входом второго элемента И, а второй выход - со вторым входом элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, первый вход второго элемента И соединен с шиной первого такта, второй вход счетчика записи подключен к выходу элемента ИЛИ, а первый - к установочной щине, шины записи, редактирования и второго

такта подключены к соответствующим входам формирователя.

Источники информации, принятые во внимание при экспертизе

1. Одуло В. Д. и др. Полупроводниковая буферная память системы отображения алфавитно-цифровой информации. -«Вопросы радиоэлектроники, сер. ЭВТ, 1975, вып. 12.

2. Самойлов Л. К. Устройства задержки информации в дискретной технике. М., «.Сов. радио, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1979 |

|

SU851491A1 |

| Буферное запоминающее устройство | 1977 |

|

SU720507A1 |

| Буферное запоминающее устройство | 1981 |

|

SU993333A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Запоминающее устройство для телеграфного аппарата | 1982 |

|

SU1200343A1 |

| Буферное запоминающее устройство | 1974 |

|

SU493805A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1019492A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

Авторы

Даты

1979-01-25—Публикация

1976-07-22—Подача