(54) ДИНАЛ ИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

| Динамический элемени памяти | 1976 |

|

SU627541A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU347797A1 |

| Элемент памяти | 1986 |

|

SU1388947A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

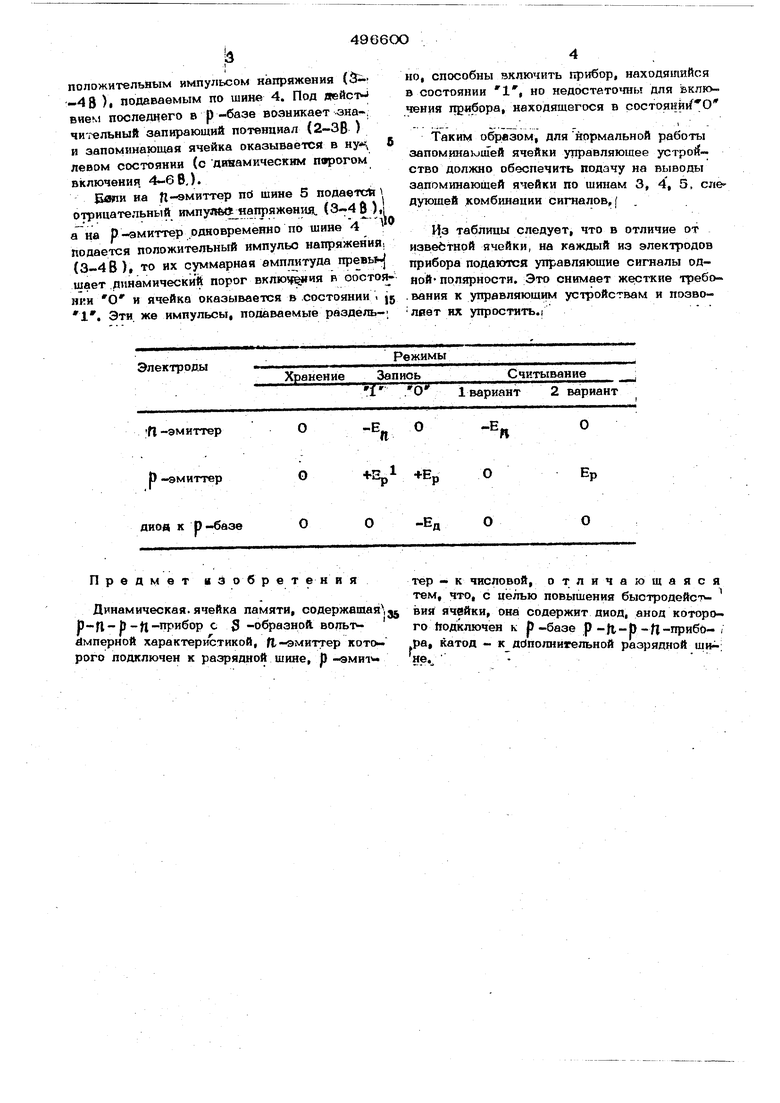

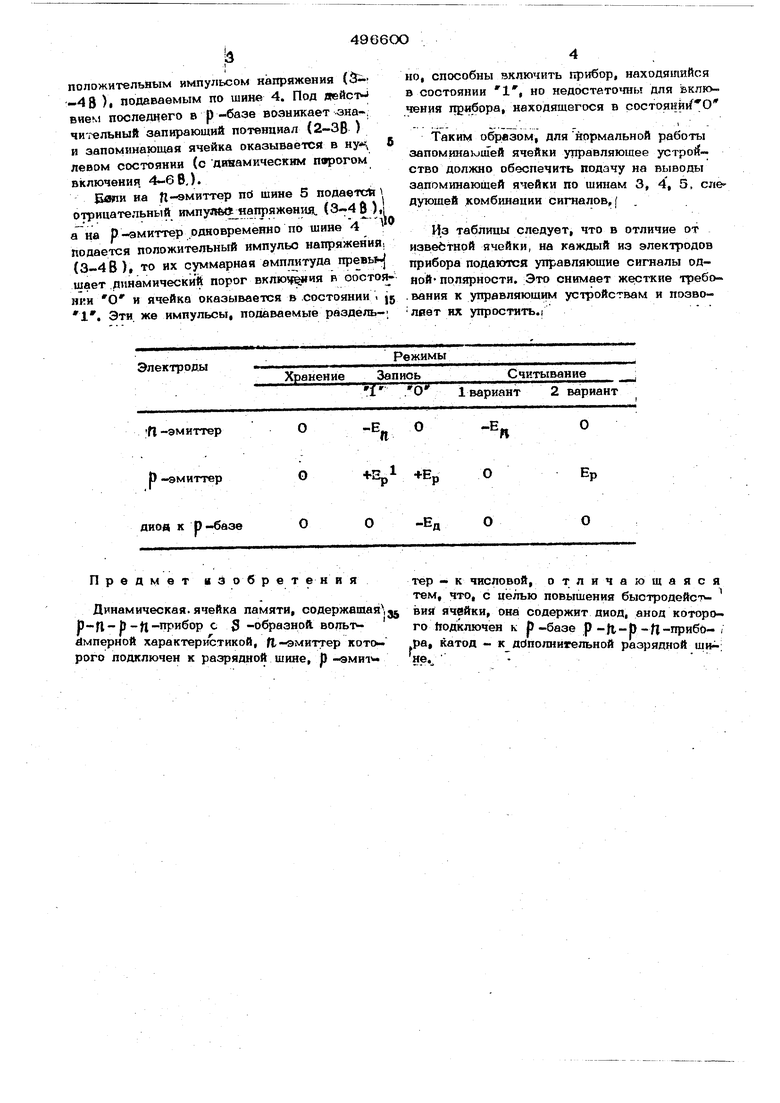

; Изобретение относится к вычислительной ;технике и (.ожет быть использовано в запоминающих устройствах и в устройствах цифровой автоматики. Известна интегральная мвтршш накопителя запоминающего устройства, ячейки котофого состоят из полупроводникового p-tl-P-tl-1фибора о S -| бразной вопьтамперной характеристикой, ft -эмиттер которого подсоединен к разрядной шине, а :р -эмиттер к числовой шине., Однако известная динамическая ячейка памяти характеризуется тем, что цикл изменения инфоркшпит включает операцию сти}эанйя целого слова накопителя и операцйго записи в выбранные ячейки этого же олова. Это уменьшает быстродействие запоминающего устройства. Целью изобретения является повышение быстродействия ячейки. Для этого она содержит диод, анод кото,рого подключен к р -базе р - fj- р - д-прибора, катод - к дополнительной разрядной шине. На чертеже приведена схема ячейки. iДинамическая ячейка памяти содержит полупроводниковый Д -р-fl р-прибор 1 ,с g -образной Больгамперной характеристИ кой, р -база которого через диод 2 поцсое™ динена к шине 3, р -эмиттер и П -эмиттер прибора подсоединены к шннаь 4 и 5, соответственно. Составляющий fi - р П-транзистор, как и в известной ячейке, выполнен с большим коэ41фициентои усиления по току и с минимальными утечками; диод-2 также выполнен с минимальной утечкой так, что потенциал, зашфающий p-f -переходы 6, 7, 8 может сохраняться продолжительное время (около 1Осек}. Кроме того, ячейка содержит конденсаторы 9-12. Ячейка работает следующим обрезом. Отрицательнь й импулт д напряжения (1-25) подаваемый по шине 3 через диод 2 на р-базу, запирает ее потенциалом (О,5-l6 ), недостаточным для перевода ячейки из единичного в нулевое-состояние. Ошшко его амплитуда достаточна, чтобы заблоки;ровать открывание ft р-П- P эиcтopa.. положительным импульсом напряжения ( В ) I подаваемым по шине 4. Под яейст вием последнего в р -базе возникает зна-, чи-гельный запирающий потенциал (2-ЗВ ) и запоминающая ячейка оказывается в ну«, левом состоянии (с динамическим порогом включения. 4-6В,). Бели на Ц-эмиттер nd шине 5 подается отрицательный импуябв1напряжения. (3-.46 )J а на р-эмиттер одновременно по шине 4 подается положительный импульо напряжения. (3-4В )| то их суммарная амплитуда превы-j шает динамический порог вклю р ия в оостоя; НИИ О и ячейка оказывается в .состоянии - |5 1, Эти же импульсы, подаваемые раздепь-;

р -эмиттер

диоя к р-базв Предмет изобретения Динамическая, ячейка памяти, содержашая p-fl-p-tl-прибор с 3 -образной, вольтАмперной характеристикой, fl-эмиттер котоd4n«M-.ur% п,«.-.--..Си. « рого подключен к разрядной щине, р -эми

О

-Е

О

д но, способны включить прибор, находящийся в состоянии , но недостетошы для ъкпючения прибора, находящегося в состояни О - - .,,. -,..Таким обрезом, для нормальной работы запоминающей ячейки управляющее устройство должно обеспечить подачу на выводы запоминающей ячейки по щинам 3, 4, 5, сле дующей комбинации сигналов, f . Из таблицы следует, что в отличие от изв ейтнрй ячейки, на каждый из электродов прибора подаются управляющие сигналы одной-полярности. Это снимает жесткие требо. вания к управляющим устройствам и позволвет их упростить.1 тер - к числовой, отличающаяся тем, что, с целью повышения быстродейст вия ячейки, она содержит диод, анод которого Подключен к р-базе р-Ц - р-Ц-прибопо. г ™.---Л- .... ра, катод - к дьполнигельной разрядной

111

L.

J

tf,

irv.

0

XT.

3

/2

Авторы

Даты

1975-12-25—Публикация

1972-07-06—Подача