Изобретение относится к полупроводниковым схемам памяти на биполярных транзисторах, может быть использовано в различных устройствах /фанения информации.

Известны динамические элементы памяти (ДЭП) на биполяиных полупроводниковых приборах 1. В каждом из них информация хранится в виде заряда на емкости обратносмещенного р-ц-перехода,

Наиболее близок к предлагаемому динамический элемент памяти, содержащий ц-р-м транзистор, эмиттер которого сое динен со словарной шиной, коллектор - с разрядной шиной, а база - с катодом

диода, причем анод диода соединен с адресной шиной 2.

Для управления этим ДЭП используются трк шины с большим количеством пересечений, нто снижает надежность

элемента и увеличивает габариты запоминающего устройства (ЗУ).

Цель изобретения - повышение надежности элемента. Достигается она тем, чт

анод диода подключен к эмиттеру транзистора.

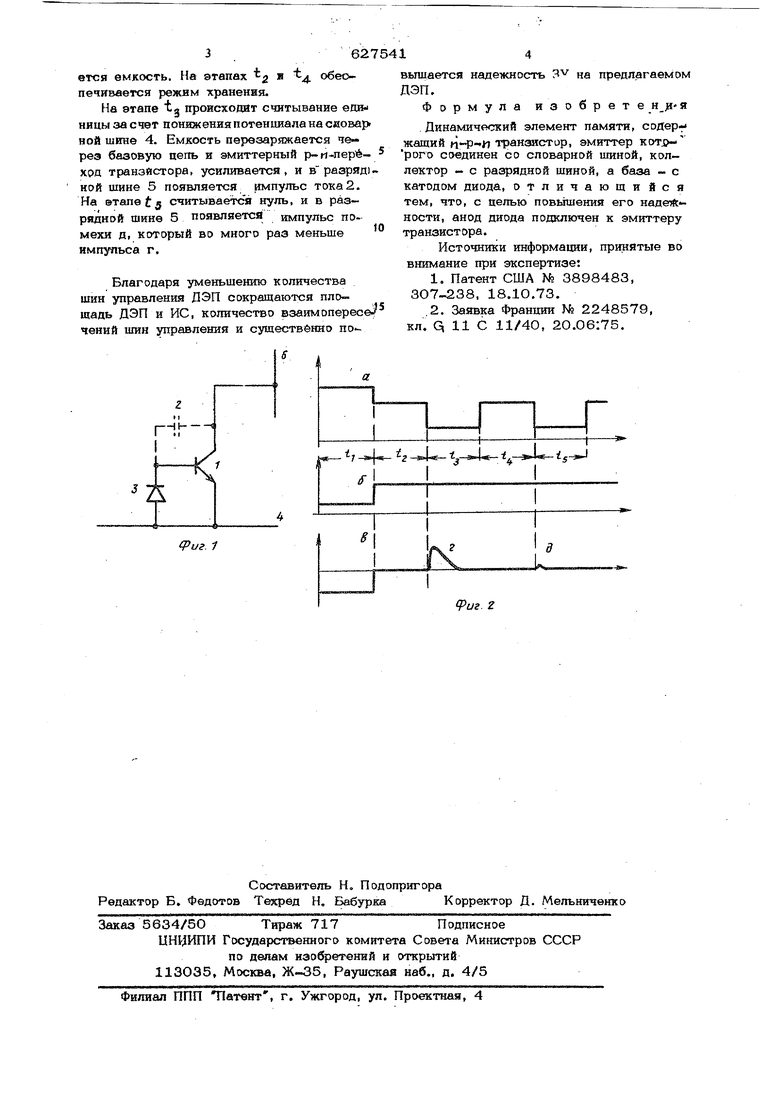

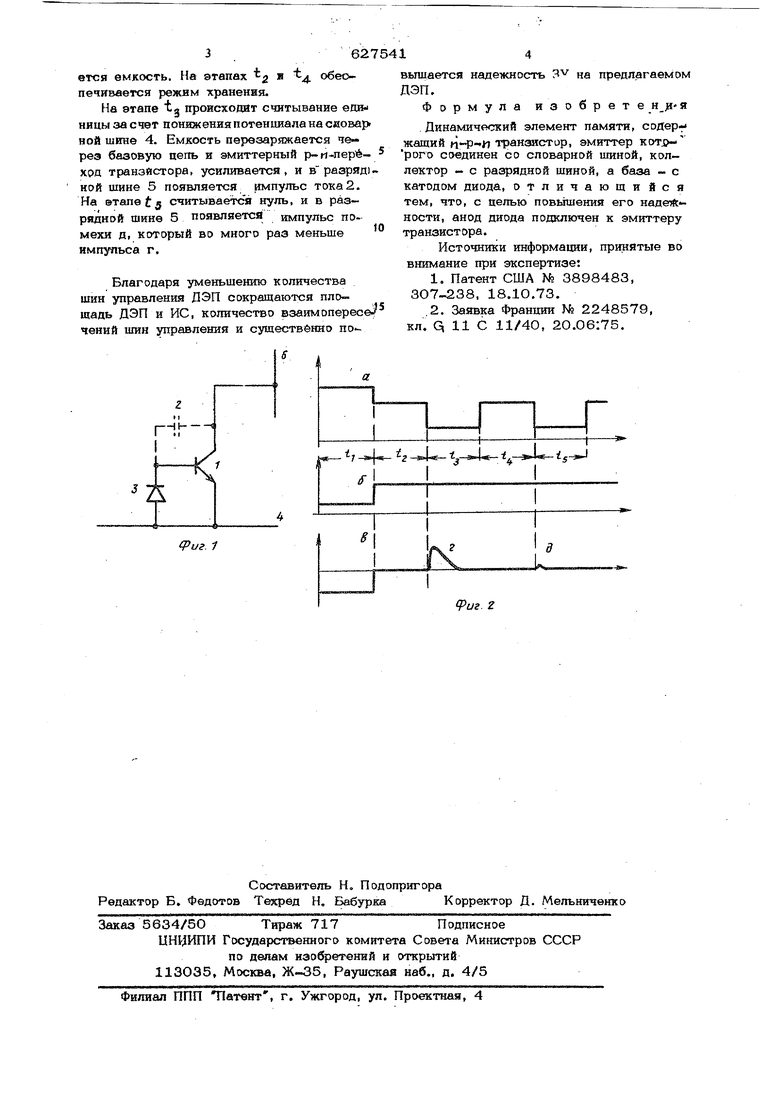

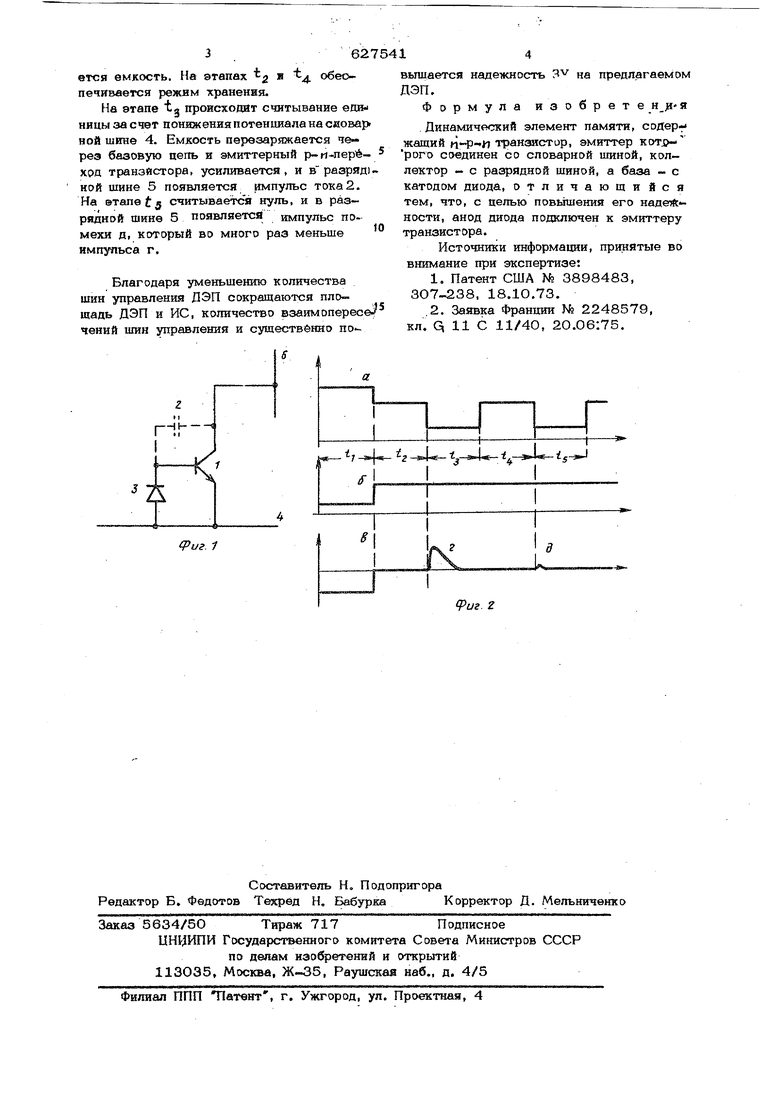

На фиг. 1 представлена принципиальная электрическая схема предлагаемого ДЭП, на фиг. 2 - временная диаграмма его работы.

ДЭП содержит и-р-п транзистор 1, барьерную емкость 2 базо-коллекторного р-п-перехода (емкость хранения), диод 3, словарную шину 4, разрядную шину 5 К словарной шине подключены эмиттер транзистора и анод диода; катод диода подключен к базе транзистора, а коллектор последнего - к разрядной шине.

На диаграмме обозначены :Q - изменение напряжения на словарной шине 4| б - изменение напряжения на разрядной шине 51 в - изменение тока в разрядной шине 5.

Предлагаемый элемент памяти работает следуюшим образом.

На этапеt(записывается единица. В этэ время повышается напряжение на слвари эй шине 4 и понижается на разрядной шине 5, открывается диэд и заряжа- втся емкость. На этапах Д обеопечявавтся режим хранения. На этапе tg происходят считывание единицы за с чет понижения потенциала на сиовар ной шине 4. Емкость перезаряжается через базовую цепь и эмиттерный p-n-nepifeход транзистора, усиливается, и вразрящ ной шине 5 появляется импульс тока2. На этапе t считываетс-я нуль, и в раз рядной шине 5 появляется импульс помеки д, который во много раз меньше импульса г. Благодаря уменьшению количества шин управления ДЭП сокращаются площадь ДЭП и ИС, количество взаимопересе чений иган управления и существенно повышается надежность 3 на предлагаемом ДЭП. Формула изобрете я Динамический элемент памяти, содержащий транзистор, эмиттер KOTJ рого соединен со словарной шиной, коллектор - с разрядной шиной, а база - с катодом диода, отличающийся тем, что, с целью повьгаения его надвА«ности, анод диода подключен к эмиттеру транзистора. Источники информации, принятые во внимание при экспертизе: 1. Патент США N 3898483, 307-238, 18.10.73. .2. Заявка Франции NQ 2248579, кл, q 11 С 11/40, 20.06:75.

г

11

I-II

I II

иг. 1

Сриг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Полупроводниковый элемент памяти | 1980 |

|

SU942150A1 |

| Элемент памяти | 1981 |

|

SU978328A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

Авторы

Даты

1978-10-05—Публикация

1976-05-11—Подача