ла поиска соседней ячейки коммутации. Выход собирательного элемеита «ИЛИ подключен к входу блока управления и первому входу первого элемента «ИЛИ схемы памяти, второй вход которого связа-н с общей для решающих блоков шиной установки триггера управления схемы помяти, а выход - с единичным .входом того же триггера управления, единичный выход которого соединен с первыми входами первого и второго элементов «И схемы памяти. Вторые входы этих элементов соединены соответственно с настроечной и ключевой шинами структуры, выход первого элемента «И схемы памяти - с входом регистра кода операций схемы управления и с входом ввода начальных значений интегратора, а выход второго элемента «И схемы памяти - с первым входом ее второго элемента «ИЛИ, выход которого подключен к входу регистра схемы памяти. Выход этого регистра подсоединен к второму входу второго элемента «ИЛИ и к первому входу элемента сравнения схемы памяти, второй вход которого соединен с ключевой шиной, а третий вход - с шиной разрешения сравнения, соединенной через инвертор с третьим входом второго элемента «И схемы памяти.

Выход элемента сравнения связан с первым входом третьего элемента «ИЛИ той же схемы, второй вход которого соединен с общей шиной установки триггеров управления в нулевое состояние, а выход - с нулевым входом триггера управления той же схемы памяти.

Это позволяет неявным вложением графазадачи в структуру обеспечить обход неисправных ячеек коммутации и интеграторов, повысить надежность ее функционирования и сократить число-шин управления.

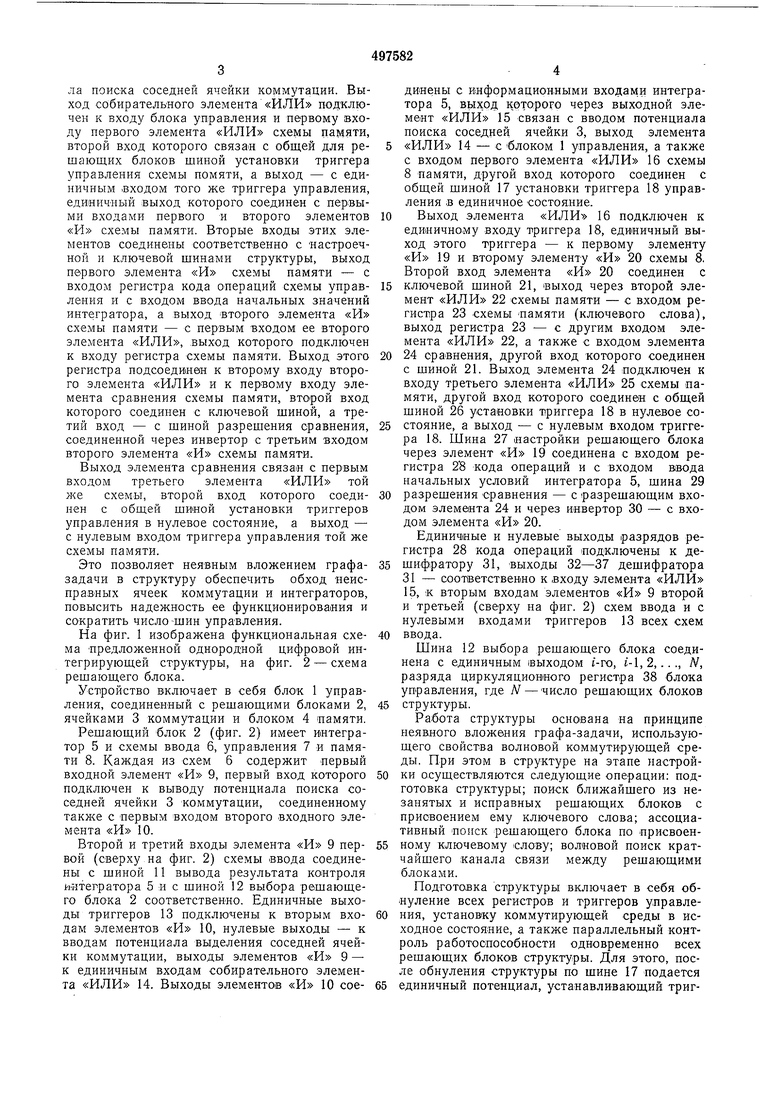

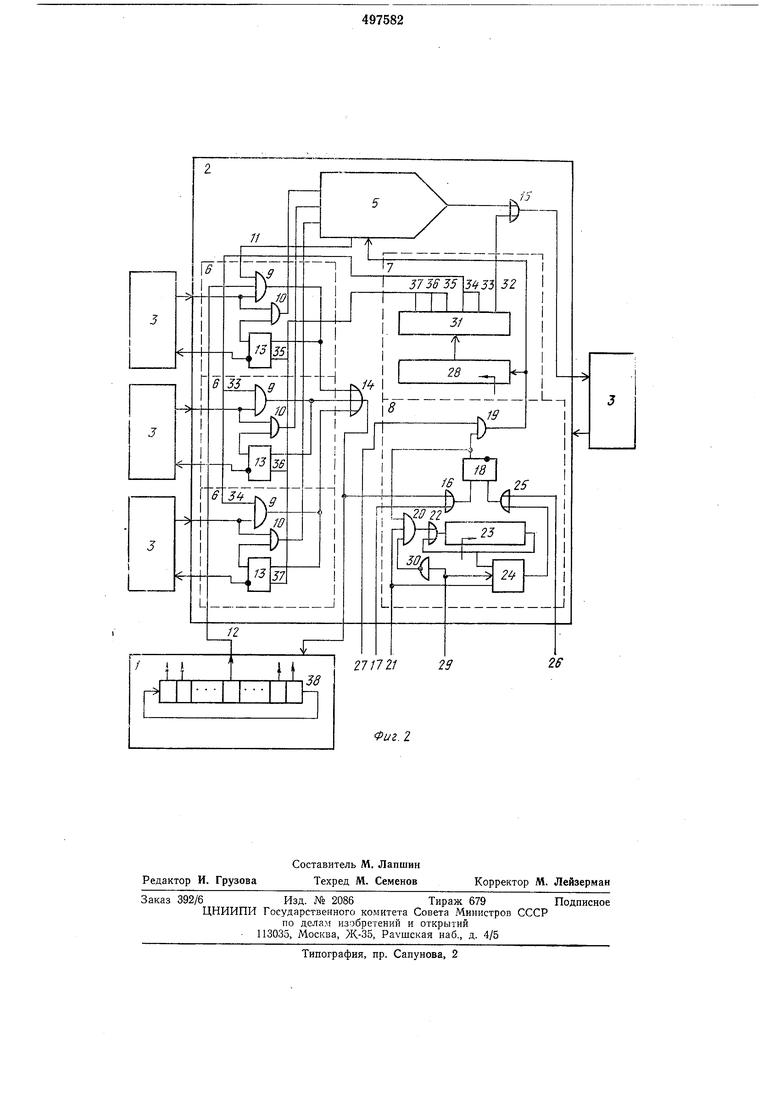

На фиг. 1 изображена функциональная схема предложенной однородной цифровой интегрирующей структуры, на фиг. 2 - схема решающего блока.

Устройство включает в себя блок 1 управления, соединенный с решающими блоками 2, ячейками 3 коммутации и блоком 4 памяти.

Решающий блок 2 (фиг. 2) имеет интегратор 5 и схемы ввода 6, управления 7 и памяти 8. Каждая из схем 6 содержит первый входной элемент «И 9, первый вход которого подключен к выводу потенциала поиска соседней ячейки 3 коммутации, соединенному также с первым входом второго входного элемента «И 10.

Второй и третий входы элемента «И 9 первой (сверху на фиг. 2) схемы ввода соединены с шиной 11 вывода результата контроля и-нтегратора бис шиной 12 выбора решающего блока 2 соответственно. Единичные выходы триггеров 13 подключены к вторым входам элементов «И 10, нулевые выходы - к вводам потенциала выделения соседней ячейки коммутации, выходы элементов «И 9 - к единичным входам собирательного элемента «ИЛИ 14. Выходы элементов «И 10 соединены с информационными входам.и интегратора 5, выход которого через выходной элемент «ИЛИ 15 связан с вводом потенциала поиска соседней ячейки 3, выход элемента «ИЛИ 14 - с -блоком 1 управления, а также с входом первого элемента «ИЛИ 16 схемы 8 памяти, другой вход которого соединен с общей шиной 17 установки триггера 18 управления в единичное состояние.

Выход элемента «ИЛИ 16 подключен к единичному входу триггера 18, единичный выход этого триггера - к первому элементу «И 19 и второму элементу «И 20 схемы 8, Второй вход элемента «И 20 соединен с

ключевой шиной 21, выход через второй элемент «ИЛИ 22 схемы памяти - с входом регистра 23 схемы -памяти (ключевого слова), выход регистра 23 - с другим входом элемента «ИЛИ 22, а также с входом элемента

24 сравнения, другой вход которого соединен с шиной 21. Выход элемента 24 подключен к входу третьего элемента «ИЛИ 25 схемы памяти, другой вход которого соединен с общей шиной 26 установки триггера 18 в нулевое состояние, а выход - с нулевым входом триггера 18. Шина 27 настройки решающего блока через элемент «И 19 соединена с входом регистра 28 кода операций и с входом ввода начальных условий интегратора 5, шина 29

разрешения сравнения - с разрешающим входом элемента 24 и через инвертор 30 - с входом элемента «И 20.

Единичные и нулевые выходы разрядов регистра 28 кода операций подключены к дешифратору 31, выходы 32-37 дешифратора 31 - соответственно к входу элемента «ИЛИ 15, к вторым входам элементов «И 9 второй и третьей (сверху на фиг. 2) схем ввода и с нулевыми входами триггеров 13 всех схем

ввода.

Шина 12 выбора решающего блока соединена с единичным выходом 1-го, t-1,2,..., N, разряда циркуляционного регистра 38 блока управления, где N-число решающих блоков

структуры.

Работа структуры основана на принципе неявного вложения графа-задачи, использующего свойства волновой коммутирующей среды. При этом в структуре на этапе настройки осуществляются следующие операции: подготовка структуры; поиск ближайшего из незанятых и исправных решающих блоков с присвоением ему ключевого слова; ассоциативный поиск решающего блока по присвоенному ключевому слову; волиовой поиск кратчайшего канала связи между решающими блоками.

Подготовка структуры включает в себя обнуление всех регистров и триггеров управления, установку коммутирующей среды в исходное состояние, а также параллельный контроль работоспособности одновременно всех решающих блоков структуры. Для этого, после обнуления структуры по шине 17 подается

единичный потенциал, устанавливающий триггеры 18 всех решающих блоков в единичные состояния, и по настроечной шине 27 через открытый элемент «И 19 заносится контрольный тест в интеграторы 5. После отработки теста и сравнения ответа с контрольным кодом, храняшимся в интеграторе, принимается решение о его исправности. Если интегратор 5 испраБен, то по шине 11 вывода результата контроля выдается разрешение первому входному элементу «И 9 первой (сверху на фиг, 2) схемы б ввода ,на прием потенциала поиска. В противном случае интегратор не может быть выбран.

После этого единич«ьш потенциалом, подаваемым по шине 26, триггеры 18 всех решающих блоков устанавливаются в нулевые состояния.

Операция поиска ближайшего решающего блока с присвоением -ключевого слова осуществляется в предположении, что имеется или ранее выбранный решающий блок, или доступ к некоторым граничным ячейкам коммутации. В обоих случаях с выхода решающего блока или отмеченной ячейки коммутации посылается потенциал поиска и ищется ближайший решающий блок с последующим присвоением ему ключевого слова.

Пусть в предыдущем шаге настройки структуры уже был выбран один из решающих блоков. В его регистры 23 и 28 заносятся соответственно ключевое слово и код признака поиска ближайшего решающего блока. Ячейкам 3 коммутации со стороны-блока 1 управления выдается разрешение «а распространение волны потенциала поиска. После дещифрирования кода признака с выхода 32 дешифратора 31 через элемент «И 15 потенциал поиска прикладывается к входу соседней ячейки 3. Далее потенциал поиска волнообразно распространяется по ячейкам коммутации структуры, образуя дерево кратчайших каналов связи с несливающимися ветвями с корнем в вершине решающего блока - источника. Через время т, где t - время, необходимое для достижения волной потенциала поиска входов ближайших решающих блоков, образовавшееся дерево каналов связи записывается в память ячеек коммутации подачей соответствующей команды с блока управления.

В результате этого входы ячеек коммутации, которых не достигла волна потенциала поиска, обнуляются, и дальнейшее распространение волны прекращается. Таким образом, устанавливаются каналы связи между решаюшим блоком - источником и некоторым количеством ближайших решающ-их блоков.

В следующем шаге проводится произвольная выборка одного из них. Для этого по циркуляционному регистру 38 блока управления последовательно сдвигается «единица, прикладываемая в виде потенциала выбора по шине 12 к входу элемента «И 9 первой схемы ввода решающего блока, соответствующего номеру разряда регистра. При совпадении

потенциала выбора с потенциалом поиска и с сигналом исправности данного решающего блока элемент «И 9 открывается, и единичный потенциал поступает на единичный вход триггера 13 первой схемы 6 ввода, устанавливая его в единичное состояние. С единичного выхода триггера 13 снимается разрешение на подключение второго входного элемента «И 10 к выходу ячейки 3 коммутации, а с нулевого выхода снимается потенциал выделения, который распространяется по стволу дерева каналов связи к рещающему блоку - источнику, выделяя этот канал связи. Одновременно единичный потенциал с выхода элемента «И 9 через элемент «ИЛИ 14 поступает в блок управления, останавливая регистр 38, а через элемент «ИЛИ 16 - па единичный вход триггера 18, устанавливая его в единичное/состояние. Элементы «И 19 и 20 оказываются открытыми, и через них по шинам 27 и 17 заносится соответственно очередная команда в регистр 28 и ключевое слово в регистр 23. При необходимости, по шине 27 в интегратор 5 заносятся начальные условия.

Если в данном количестве решающих блоков не окажется исправного и незанятого, то после переполнения регистр 38 останавливается, все ячейки коммутации возвращаются в исходные состояния и поиск проводится сначала, пока волна потенциала поиска не достигнет исправного и незанятого решающего блока.

Когда возникает необходимость обращения к одному из ранее выбранных решающих блоков, с целью установки каналов связи по другим входам или для стирания ненужных каналов связи, то осуществляется операция ассоциативного поиска решающего блока по ключевому слову. Для этого по шине 17 подается единичный потенциал, устанавливающий триггеры 18 всех решающих блоков в единичные состояния, по щине 29 - единичный потенциал, который разрешает сравнение и после инверсии инвертором 30 закрывает элемент «И 20. Затем по шине 21 посылается ключевое слово искомого решающего блока, которое сравнивается поразрядно с хранимым в регистре 23 ключевым словом с помощью элементов 24 сравнения всех решающих блоков одновременно. Есть хоть в одном разряде произошло несовпадение, то на выходе данного элемента сравнения появляется единичный потенциал, устанавлнвающий триггер 18 в нулевое состояние.

Таким образом, в единичном состоянии остается только триггер 18 искомого решающего блока. Далее по шине 27 через открытый элемент «И 19 заносится необходимая команда в регистр 28.

В ТОМ случае если это - команда подключения второй или третьей схемы ввода решающего блока к каналу связи, то на выходе данного элемента сравнения образуется единичный потенциал, устанавливающий триггер 18 в нулевое состояние. Таким образом, в единичном состоянии остается только триггер 18 искомого решающего блока. Далее по шине 27 через открытый элемент «И 19 заносится необходимая команда в регистр 28.

ЕСли это - команда подключения второй или третьей схемы ввода решающего блока к каналу связи, то на выходе 33 или 34 дешифратора 31 появляется единичный потенциал, разрешающий -прием потенциала поиска элементом «И 9 соответствующей схемы ввода.

Когда это - команда стирания канала свяЗИ, подключенного к какой-либо схеме ввода, то на соотввтствующем из выходов 35-37 дешифратора 31 образуется единичный потенциал, который устанавливает триггер 13 этой схемы ввода в нулевое состояние. После этого подачей соответствующих кома-нд на ячейки коммутации канал стирается.

Операция волнового поиска кратчайшего канала связи необходима в том случае, когда устанавливается канал связи между двумя ранее выбранными решающими блоками. Сначала проводится операция ассоциативного поиска первого решающего блока и в его регистр 28 заносится команда подключения одной из схем б ввода. Затем ищется второй решающий блок, и в его регистр 28 заносится команда выработки потенциала поиска. Время поиска выбирается таким, чтобы волна потенциала поиска охватила всю структуру. При достижении искомого решающего блока, потенциал поиска через один из открытых элементов «И 9 устанавливает соответствующий триггер 13 в единичное состояние, выделяя, тем самым, канал связи, и далее через элемент «ИЛИ 14 поступает в блок управления, сигнализируя об окончании поиска.

Описанные операции обеспечивают неявное вложение графа-задачи любой конфигурации в однородную цифровую интегрирующую структуру. Процесс работы не отличается от соответствующих процессов известных устройствах.

Предмет изобретения

Однородная цифровая интегпир .ощая структура, содержащая решающие блоки, информационные входы и выходы решающих блоков соединены соответственно с выходами и входами соседних ячеек коммутации, блок памяти, входы я выходы которого соединены с выходами и входами блока управления, выполненного на циркуляционном регистре, выходы блоков управления и памяти соединены с управляющими входами ячеек коммутации, а каждый решающий блок содержит интегратор и схему управления, выполненную на дешифраторе, входы которого соединены с выходами регистра кода операции, отличающаяся тем, что, с целью повышения надежности И уменьшения числа щин управления, каждый решающий блок содерж1ит элементы «И, «ИЛИ, триггеры, инвертор, регистр и элемент сравнения, объединенные в схемы

ввода и в схему памяти, первые входы первого и второго элементов «И схем ввода каждого решающего блока соединены с выходами потенциала поиска соседних ячеек коммутации,

вторые входы первых входных элементов «И первой и второй схем ввода соединены с соответствующими .выходами дещифратора, второй и третий входы первого входного элемента «И третьей схемы ввода соединены соответственно с шиной вывода результата контроля интегратора и с шиной выбора решающего блока, соединенной с единичным выходом соответствующего разряда циркуляциониого регистра блока управления, выходы первых входных элементов «И соединены с входами собирательного элемента «ИЛИ и с единичными входами триггеров соответствующих схем ввода, единичные выходы которых соединены с вторыми входами соответствующих вторых входных элементов «И, выходы которых соединены с информационными входами интегратора, нулевые выходы триггеров, схем ввода соединены с входами потенциала выделения соседних ячеек коммутации, а нулевые входы соединены с соответствующими выходами дешифратора схемы управления, информационный выход интегратора соединен с первым входом выходного элемента «ИЛИ, второй вход которого соединен с выходом потенциала поиска дешифратора, а выход соединен с входом потенциала поиска соседней ячейки коммутации, выход собирательного элемента «ИЛИ соединен с входом блока управления и с первым входом первого элемента «ИЛИ Схемы памяти, второй вход которого соединен с обшей для решающих блоков щиной установки триггера управления схемы памяти, а выход соединен с единичным входом того же триггера управления, единичный выход которого соединен с первыми входами первого и второго элементов «И схемы памяти, вторые входы которых соединены соответственно с настроечной и ключевой шинами структуры, выход первого элемента «И схемы памяти соединен с входом регистра кода операций схемы управления и с входом ввода начальных значений интегратора, а выход второго элемента «И схемы памяти соединен с neipBbiM входом ее второго элемента «ИЛИ, выход которого Соединен с входом регистра схемы памяти, выход Которого соединен с вторым входом второго элемента «ИЛИ и с первым входом элеМбнта сравнения схемы памяти, второй вход -которого соединен с ключевой шиной, а третий вход соединен с шиной разрешения сравнения, соединенной через инвертор с третьим входом второго элемента «И схемы памяти, выход элемента срав-нения соединен с первым входом третьего элемента

«ИЛИ той же схемы, второй вход которого соединен с общей шиной установки триггеров управления в нулевое состояние, а выход соединен с нулевым входом триггера управления той же схемы памяти.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Коммутирующее устройство | 1973 |

|

SU478439A1 |

| АДРЕСУЕМАЯ ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ | 2010 |

|

RU2427033C1 |

| Устройство для информационного поиска | 1986 |

|

SU1399769A1 |

| Ячейка волновой коммутационной системы | 1985 |

|

SU1256011A2 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для коммутации информационных каналов | 1981 |

|

SU1003123A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

Авторы

Даты

1975-12-30—Публикация

1973-11-30—Подача