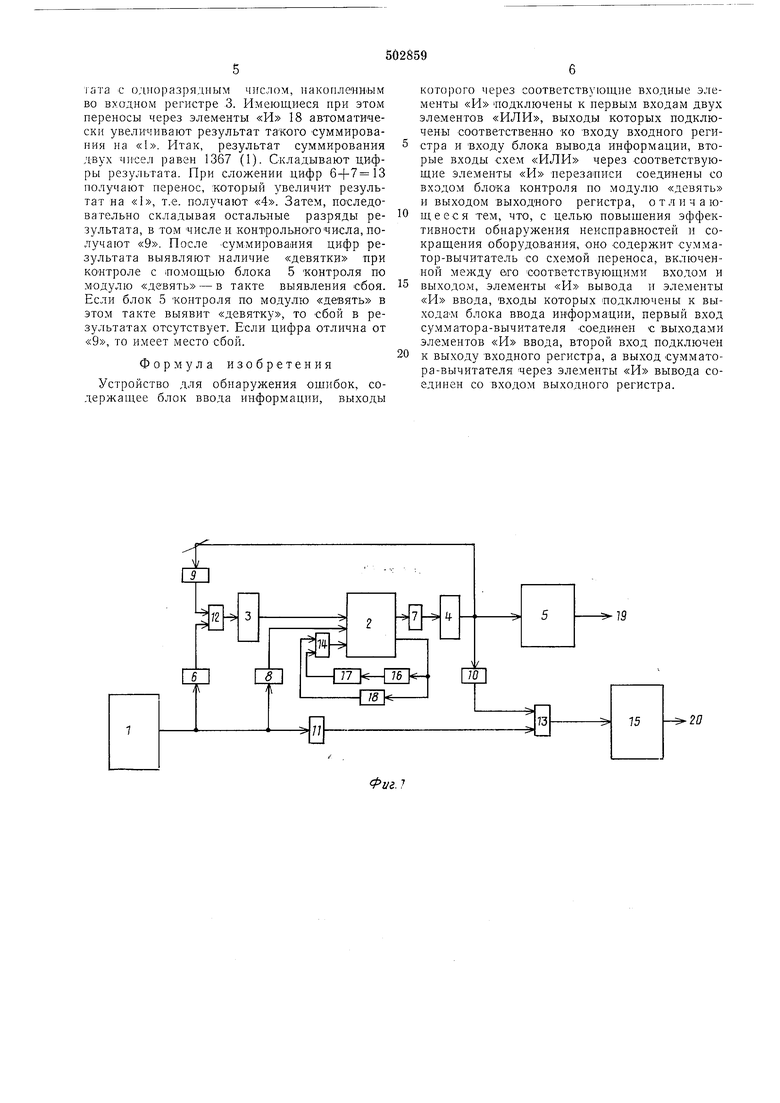

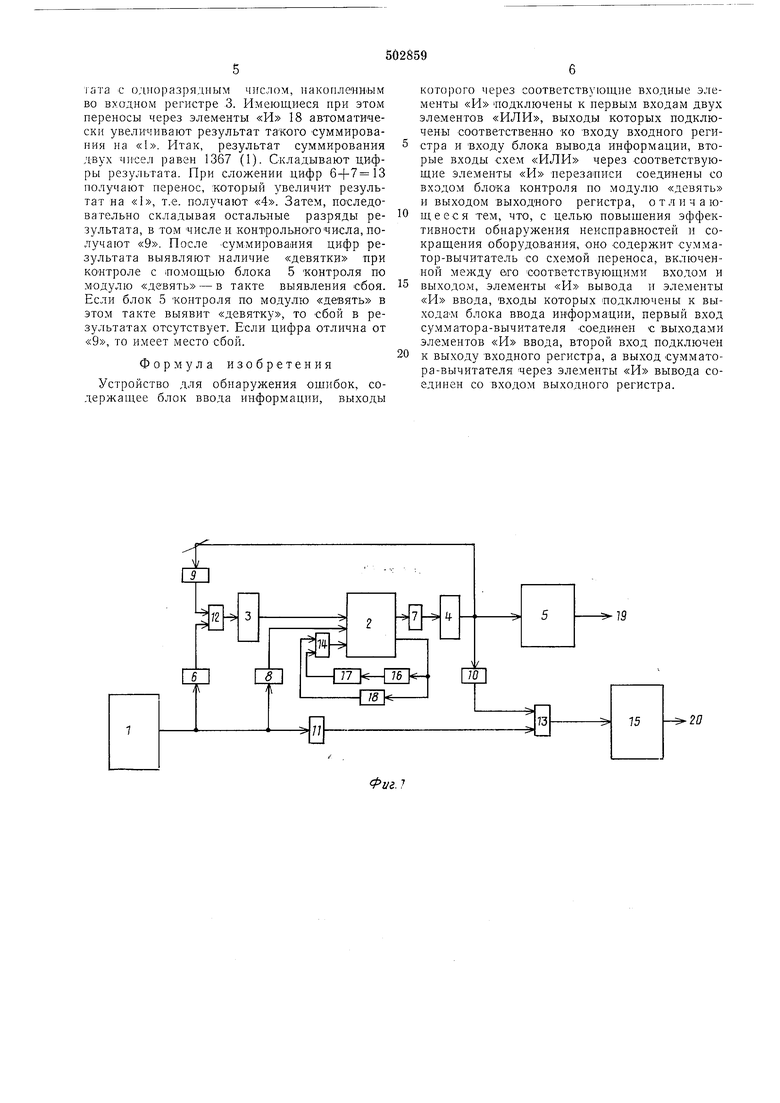

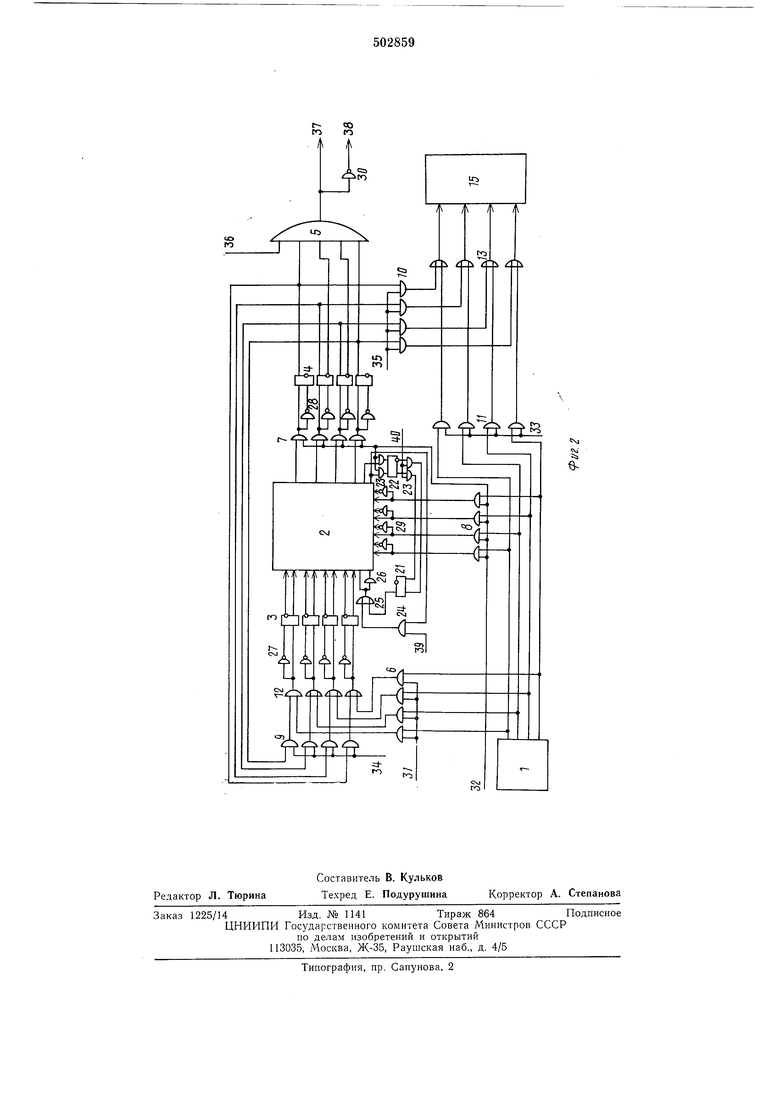

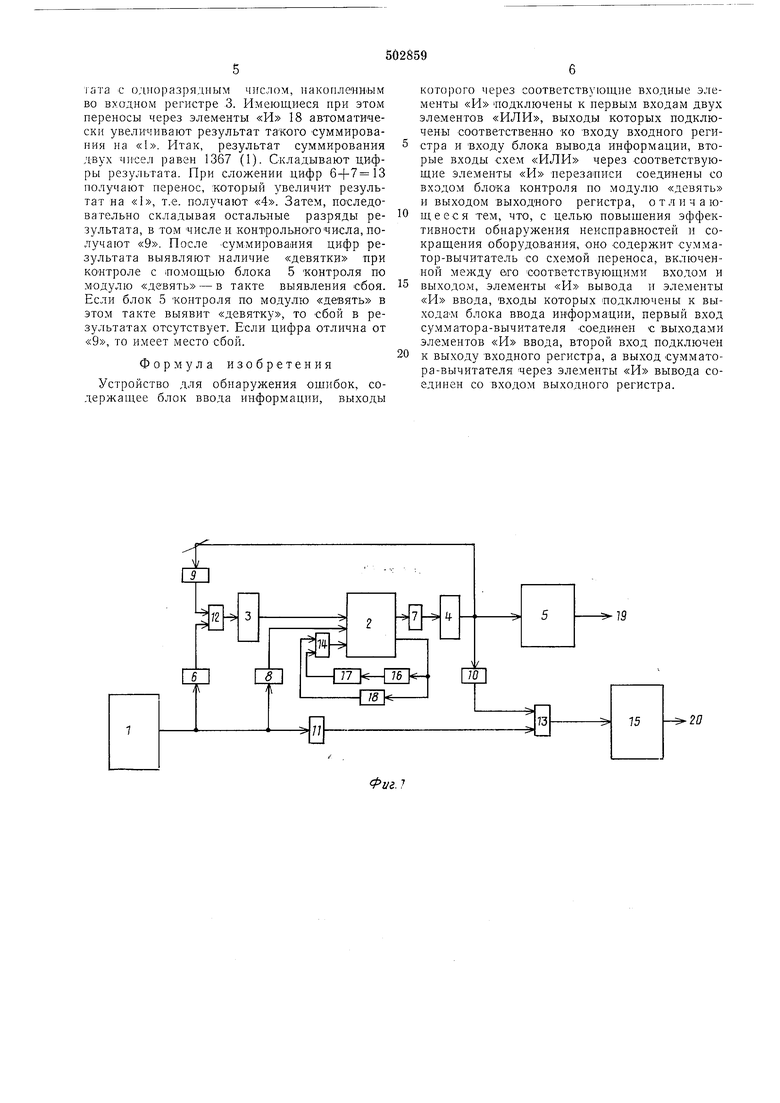

вых сигналов, элемент 30 выдает инверсию сигнала сбоя. На вход 31 подается стробирующий имнульсный потенциал ввода внформации во входной регистр 3 через элемент «И 6 и Собирательные схемы «ИЛИ 12. На вход 32 подается управляющий потенциал, стробирующий выдачу в сумматор-вычитатель 2 второго сла;гаемого и запись суммы или разности из сумматора-вычитателя 2 Б выходной регистр 4. На вход 33 подается управляющий потенциал непосредственной передачи чисел из блока ввода 1 в блок 15 вывода. На вход 34 подается управляющий потенциал перезаписи информации из выходного регистра 4 во входной регистр 3 через элементы 9 перезаписи и собирательные схемы «ИЛИ 12. Возможность перезаписи ннфор1мации из регистра 3 в регистр 4 обеспечивает непосредственное иакоПление одноразрядной разности или суммы при образовании контрольного числа-дополиения но модулю «девять или при контроле. Поразрядная выдача чисел в бло« 15 результата суммирования или вычитания или контрольного числа производится при подаче стробирующего потенциала «а вход 35. На вход 36 тодается управляющий потенциал контро ля для выделения сигнала сбоя на шинах 37 и 38. На вход 39 подаются стробирующие импульсы контроля при получении контрольных чисел или при операции над ними. На вход 40 подаются в такте переписи импульсы переноса в триггер 21, подаваемые при отсутствии операций над контрольными числами или при их образовании. Работа устройства при контроле обработки цифровой информации (см. фиг. 1). Обработка информации и арифметические онерации производятся блоками ввода 1 и вывода 15, сумматором-вычитателем 2, элемен.тами «И 6-11, элементами «ИЛИ 12 и 13. Сложение (вычитание) двух чисел осществляется этими узлами последовательно, разряд за разрядом первого числа с одноименными разрядами второго числа. При этом разряд первого числа в такте ii через элемент «И 6 и элемент «ИЛИ 12 подается во входной .регистр 3, который выдает его непосредственно на сумматор-вычитатель 2. В последующем такте через элементы «И 8 в сумматор-вычитатель 2 поступает одноименный разряд второго слагаемого. Образующаяся в такте второ.го слагаемого сумма (разность) при помощи элемента «И 7 записывается в выходной регистр 4. При этом переносы запоминаются в .элементе 16 переноса и передаются при суммировании последующих разрядов чисел. Результаты сложения (вычитания) в такте вывода через элементы «И 10 поступают из выходного регистра 4 в блок 15 вывода. Для контроля обработки информации и .проверки результатов арифметических операций предлагаемое устройство производит следующее. Получение контрольного числа при первичном вводе цифр числа. Вычитают вводимые цифры из числа, находящегося во входном регистре 3. При этом разряды вводимого числа через блок 15 выдаются в канал 20. При вводе разряд поступает через элемент «И 8 в суу матор-вычислитель 2, на который подаются потенциал вычитания (вход «-) и содержимое входного регистра 3. В такте ввода прл помощи элементов «И 7 разность чисел по ступает в выходной регистр 4. Если при вычитании возникают займы, то они в том же такте образования разности через цепь элемента «И 18 вычитаются также нз одноразрядного числа, находящегося во входном регистре 3, В последующем промежуточном такте число, уменьшенное на значение введенного разряда из регистра 4, через элементы «И 9 и схемы «ИЛИ 12 снова переписывается во входной регистр 3. Последующие разряды при вводе аналогично вычитаются из числа, накопленного во входном регистре 3. По окончании ввода цифр накопленное контрольное число в такте вывода выдается из выходного регистра 4 через элементы «И 10 в блок 15. Пример процесса образования контрольного числа А-512, вводимого разряд за разрядом: а) вычитают из нуля «пятерку : О-5; образующийся заем через вентиль 18 также вычи тается: /Ci 10-5-1 4; б) вводят «1, контрольное число после ввода «Ь будет: /(2 в)вводят «2, контрольное число носле ввода «2 будет: /(3 г)выдают контрольное число, равное «1, в блок вывода. Операция над контрольными числами в процессе обработки информации или при арифметических операциях. Эти операции устройство производит, как с обычными числами, т. е. складывает и вычитает их. При этом имеющиеся переносы автоматически увеличивают контрольное число, а займы уменьшают его на «единицу, что совершается в устройстве при помощи установленного для этой цели элемента «И 18, на который во время получения контрольного числа и его обработки, а также при контроле подаются управляющие импульсные потенциалы. Например, складывают два числа А 512/1/ и В 855/9/. Нри сложении контрольных чисел получают «10 или единицу переноса, которая добавится к нулю. Получают контрольное число суммы, равное «1. (1)+855(9) 1367(1). Контроль правильности передачи, перезаписи, считывания, сложен-ия, вычитания или умножения чисел осуществляется путем суммирования всех цифр числа, в том числе и контрольного, полученного результата передачи, перезаписи, считывания или результата арифметических операций. При этом в ходе проверки результатов при суммировании цифр накопление итогов происходит Б регистрах 4 и 3 путем суммирования очередной цифры резульгага с о;игоразрядиым числом, иакопленным во входном регистре 3. Имеющиеся при этом переносы через элементы «И 18 автоматически увеличивают результат такого суммирования на «1. Итак, результат суммирования двух чисел равен 1367 (I). Складывают цифры результата. При сложении цифр получают перенос, который увеличит результат на «1, т.е. получают «4. Затем, последовательно складывая остальные разряды результата, в том числе и контрольного числа, иолучают «9. После суммироваяия цифр результата выявляют наличие «девятки при контроле с 1помощью блока 5 контроля по модулю «девять - в такте выявления сбоя. Если блок 5 Контроля по модулю «девять в этом такте выявит «девятку, то сбой в результатах отсутствует. Если цифра отлична от «9, то имеет место сбой.

Формула изобретения

Устройство для обнаружения ошибок, содержа1цее блок ввода информации, выходы

которого через соответствующие входные элементы «И подключены к первым входам двух элементов «ИЛИ, выходы которых подключены соответственно ко -входу входного регистра и ВХОДУ блока вывода информации, вторые входы схем «ИЛИ через соответствующие элементы «И церезаниси соединены со входом блока контроля по модулю «девять и выходом выходного регистра, отличающееся тем, что, с целью повышения эффективности обнаружения неисправностей и сокращения оборудования, оно содержит сумматор-вычитатель со схемой переноса, включенной между его соответствующими входом и выходом, элементы «И вывода и элементы «И ввода, ВХОДЫ которых подключены к выходаМ блока ввода информации, первый вход сумматора-вычитателя соединен с выходами элементов «И ввода, второй вход подключен к выходу входного регистра, а выход сумматора-вычитателя через элементы «И вывода соединен со входом выходного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Кассовый регистратор | 1978 |

|

SU748415A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1986 |

|

SU1478212A1 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

20

«Nl

Q

Авторы

Даты

1976-02-15—Публикация

1972-12-11—Подача