(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДЕСЯТИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоично- дЕСяТичНыХ чиСЕл B дВОичНыЕ | 1979 |

|

SU809152A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2566946C1 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ЕДИНИЦ | 2014 |

|

RU2540787C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для преобразования двоичныхчиСЕл B дВОичНО-дЕСяТичНыЕ | 1979 |

|

SU809153A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2013 |

|

RU2538949C1 |

I

Изобретение касается вычислительной техники, где оно может использоваться в качестве одного из узлов устройств обработки и вывода данных.

Известен преобразователь двоичного кода в десятичный, содержащий тетраду, каждый разряд которой содержит триггер, вхо;ДЫ которого соединены соответственно с ;двумя элементами задержки, входы которых ,в первом разряде соединены с выходами

двух соответствующих вентилей, первые ; входы которых объединены и подключены к шине сдвига, а вторые входы подключены к двум входным шинам, причем в первом, втором и третьем разрядах единичный выход ;триггера через соответствующие первый |элемент И и первый элемент ИЛИ подключены ко входу первого элемента задержки, выход которого подключен к единичному |Входу триггера последующего разряда, нулевые выходы триггера каждого из указаниых разрядов через второй элемент И и второй элемент ИЛИ подключены ко входу втоIporo элемента задержки, выход которого подключен к нулевому входу триггера пос|ледующего разряда, другие входы первых |и вторых элементов И соединены между собой.

Однако для этого преобразователя харак1терно низкое быстродействие.

Целью изобретения является повышение быстродействия преобразователя.

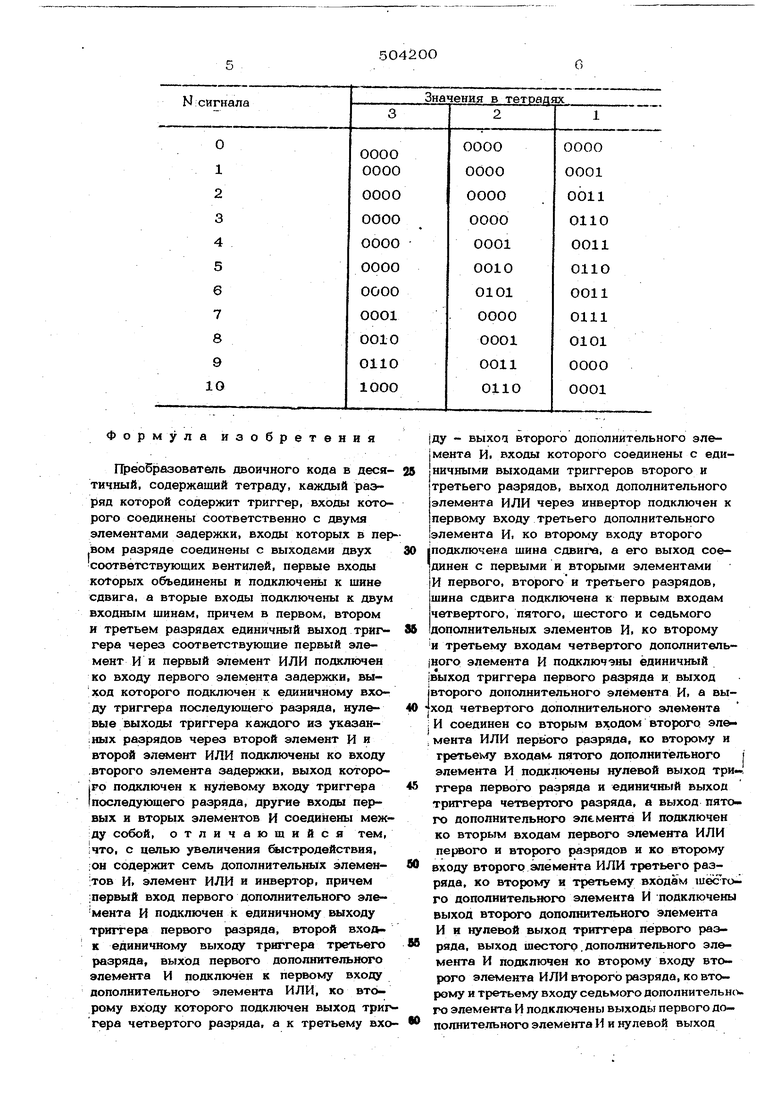

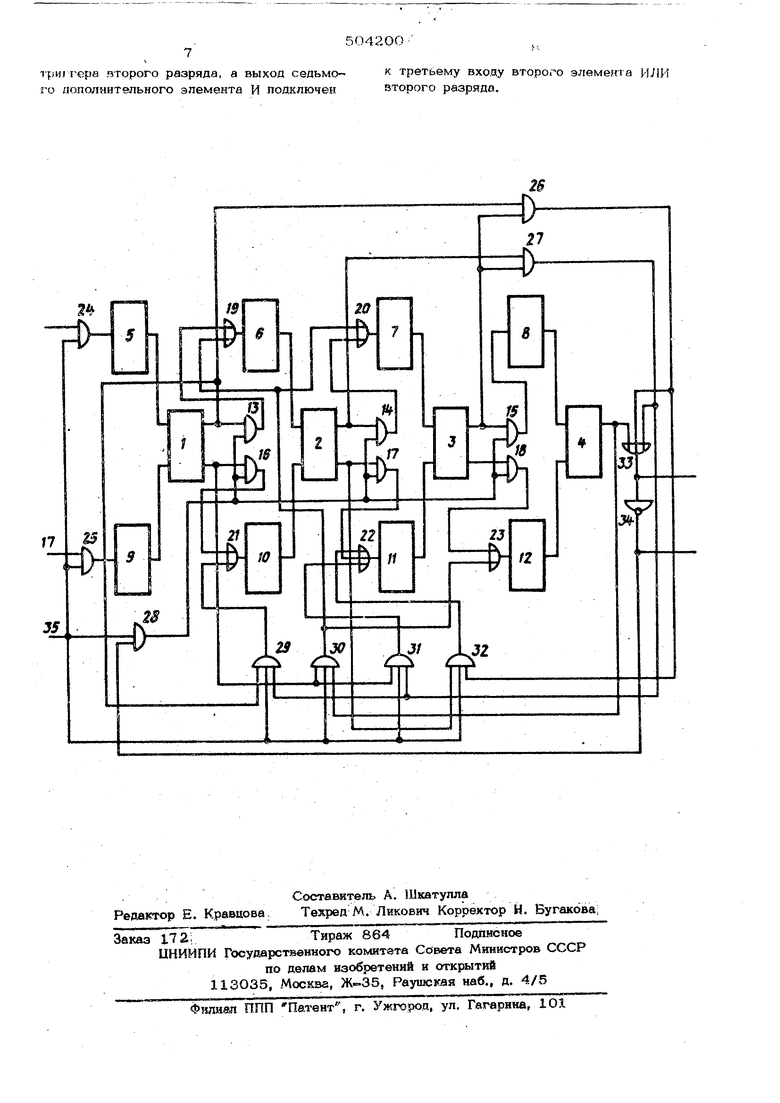

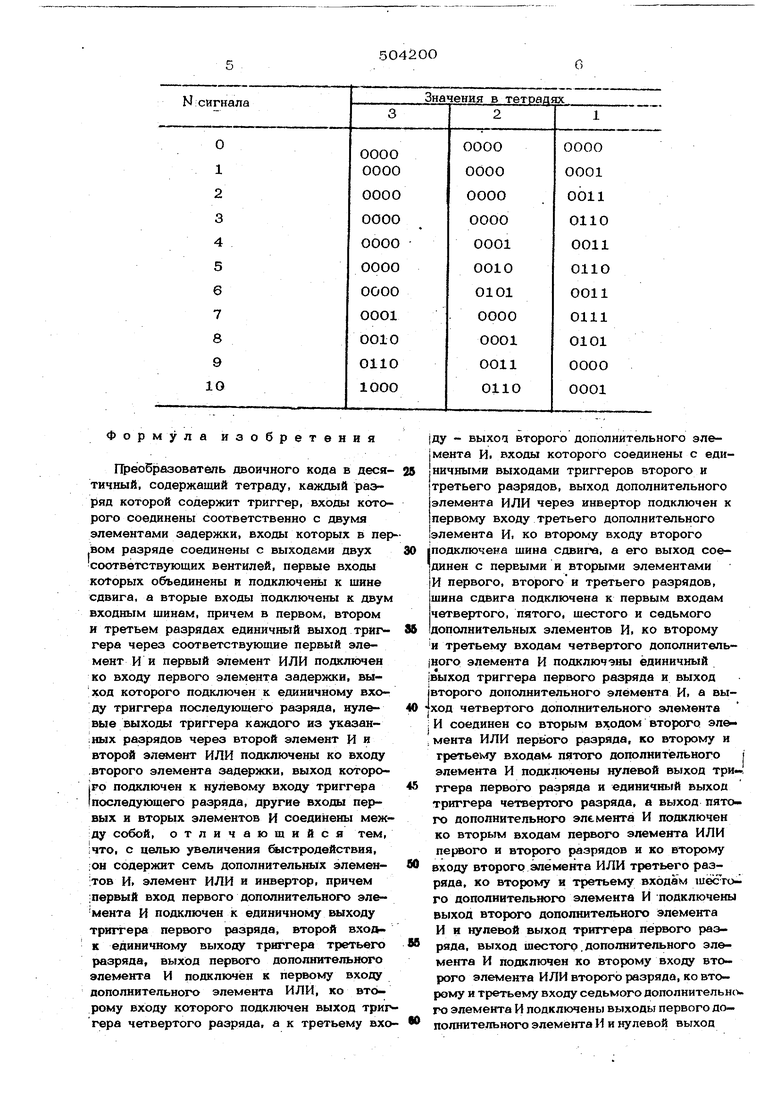

Для этого предложенный преобразова|тель содержит семь дополнительных элементов И, элемент ИЛИ и инвертор, причем первый вход первого дополнительного элемента И подклкзчен к единичному выходу триггера первого разряда, вторюй вход К единичному выходу триггера третьего ра.ряда, выход первого дополнительного элемента И подключен к первому входу допол нительного элемента ИЛИ, ко второму входу которого подключен выход тпиггепа чет вертого разряда, а к третьему - выход аторого дополнительного элемента И, зходы JKOTOporo соединены с единичными выходами Триггеров второго и третьего разрядов, вы |ход дополнительного элемента ИЛИ через рнвертор подключен к первому входу треЬгьего дополнительного элемента И. ко второму входу которого подключена шина сдвига, а его выход соединен с первыми и вторыми элементами И -первого, второго и третьего разрядов, шина сдвига подключена к первым входам четвертого, .пятого и седьмого дополнительных элементов И, ко второму и третьему входам четвертого дополнительного элемента И подключен ы единичный выход триггера первого разряда и выход второго дополнительного элемента И, а выход четвертого дополнительного элемента И соединен со вторым входом второго элемента ИЛИ первого разряда, ко вторрму и третьему входам пятого дополнительного элемента И подключены нулевой выход триггера первого разряда и единичный выход триггера четвертого разряда, а выход пятого дополнительного элемента И подключен ко вторым-входам первого элемента ИЛИ первого и второго раз рядов и ко второму входу второго элемента ИЛИ третьего разряда, ко второму и третьему входам шестого дополнительного элемента И подключены выход второго дополнительного элемента И и нулевой выход триггера первого разряда, выход шестого дополнительного элемента И подключен ко второму входу второго элемента ИЛИ второго разряда, ко второму и третьему входу седьмого дополнительного элемента И Подключены выходы первого дополнительного элемента И и нулевой выход триггера второго разряда, а выход седьмого дополнител ного элемента И подключен к третьему вхо ду второго элемента ИЛИ второго разряда. На чертеже показана одна тетрада пред ложенного преобразователя. На чертеже приняты следующие обозначения 1-4 -триг геры первого, второго, третьего и четвертого разрядов те1трады, 5-8 - первые элементы задержки первого, второго, третьего и четвертого ра13рядов тетрады, 9-12 вторые элементы зa epжки первого, второго, третьего и четвертого разрядов тет рады, 13-15 - пер;вые элементы И первого второго н третьего разрядов, 16-18 вторые элементы И первого, второго и третьего разрядов, 19-2О - первые элементы ИЛИ первого и второго разрядов, 21-23 - вторые элементы ИЛИ первого, второго и третьего разрядов, 24-25 - вен тили (элементы И), 26-32 - первый, второй, третий, четвертый, пятый, шестой н седьмой дополнительные элементы И, 33 дополнительный элемент ИЛИ, 34 - Инвертор и 35 - шина сдвига. В исходном состоянии все триггеры тетады находятся в нулевом состоянии. В роцессе преобразования на триггер первоо разряда 1 тетрады единиц поступают арафазным кодом последовательно во вреени двоичные разряды преобразуемого чиса, начиная со старшего разряда. Поступение по сигналу на шину сдвига 35 очеедного .чвоичного разряда на вход тетраы в зависимости от ее содержащего выывает сдвиг кода тетрады в сторону старих разрядов или установку в тетраде оп, еделенного кода с выработкой переноса, поступающего парафазным кодом на вход соседней старшей тетрады. Сигнал переноса П вырабатывается в сответствии со следующим логическим выр онием:П . - значения в разря 1V 3 4 дах тетрады на момент поступления сигнала по шине сдвига. Появление сигнала на выходе элемента ИЛИ 33 обеспечивает через элементы 34 и 28 блокировку поступления сигнала с шины сдвига разряды тетрады. Если в тетраде а Л 1, через элементы 27, 29, 1 2 «3 21 и Ю обеспечивается перевод триггера 2в нулевое состояние, если же а Л а Л а 1 о 1, по цепи из элементов 27, 31, 22, 11 осушест&ляется установка нулевого значения в триггере 3. Если в тетраде а Л а Л , по цепи из элементов 26, 32, 22, 11 устанавливается нулевое значение в триггере 3, если а 1, по цепи из эле14ментов 23, 12 устанавливается нулевое значение в триггере 4, а в триггерах 2 и 3по сигналу с выхода элемента 27 по цепям из элементов 19.6 и - . Таким образом, пр поступлении сигнала сдвига в тетраде будет обеспечен сдвиг, если в ней был код, не превышающий 4. ЕСЛИ в тетраде на момент cpBitra имеется .один из кодов PIOI, ОНО, 0111, 1ООО, 1О01, сдвиг запрещается, а в трех старших разрядах тетрады будет установлен одни из кодов ООО, ОО1, О1О, 011, 10О соответственно. В младшем разряде тетрадь всег да устанавливается значение, поступившее иа ее вход. В таблице приведена последовательность значений в тетрадах преобразователя при переводе в десятичный двоичный код. Формула изобретения Преобразователь двоичного кода в десятичный, содержащий тетраду, каждый разряд которой содержит триггер, входы которого соединены соответственно с двумя элементами задержки, входы которых в пер вом разряде соединены с выходами двух соответствующих вентилей, первые входы которых объединены и подключены к щине сдвига, а вторые входы подключены к двум входным шинам, причем в первом, втором и третьем разрядах единичный выход триггера через соответствующие первый элемент И и первый элемент ИЛИ подключен ко входу первого элемента задержки, выход которого подключен к единичному входу триггера последующего разряда, нулевые выходы триггера каждого из указанiHbix разрядов через второй элемент И и второй элемент ИЛИ подключены ко входу .второго элемента задержки, выход которого подключен к нулевому входу триггера последующего разряда, другие входы перьвых и вторых элементов И соединены меж :ду собой, отличающийся тем, ;что, с целью увеличения й 1стродействия, ,он содержит семь дополнительных элемен;тов И, элемент ИЛИ и инвертер, причем ; первый вход первого дополнительного элемента И подключен к единичному выходу триггера первого разряда, второй входк единичному выходу триггера третьего разряда, выход первого дополнительного элемента И подключён к первому входу дополнительного элемента ИЛИ, ко второму входу которого подключен выход три гера четвертого разряда, а к третьему вх ду ВЫХО1 второго дополнительного элемента И, входы которого соединены с единичными выходами триггеров второго и третьего разрядов, выход дополнительного элемента ИЛИ через инвертор подключен к первому входу третьего дополнительного элемента И, ко второму входу второго подключена щина сдвига, а его выход соединен с первыми и вторыми элементами |И первого, второгои третьего разрядов, щина сдвига подключена к первым входам четвертого, пятого, щестого и седьмого дополнительных элементов И, ко второму и третьему входам четвертого дополнительjHoro элемента И подключэны единичный |выход триггера первого разряда и выход jBToporo дополнительного элемента И, а четвертого дополнительного элемента I И соединен со вторым входом второго эл&I мента ИЛИ первого разряда, ко второму и rpeTbeiviy входам- пятого дополнительного | элемента И подключены нулевой выход три-, ггера первого разряда и единичный выход триггера четвертого разряда, а выход пятого дополнительного элемента И подключен ко вторым входам первого элемента ИЛИ первого и второго разрядов и ко второму входу второго элемента ИЛИ третьего разряда, ко второму и третьему входам шёегого дополнительного элемента И подключены выход второго дополнительного элемента И и нулевой выход триггера первого разряда, выход шестого дополнительного элемента И подключен ко второму входу второго элемента И ЛИ второго разряда, ко второму и третьему входу седьмого дополнительнее го элемента И подключены выходы первого дополнительного элемента И и нулевой выход

триммера второго разряда, а выход седьмого дополнительного элемента И подключен

к третьему входу второго элеменча ИЛИ второго разряда.

Авторы

Даты

1976-02-25—Публикация

1973-06-27—Подача