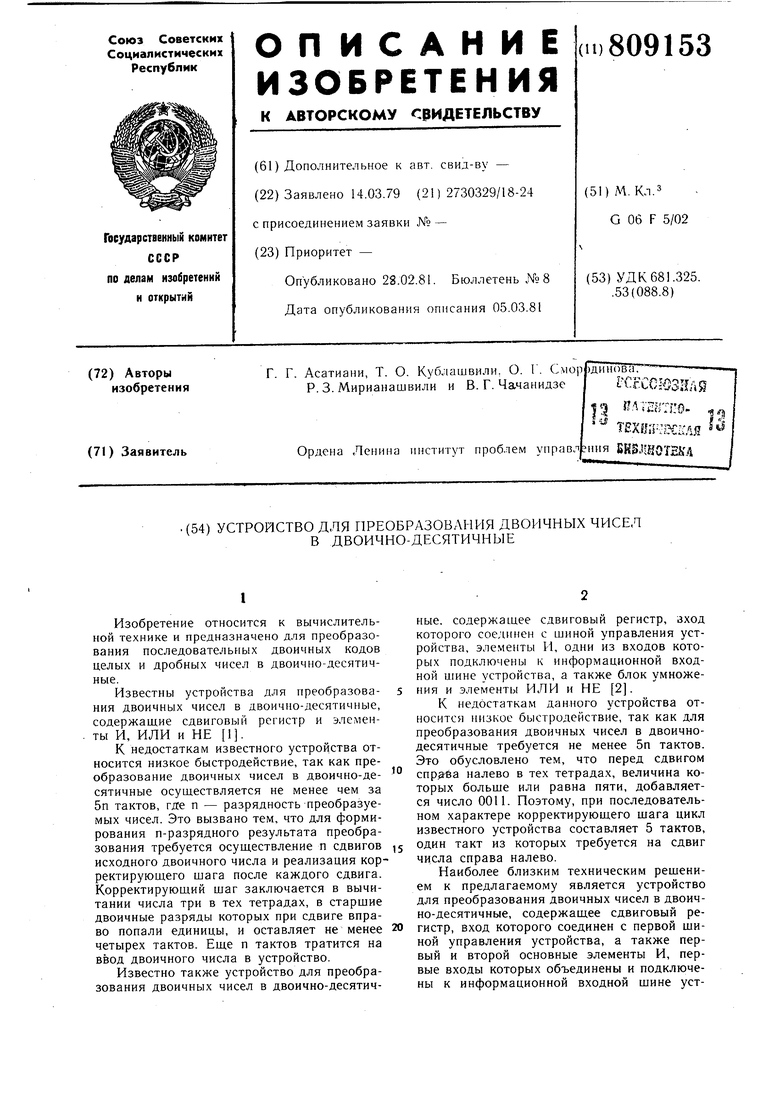

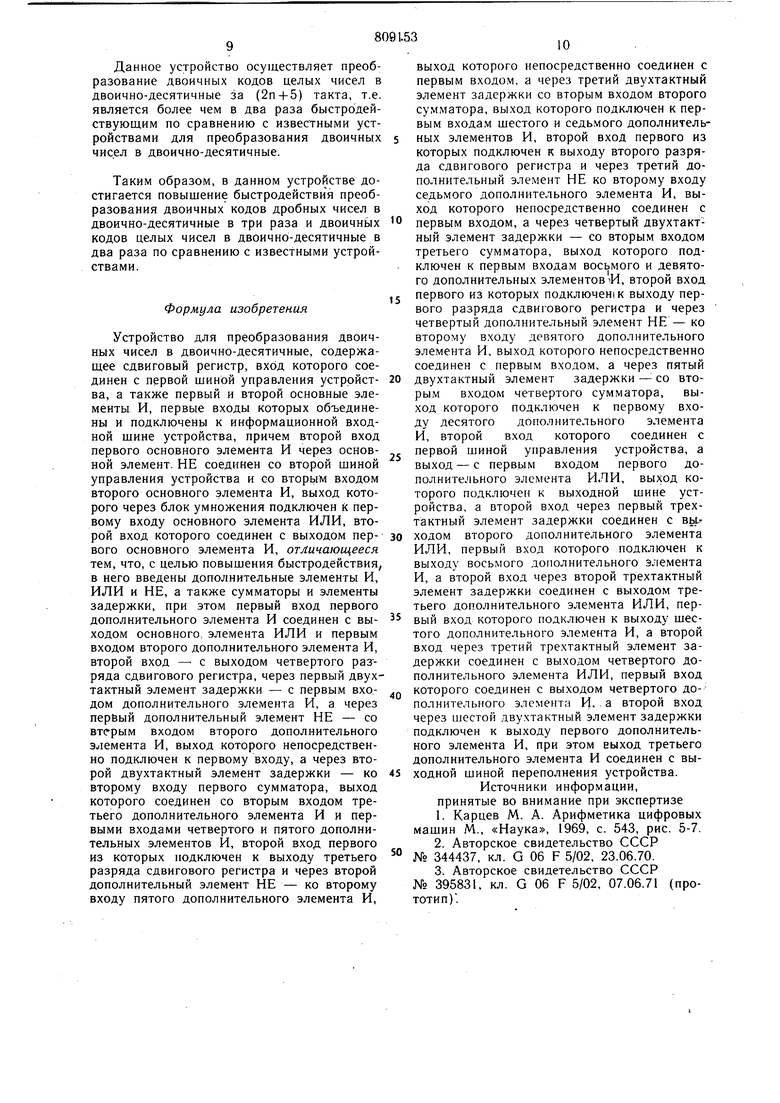

Изобретение относится к вычислительной технике и предназначено для преобразования последовательных двоичных кодов целых и дробных чисел в двоично-десятичные. Известны устройства для преобразования двоичных чисел в двоично-десятичные, содержащие сдвиговый регистр и элементы И, ИЛИ и НЕ 1. К недостаткам известного устройства относится низкое быстродействие, так как преобразование двоичных чисел в двоично-десятичные осуществляется не менее чем за 5п тактов, где п - разрядность преобразуемых чисел. Это вызвано тем, что для формирования п-разрядного результата преобразования требуется осуществление п сдвигов исходного двоичного числа и реализация кор ректирующего шага после каждого сдвига. Корректирующий щаг заключается в вычитании числа три в тех тетрадах, в старщие двоичные разряды которых при сдвиге вправо попали единицы, и оставляет не менее четырех тактов. Еще п тактов тратится на ввод двоичного числа в устройство. Известно также устройство для преобразования двоичных чисел в двоично-десятичные, содержащее сдвиговый регистр, зход которого соединен с шиной управления устройства, элементы И, одни из входов которых подключены к информационной входной щине устройства, а также блок умножения и элементы ИЛИ и НЕ 2. К недостаткам данного устройства относится низкое быстродействие, так как для преобразования двоичных чисел в двоичнодесятичные требуется не менее 5п тактов. Это обусловлено тем, что перед сдвигом налево в тех тетрадах, величина которых больше или равна пяти, добавляется число 0011. Поэтому, при последовательном характере корректирующего шага цикл известного устройства составляет 5 тактов, один такт из которых требуется на сдвиг числа справа налево. Наиболее близким техническим решением к предлагаемому является устройство для преобразования двоичных чисел в двоично-десятичные, содержащее сдвиговый регистр, вход которого соединен с первой шиной управления устройства, а также первый и второй основные элементы И, первые входы которых объединены и подключены к информационной входной шине устроиства, причем второй вход первого основного элемента И через основной элемент НЕ соединен со второй шиной управления устройства и со вторым входом второго основного элемента И, выход которого через блок умножения подключен к первому х входу основного элемента ИЛИ, второй вход которого соединен с выходом первого основного элемента И 3. К недостаткам такого устройства относится низкое быстродействие, так как для преобразования двоичного числа в двоично-десятичные требуется 5п тактов. Это вызвано тем, что в этом устройстве преобразование осуществляется при помооди сдвига и коррекции, заключающееся в том, что исходное двоичное число последовательно делится на два, т.е. сдвигается на один разряд в сторону младщих разрядов, и из тех тетрад, в которые при сдвиге единица переходит из соседней старшей тетрады, вычитается число ООП. Последнее компенсирует ошибку, образующуюся в результате сдвига двоичного числа. Цель изобретения - повышение быстродействия устройства для преобразования двоичных чисел в двоично-десятичные. Указанная цель достигается за счет того, что в устройстве для преобразования двоичных чисел в двоично-десятичные, содержащем сдвиговый регистр, вход которого соединен с первой шиной управления устройства, а также первый и второй основные элементы И, первые входы которых объединены и подключены к информационной входной, шине устройства, причем второй вход первого основного элемента И через основной элемент НЕ соединен со второй щиной управления устройства и со вторым входом второго основного элемента И, выход которого через блок умножения подключен к первому входу основного элемента ИЛИ, второй вход которого соединен с выходом первого основного элемента И, введены дополнительные элементы И, ИЛИ и НЕ, а также сумматоры и элементы задержки, при этом первый вход первого дополнительного элемента И соединен с выходом основного элемента ИЛИ и первым входом второго дополнительного элемента И, второй вход - с выходом четвертого разряда сдвигового регистра, через первый двухтактный элемент задержки - с первым входом третьего дополнительного элемента И, а через первый дополнительнй элемент НЕ со вторым входом второго дополнительного элемента И, выход которого непосредственно подключен к первому входу, а через второй двухтактный элемент задержки ко второму входу первого сумматора, выход которого соединен со вторым входом третьего дополнительного элемента И и первыми входами четвертого и пятого дополнительных элементов И, второй вход первого из которых подключен к выходу третьего разряда сдвигового регистра и через второй дополнительный элемент НЕ - ко второму входу пятого дополнительного элемента И, выход которого непосредственно соединен с первым входом, а через третий двухтактный элемент задержки со вторым входом второго сумматора, выход которого подключен к первым входам шестого и седьмого дополнительных элементов И, второй вход первого из которых подключен к выходу второго разряда сдвигового регистра и через третий дополнительный элемент НЕ ко второму входу седь.мого дополнительного элемента И, выход которого непосредственно соединен с первым входом, а через четвертый двухтактный элемент задержки - со вторым входом третьего су.мматора, выход которого подключен к первым входам восьмого и девятого дополнительных элементов И, второй вход первого из которых подключен к выходу первого разряда сдвигового регистра и через четвертый дополнительный элемент НЕ - ко второму входу девятого дополнительного элемента И, выход которого непосредственно соединен с первым входом, а через пятый двухтактный элемент задержки - со вторым входом четвертого сумматора, выход которого подключен к первому входу десятого дополнительного элемента И, второй вход которого соединен с первой шиной управления устройства, а выход - с первым входом первого дополнительного элемента ИЛИ, выход которого подключен к выходной шине устройства, а второй вход через первый трехтактный элемент задержки соединен с выходом второго дополнительного э.лемента ИЛИ, первый вход которого подключен к выходу восьмого дополнительного элемента И, а второй вход через второй трехтактный элемент задержки соединен с выходом третьего дополнительного элемента, ИЛИ, первый вход которого подключен к выходу шестого дополнительного элемента И, а второй вход через третий трехтактный элемент задержки соединен с выходо.м четвертого дополнительного элемента ИЛИ, первый вход которого соединен с выходом четвертого дополнительного элемента И, а второй вход через шестой двухтактный элемент задержки подключен к выходу первого дополнительного элемента И, при этом выход третьего дополнительного элемента И соединен с выходной шиной переполнения устройства. На фиг. 1 представлена функциональная схема устройства для преобразования двоичных чисел в двоично-десятичные; на фиг. 2 и 3 - временные диаграммы работы устройства. Устройство содержит сдвиговый регистр 1, вход которого соединен с первой шиной 2 управления, первый и второй основные элементы И 3 и 4, первые входы которых объединены и подключены к информационной входной шине 5, второй вход первого основного элемента И 3 через основной элемент НЕ 6 соединен со второй шиной 7

управления и со вторым входом второго основного элемента И 4, выход которого через блок 8 умножения подключен к первому входу основного элемента ИЛИ 9, второй вход которого соединен с выходом первого основного элемента И 3, первый вход первого дополнительного элемента И 10 соединен с выходом основного элемента ИЛИ 9 и первым входом второго дополнительного элемента И 11, второй вход - с выходом четвертого разряда сдвигового регистра 1, через первый двухтактный элемент 12 задержки с первым входом третьего дополнительного элемента И 13, а через первый дополнительный элемент НЕ 14 со вторым входом второго дополнительного элемента И 11, выход которого непосредственно подключен к первому входу, а через второй двухтактный элемент 15 задержки ко второму входу первого сумматора 16, выход которого соединен со вторым входом третьего дополнительного элемента И 13 и первыми входами четвертого и пятого дополнительных элементов И 17 и 18, второй вход первого из которых подключен к выходу третьего разряда сдвигового регистра 1 и через второй дополнительный элемент НЕ 19 ко второму входу пятого дополнительного элемента И 18, выход которого непосредственно соединен с первым входом, а через третий двухтактный элемент 20 задержки со вторым входом второго сумматора 21, выход которого подключен к первым входам шестого и седьмого элементов И 22 и 23, второй вход первого из которых подключен к выходу второго разряда сдвигового регистра 1 и через третий дополнительный элемент НЕ 24 ко второму входу седьмого дополнительного элемента И 23, выход которого непосредственно соединен с первым входом а через четвертый двухтактный элемент 25 задержки со вторым входом третьего сумматора 26, выход которого подключен к первым входам восьмого и девятого дополнительных элементов И 27 и 28, второй вход первого из которых подключен к выходу первого разряда сдвигового регистра 1 и через четвертый дополнительный элемент НЕ 29 ко второму входу девятого дополнительного элемента И 28, выход которого непосредственно соединен с первым входом, а через пятый двухтактный элемент 30 задержки со вторым входом четвертого сумматора 31, выход которого подключен к первому входу десятого дополнительного элемента И 32, второй вход которого соединен с первой шиной 2 управления, а выход - с первым входом первого дополнительного элемента ИЛИ 33, выход которого подключен к выходной шине 34, а второй вход через первый трехтактный элемент 35 задержки соединен с выходом второго дополнительного элемента ИЛИ 36, первый вход которого подключен к выходу восьмого дополнительного элемента И 27, а второй вход через второй трехтактный элемент 37 задержки

соединен с выходом третьего дополнительного элемента ИЛИ 38, первый вход которого подключен к выходу шестого дополнительного элемента И 22, а второй вход через третий трехтактный элемент 39 задержки соединен с выходом четвертого дополнительного элемента ИЛИ 40, первый вход которого соединен с выходом четвертого дополнительного элемента И 17, а второй вход через шестой двухтактный элемент 41 задержки подключен к выходу первого дополнительного элемента И 10, выход третьего дополнительного элемента И 13 соединен с выходной шиной 42 переполнения, сумматоры 43, однотактные элементы 44 задержки, двухтактные элементы 45 задержки, трехтактные элементы 46 задержки.

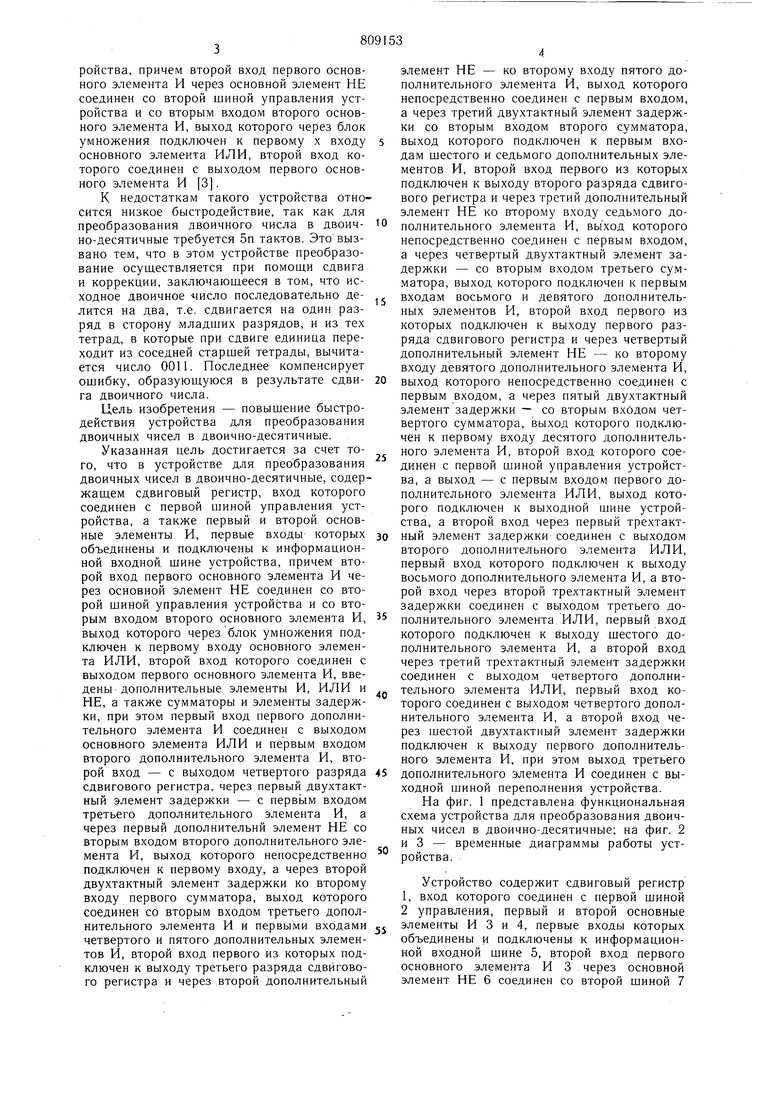

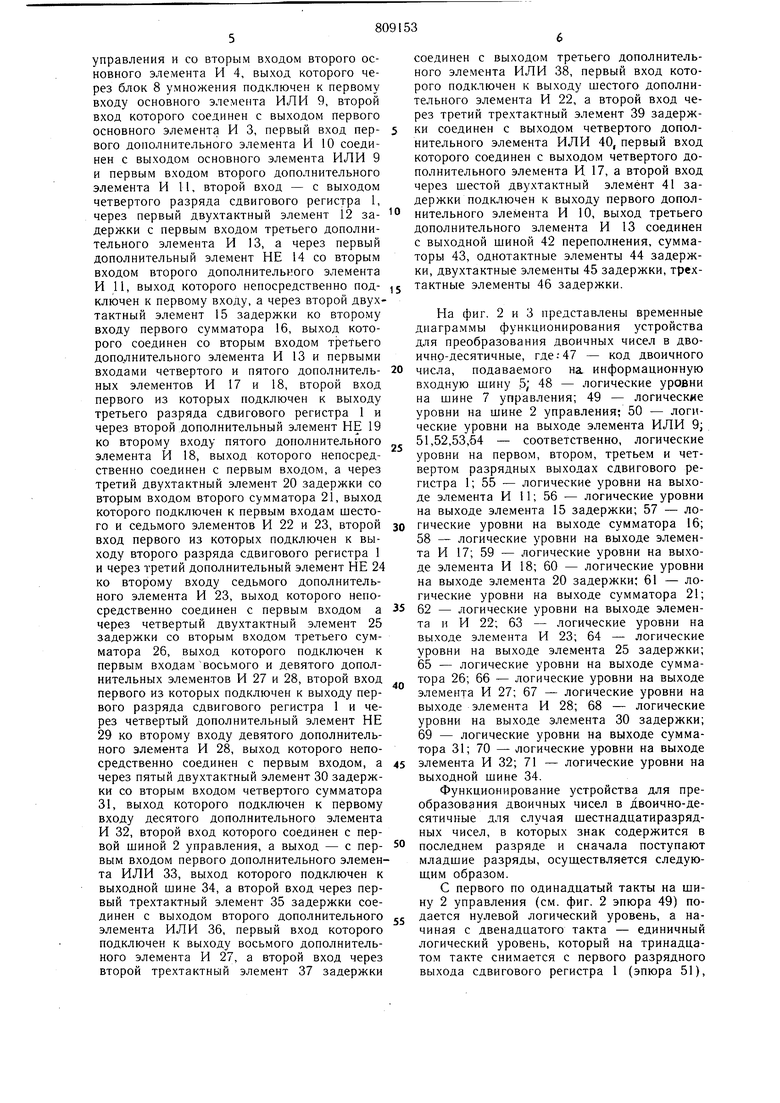

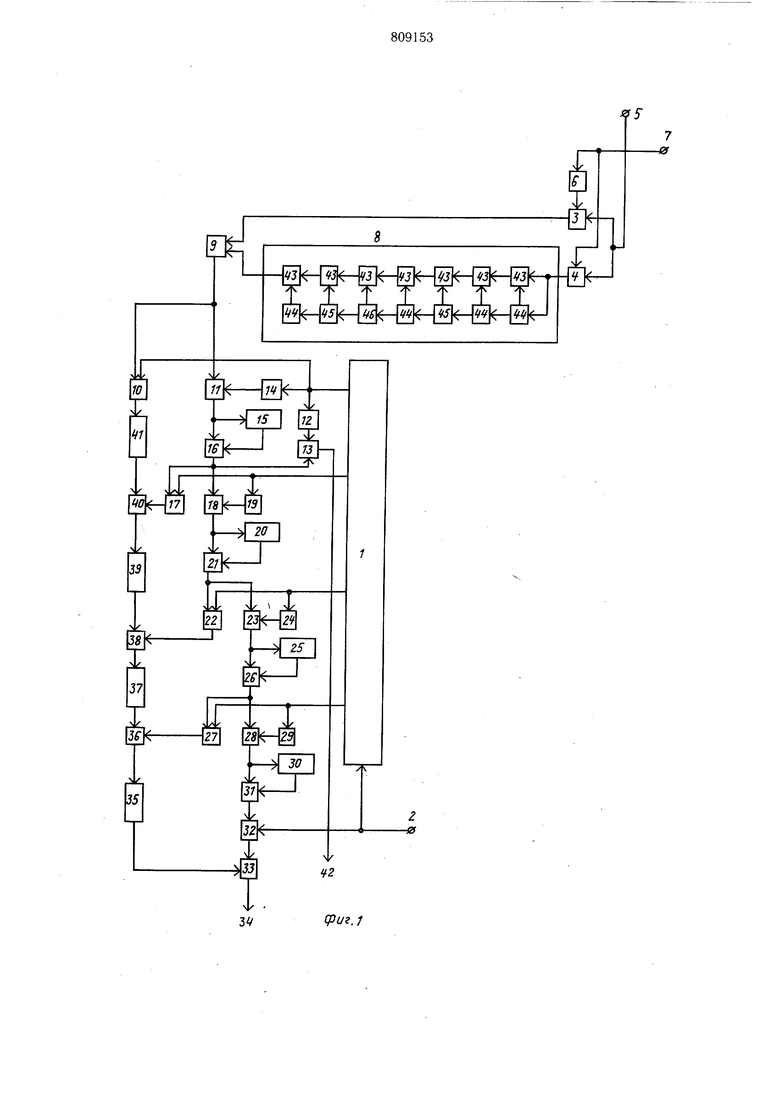

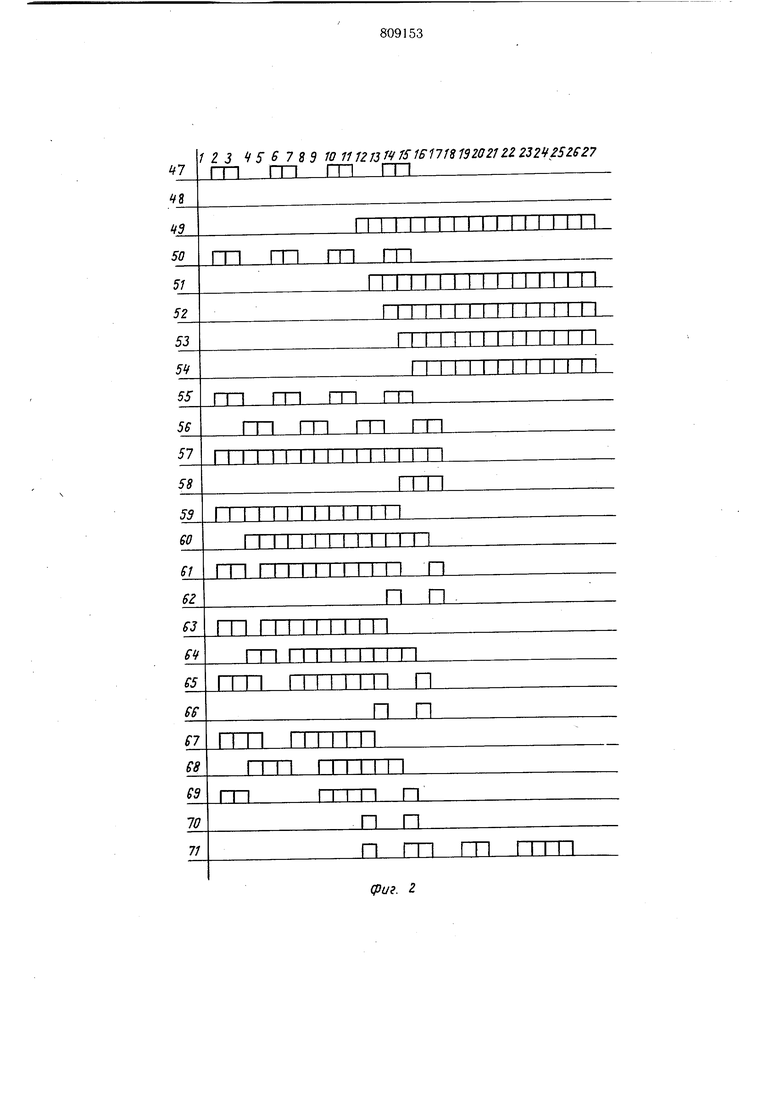

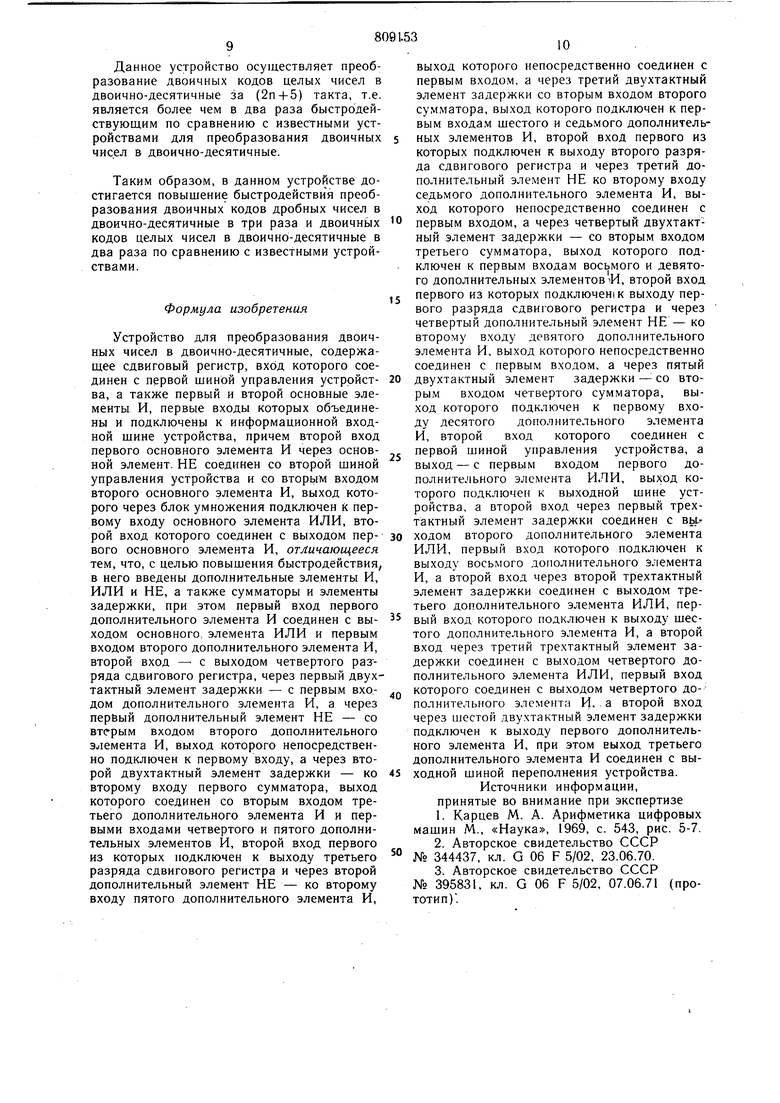

На фиг. 2 и 3 представлены временные диаграммы функционирования устройства для преобразования двоичных чисел в двоично-десятичные, где .47 - код двоичного числа, подаваемого на информационную входную шину 5; 48 - логические уровни на шине 7 управления; 49 - логические уровни на шине 2 управления; 50 - логические уровни на выходе элемента ИЛИ 9; 51,52,53,54 - соответственно, логические уровни на первом, втором, третьем и четвертом разрядных выходах сдвигового регистра 1; 55 - логические уровни на выходе элемента И 11; 56 - логические уровни на выходе элемента 15 задержки; 57 - логические уровни на выходе сумматора 16; 58 - логические уровни на выходе элемента И 17; 59 - логические уровни на выходе элемента И 18; 60 - логические уровни на выходе элемента 20 задержки; 61 - логические уровни на выходе сумматора 21; 62 - логические уровни на выходе элемента и И 22; 63 - логические уровни на выходе элемента И 23; 64 - логические уровни на выходе элемента 25 задержки; 65 - логические уровни на выходе сумматора 26; 66 - логические уровни на выходе элемента И 27; 67 - логические уровни на выходе элемента И 28; 68 - логические уровни на выходе элемента 30 задержки; 69 - логические уровни на выходе сумматора 31; 70 - логические уровни на выходе элемента И 32; 71 - логические уровни на выходной шине 34.

Функционирование устройства для преобразования двоичных чисел в двоично-десятичные для случая шестнадцатиразрядных чисел, в которых знак содержится в последнем разряде и сначала поступают младшие разряды, осушествляется следующим образом.

С первого по одинадцатый такты на шину 2 управления (см. фиг. 2 эпюра 49) подается нулевой логический уровень, а начиная с двенадцатого такта - единичный логический уровень, который на тринадцатом такте снимается с первого разрядного выхода сдвигового регистра 1 (эпюра 51), на четырнадцатом такте - со второго разрядного выхода сдвигового регистра 1 (эпюра 52) и т.д. (эпюры 53 и 54). В этом режиме на шину 7 управления подается нулевой логический уровень (эпюра 48). Начиная с первого такта на- информационную входную шину 5 подается код дзоичного числа (эпюра 47), который через элементы И 3 и ИЛИ 9 (эпюра 50) поступает на выходы элементов И 10 и И 11. Элемент И 10 при помощи единичного логического уровня С четвертого разрядного выхода сдвигового регистра 1 разблокируется на шестнадцатом такте, вследствие чего логический уровень знакового разряда подается на вход элемента 41 задержки. На. элемент И 11 дробная часть исходного двоичного числа отделяется от его знакового разряда, так как элемент И 11 при помоши нулевого логического уровня с четвертого разрядного выхода сдвигового регистра 1 разблокирован с первого по пятнадцатый такты (эпюра 55). При помоши элемента 15 задержки (эпюру 56) и сумматора 16 (эпюру 57) осуществляется умножение двоичного кода дробной части исходного числа на число 1010, в результате чего с пятнадцатого по семнадцатый такты на выходе элемента И 17 (эпюра 58) управляемого от третьего разрядного выхода сдвигового регистра 1, формируются логические уровни четвертой тетрады двоично-десятичного кода искомого числа. Если исходное двоичное число больше по абсолютному значению 0.110011001100110 0.7999, то на шестнадцатом такте на выходной шине 42 переполнения образуется единичный логический уровень, который указывает на наличие переполнения. Промежуточный результат с выхода сумматора 16, начиная с пятнадцатого такта через элемент И 18 (эпюра 59), управляемого с третьего разрядного выхода сдвигового регистра 1, при помоши элемента 20 задержки (эпюра 60) и сумматора 21 (эпюра 61) умножается на число 1010,.в результате чего с четырнадцатого по семнадцатый такты на выходе элемента И 22 (эпюра 62), управляемого со второго разрядного выхода сдвигового регистра 1, формируются логические уровни третьей тетрады двоично-десятичного кода искомого числа. Промежуточный результат с выхода сумматора 21, начиная с четырнадцатого такта через элемент И 23 (эпюра 63), управляемого со второго разрядного выхода .сдвигового регистра 1, при помощи элемента 25 задержки (эпюра 64) и сумматора 26 (эпюра 65) умножается на число 1010, в результате чего с тринадцатого по шестнадцатый такты на выходе элемента И 27 (эпюра 66), управляемого с первого разрядного выхода сдвигового регистра 1, формируются логические уровни второй тетрады искомого двоично-десятичного кода. Промежуточный результат с выхода сумматора 26, начиная с тринадцатого такта через элемент И 28 (эпюра 67), управляемого с первого разрядного выхода сдвигового регистра 1, при юмощи элемента задержки 30 (эпюра 68) и сумматора 31 (эпюра 69) умножается на число 1010, в результате чего с двенадцатого по пятнадцатый такты на элемента И 32 (эпюра 70) формируются логические уровни первой тетрады искомого двоично-десятичного кода. Элементы 35, 37, 39, 41 задержки и элементы ИЛИ 33, 36, 38, 40 служат для временной балансировки фронтов логических уровней тетрад и знакового разряда двоично-десятичного кода искомого числа. Результат преобразования с двенадцатого по двадцать седьмой:такты снимается с выходной шины 34 (эпюра 71). На фиг. 2 рассмотрен случай преобразования двоичного кода дробного числа 0.110011001100110 в двоично-десятичный код 0.111100110011001. Таким образом, предлагаемое устройство осушествляет преобразование двоичных кодов дробных чисел в двоично-десятичные за 2п + 5) тактов, т.е. является почти в три раза быстродействующим по сравнению с известными устройствами для преобразования двоичных чисел в двоично-десятичные. в случае преобразования двоичных кодов целых чисел в двоично-десятичные на шину 7 управления подается единичный логический уровень ( фиг. 3 эпюра 48). При этом с первого по двадцать второй такты на шину 2 управления подается нулевой логический уровень, а начиная с двадцать третьего такта - единичный логический уровень (эпюра 49). В результате этого информационная входная шина 5, на которую подается двоичный код исходного числа без знакового разряда, через элемент И 4 оказывается подключенной ко входу блока 8 умножения. Так как исходное целое двоичное число принимается за дробное, блок 8 осуцхествляет умножение исходного двоичного кода преобразуемого числа на число 172, где гп - разрядность двоично-десяТичного числа. Поэтому, в рассматриваемом случае гп 4 и блок 8 умножает исходное двоичное число на число лью получения точности преобразования для максимальной ошибки порядка шестнадцатыи разряд искомого двоично-десятичного кода преобразуемого двоичного числа блок 8 согласно фиг. 1 осуществляет умножение на число 0.000000000000011010001101И В этом режиме дальнейшее функционирование предлагаемого устройства осуществляется аналогично вышеуказанного, и результат преобразования снимается с выходной шины 34 с двадцать третьего по трид цать седьмой такты. На фиг. 3 рассмотрен приМ|ер преобразования двоичного кода целого числа 001100110010011 в двоично-десятичный код 110010101000111. Данное устройство осуществляет преобразование двоичных кодов целых чисел в двоично-десятичные за (2п + 5) такта, т.е. является более чем в два раза быстродействующим по сравнению с известными устройствами для преобразования двоичных чисел в двоично-десятичные. Таким образом, в данном устройстве достигается повышение быстродействия преобразования двоичных кодов дробных чисел в двоично-десятичные в три раза и двоичных кодов целых чисел в двоично-десятичные в два раза по сравнению с известными устройствами. Формула изобретения Устройство для преобразования двоичных чисел в двоично-десятичные, содержащее сдвиговый регистр, вход которого соединен с первой шиной управления устррйства, а также первый и второй основные элементы И, первые входы которых объединены и подключены к информационной входной шине устройства, причем второй вход первого основного элемента И через основной элемент. НЕ соединен со второй шиной управления устройства и со вторым входом второго основного элемента И, выход которого через блок умножения подключен к первому входу основного элемента ИЛИ, второй вход которого соединен с выходом первого основного элемента И, отличающееся тем, что, с целью повышения быстродействия, в него введены дополнительные элементы И, ИЛИ и НЕ, а также сумматоры и элементы задержки, при этом первый вход первого дополнительного элемента И соединен с выходом основного элемента ИЛИ и первым входом второго дополнительного элемента И, второй вход - с выходом четвертого разряда сдвигового регистра, через первый двухтактный элемент задержки - с первым входом дополнительного элемента И, а через первый дополнительный элемент НЕ - со втерым входом второго дополнительного элемента И, выход которого непосредственно подключен к первому входу, а через второй двухтактный элемент задержки - ко второму входу первого сумматора, выход которого соединен со вторым входом третьего дополнительного элемента И и первыми входами четвертого и пятого дополнительных элементов И, второй вход первого из которых подключен к выходу третьего разряда сдвигового регистра и через второй дополнительный элемент НЕ - ко второму входу пятого дополнительного элемента И, ВЫХОД которого непосредственно соединен с первым входом, а через третий двухтактный элемент задержки со вторым входом второго сумматора, выход которого подключен к первым входам шестого и седьмого дополнительных элементов И, второй вход первого из которых подключен к выходу второго разряда сдвигового регистра и через третий дополнительный элемент НЕ ко второму входу седьмого дополнительного элемента И, выход которого непосредственно соединен с первым входом, а через четвертый двухтактный элемент задержки - со вторым входом третьего сумматора, выход которого подключен к первым входам восьмого и девятого дополнительных элементов М, второй вход первого из которых подключен к выходу первого разряда сдвигового регистра и через четвертый дополнительный элемент НЕ - ко второму входу девятого дополнительного элемента И, выход которого непосредственно соединен с первым входом, а через пятый двухтактный элемент задержки -- со вторым входом четвертого сумматора, выход которого подключен к первому входу десятого дополнительного элемента И, второй вход которого соединен с первой шиной управления устройства, а выход - с первым входом первого дополнительного элемента ИЛИ, выход которого подключен к выходной шине устройства, а второй вход через первый трехтактный элемент задержки соединен с вьи ходом второго дополнительного элемента ИЛИ, первый вход которого подключен к выходу восьмого дополнительного элемента И, а второй вход через второй трехтактный элемент задержки соединен с выходом третьего дополнительного элемента ИЛИ, первый вход которого подключен к выходу шестого дополнительного элемента И, а второй вход через третий трехтактный элемент задержки соединен с выходом четвертого дополнительного элемента ИЛИ, первый вход которого соединен с выходом четвертого дополнительного элемента И, . а второй вход через шестой двухтактный элемент задержки подключен к выходу первого дополнительного элемента И, при этом выход третьего дополнительного элемента И соединен с выходной шиной переполнения устройства. Источники информации, принятые во внимание при экспертизе 1.Карцев М. А. Арифметика цифровых машин М., «Наука, 1969, с. 543, рис. 5-7. 2.Авторское свидетельство СССР № 344437, кл. G 06 F 5/02, 23.06.70. 3.Авторское свидетельство СССР № 395831, кл. G 06 Е 5/02, 07.06.71 (прототип).

(Puij

123 Ч 5 S 7 ВЗ JO 111213 515111913202111232 252.527

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоично- дЕСяТичНыХ чиСЕл B дВОичНыЕ | 1979 |

|

SU809152A1 |

| Устройство для умножения последовательных п-разрядных двоичных кодов | 1978 |

|

SU769541A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1978 |

|

SU742924A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для деления п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU807282A1 |

50

51

53

5

55

mпи

56

m m m

53

m I I I 11 I I I I I I п

f

62

fj

I п I ГТТТТ1

f/

m 11 I I 11 I I I

f5

fgrm I I I I I I I

ез

I I I I I П

гп т п I и и п

1±

I I I I I I I IТМ

UL

nTL

п

п п

п п п m

фиг. Z

Авторы

Даты

1981-02-28—Публикация

1979-03-14—Подача