Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

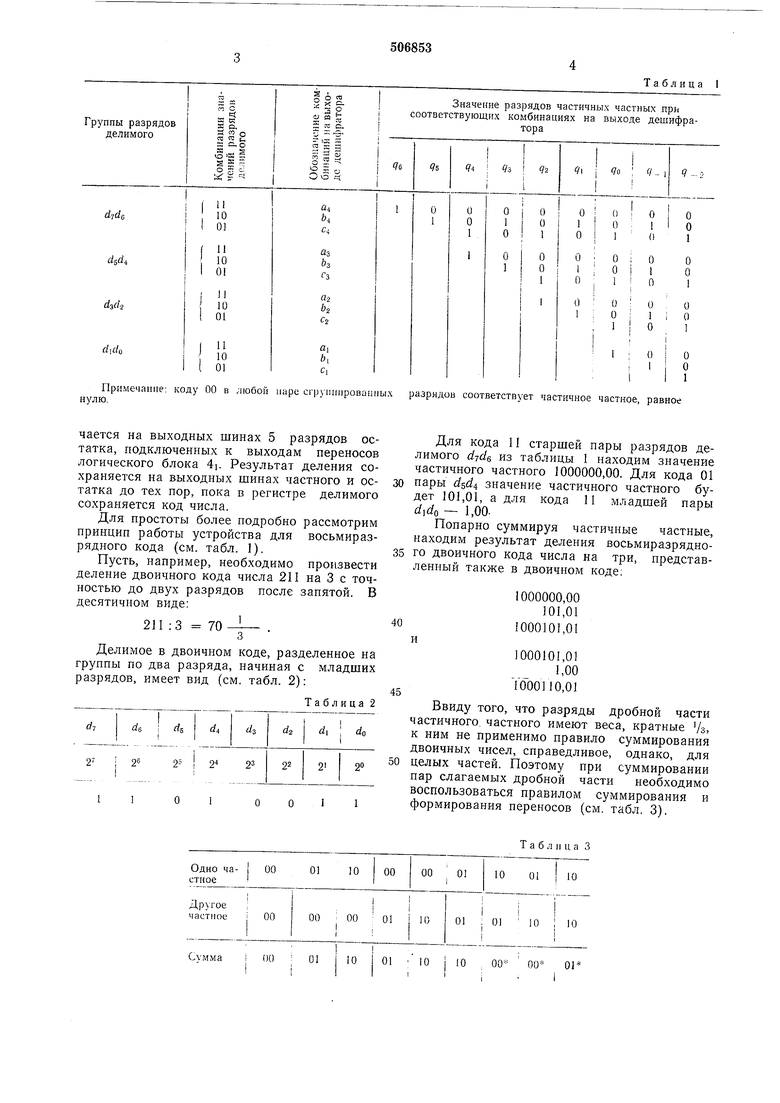

Примечание: коду 00 в любой паре crp.iinijpoBaaiibi. нулю.

чается на выходных шинах 5 разрядов остатка, подключенных к выходам переносов логического блока 4. Результат деления сохраняется на выходных шинах частного и остатка до тех пор, пока в регистре делимого сохраняется код числа.

Для простоты более подробно рассмотрим принцип работы устройства для восьмиразрядного кода (см. табл. 1).

Пусть, например, необходимо произвести деление двоичного кода числа 211 на 3 с точностью до двух разрядов после запятой. В десятичном виде:

211 :3 70- .

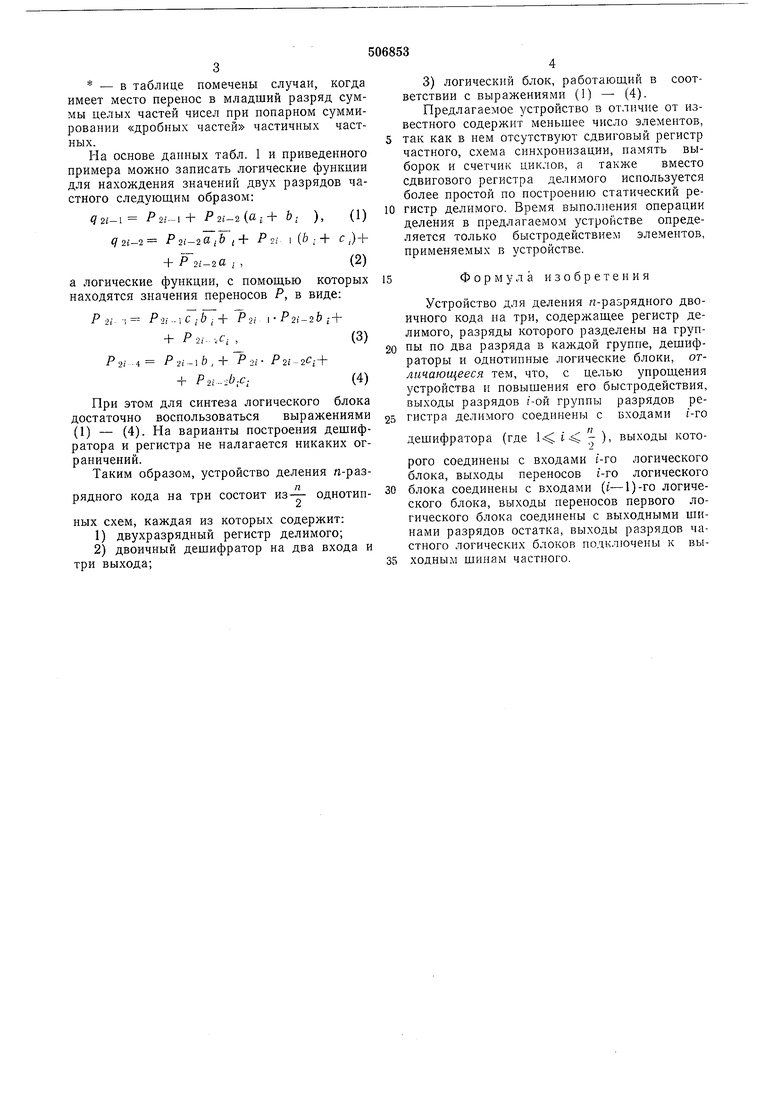

Делимое в двоичном коде, разделенное на группы по два разряда, начиная с младших разрядов, имеет вид (см. табл. 2):

Таблица 2

d7

У

У

(Ю : 01

CvMMa

разрядов соответствует частичное частное, равное

Для кода 11 старшей пары разрядов делимого cfrufe из таблицы I находим значение частичного частного 1000000,00. Для кода 01

пары значение частичного частного будет 101,01, а для кода 11 младшей пары rfjufo - 1,00.

Попарно суммируя частичные частные, находим результат деления восьмиразрядного двоичного кода числа на три, представленный также в двоичном коде:

1000000,00 01,01

1000101,01 и

1000101,01

1,00

1000110,01

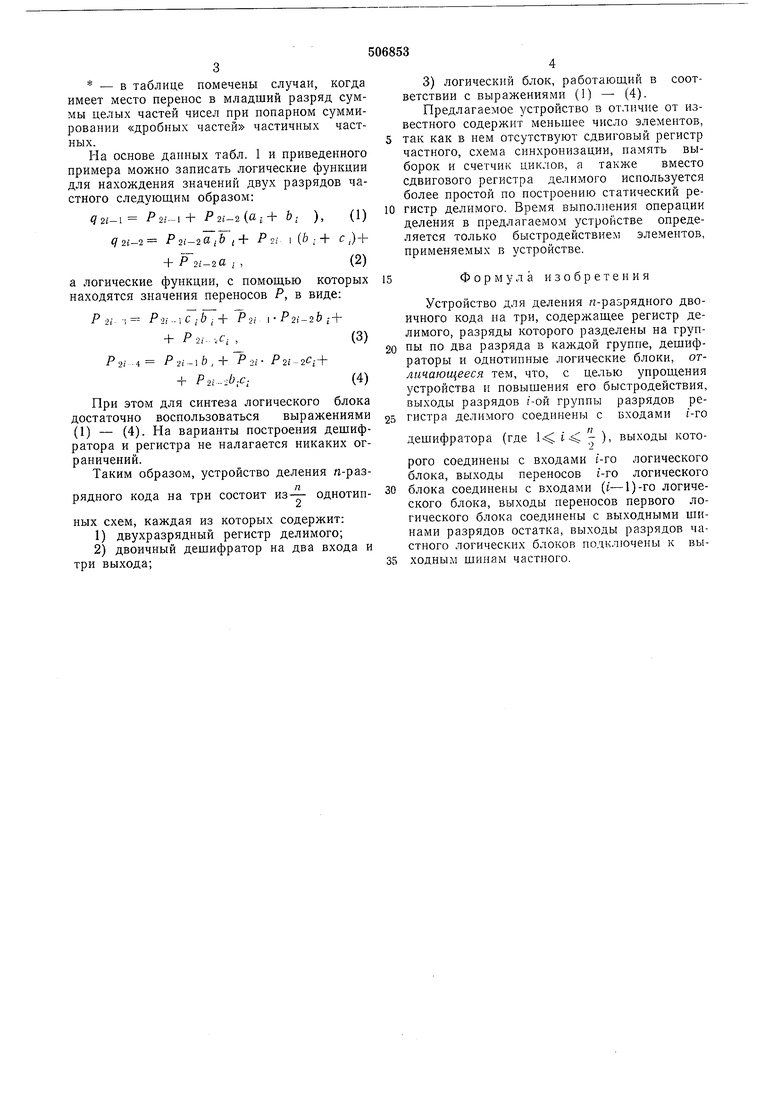

Ввиду того, что разряды дробной части частичного, частного имеют веса, кратные /з, к ним не применимо правило суммирования двоичных чисел, справедливое, однако, для целых частей. Поэтому при суммировании пар слагаемых дробной части необходимо воспользоваться правилом суммирования и формирования переносов (см. табл. 3).

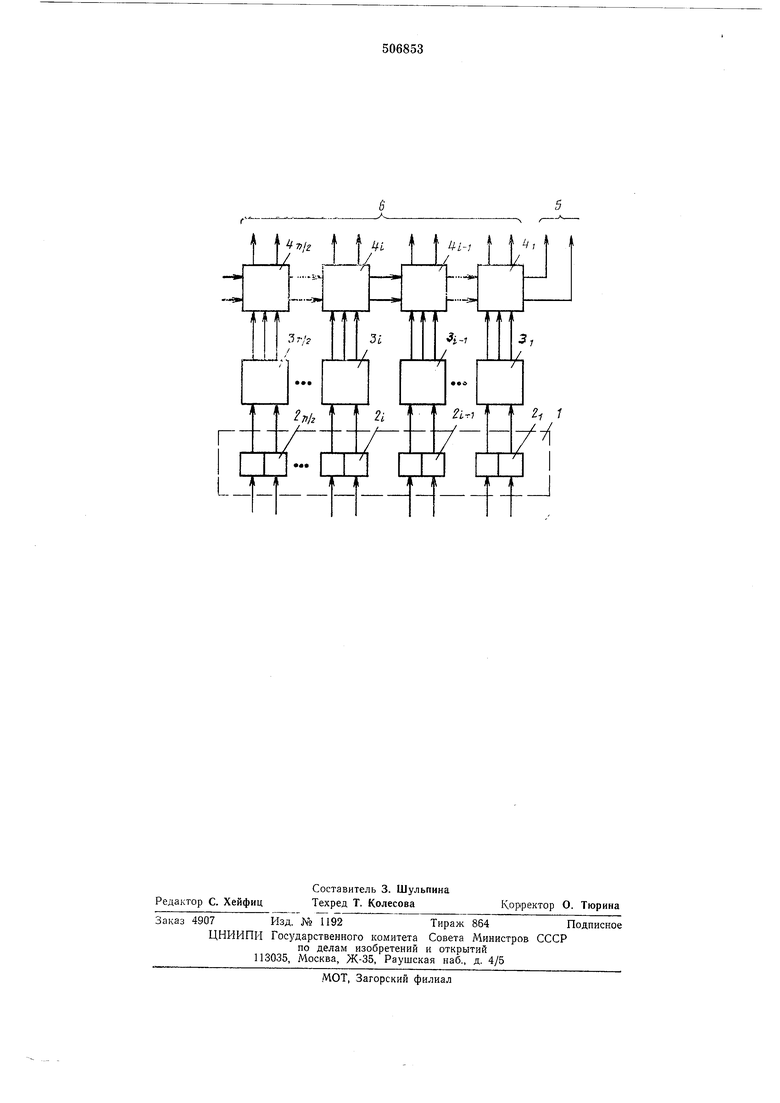

01 10 j 10 00 00 01 - в таолице помечены случаи, когда имеет место перенос в младший разряд суммы целых частей чисел при попарном суммировании «дробных частей частичных частных. На основе данных табл. 1 и приведенного примера можно записать логические функции для нахождения значений двух разрядов частного следующим образом: 421-1 /2.--1+ P2i-2(a;-f &; ),(1) 72i-2 Р21-2а(Ь(+ P2i (b;+ с ,)+ + ; ,(2) а логические функции, с помощью которых находятся значения переносов Р, в виде: Р2,--ИС,.6,+ Prt Р -11- ; 1 + + Р 2/- vC; , P2i-4 , P-2i- Pzi-2Ci + + Pzi-ibf. При этом для синтеза логического блока достаточно воспользоваться выражениями (1) - (4). На варианты построения дещифратора и регистра не налагается никаких ограничений. Таким образом, устройство деления п-разоднотипрядного кода на три состоит изных схем, каждая из которых содержит: 1)двухразрядный регистр делимого; 2)двоичный дешифратор на два входа и три выхода; 3) логический блок, работающий в соответствии с выражениями (1) - (4). Предлагаемое устройство в отличие от известного содержит меньшее число элементов, так как в нем отсутствуют сдвиговый регистр частного, схема синхронизации, память выборок и счетчик циклов, а также вместо сдвигового регистра делимого используется более простой по построению статический регистр делимого. Время выполнения операции деления в предлагаемом устройстве определяется только быстродействием элементов, применяемых в устройстве. Формула изобретения Устройство для деления п-разрядного двоичного кода на три, содержащее регистр делимого, разряды которого разделены на группы по два разряда в каждой группе, дещифраторы и однотипные логические блоки, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, выходы разрядов г-ой группы разрядов регистра делимого соединены с входами г-го дешифратора (где 1 t - ), выходы которого соединены с входами f-ro логического блока, выходы переносов i-ro логического блока соединены с входами (t-1)-го логического блока, выходы переносов первого логического блока соединены с выходными шинами разрядов остатка, выходы разрядов частного логических блоков подключены к выходным шинам частного.

f

A/f

JL/

гт М

Авторы

Даты

1976-03-15—Публикация

1974-03-11—Подача